# LAYOUT-LEVEL CIRCUIT SIZING AND DESIGN-FOR-MANUFACTURABILITY METHODS FOR EMBEDDED PASSIVE RF CIRCUITS

A Dissertation Presented to The Academic Faculty

By

Souvik Mukherjee

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology August 2007

Copyright © 2007 by Souvik Mukherjee

# LAYOUT-LEVEL CIRCUIT SIZING AND DESIGN-FOR-MANUFACTURABILITY METHODS FOR EMBEDDED PASSIVE RF CIRCUITS

### Approved by:

Dr. Madhavan Swaminathan, Advisor Professor, School of ECE Georgia Institute of Technology

Dr. Sung Kyu Lim

Associate Professor, School of ECE

Georgia Institute of Technology

Dr. Andrew Peterson Professor, School of ECE Georgia Institute of Technology Dr. Manos Tentzeris

Associate Professor, School of ECE

Georgia Institute of Technology

Dr. Mervyn Fathianathan Asst. Professor, School of ECE Georgia Institute of Technology

Date Approved: June 2007

### ACKNOWLEDGMENTS

The last five years at Georgia Tech has been the most valuable and cherished experience of my life. During this time, I have been helped and guided by numerous people, without whom this effort would not have been a reality. To pen down the magnitude of appreciation and gratitude, I owe to these people, is an impossible task. This is an effort to acknowledge most of, if not all, the people who helped me shape my career at Georgia Tech.

Firstly, I would like to thank my academic advisor, Professor Madhavan Swaminathan, for his continuous academic insight, valuable discussions, enthusiasm and encouragement. I am forever grateful to him for his guidance during my research. As an advisor, he has guided me in difficult times of my student career, and as a guardian and friend, in my personal life. I shall always remember the way he offered to help me when I first approached him to become a graduate researcher under his guidance. I am indebted to all my reading and oral committee members, Professor Worai Wardi, Professor Sung Kyu Lim, Professor Andrew F. Peterson, Professor Manos Tentzeris, and Professor Mervyn Fathianathan, for sitting through my presentations, providing thesis corrections and giving me excellent technical feedback. I would also like to thank my former advisor Professor Sung Kyu Lim for providing me the opportunity to begin my graduate studies at Georgia Tech. I would like to thank late Prof. John Uyemura for all his help and guidance when I applied for graduate studies at Tech.

I express my sincere gratitude to a lot of people who have helped me in my work. Special thanks to my friends and colleagues, especially Dr.Sidharth Dalmia, Dr.Bhyrav Mutnury, Dr.Erdem Matoglu, Dr.Vinu Govind, Dr.Rohan Mandrekar, Dr.Jifeng Mao and Dr.Jinwoo Choi for their friendship and their guidance in my research. I would also like to thank Mr.Venky Sundaram for helping me with the board fabrication, despite his hectic schedules. My sincere thanks to all the Epsilon

group members for providing me with a family at work, far away from my home and family. The times that I have spent with them, both academic and social, will always be some of the most valuable and cherished days of my life. Thanks go to: Subramanian N. Lalgudi, Krishna Bharath, Wansuk Yun, Tae Hong Kim, Nevin Altunyurt, Prathap Muthana, Abdemanaf Tambawala, KiJin Han, Marie-Solange Milleron, Janani Chandrashekhar, Abhilash Goyal and Pradeep Yadav. In particular, I would like acknowledge the help of Subramanian Lalgudi towards the end of my research work, Krishna during my dissertation writing, and Nevin for helping me immensely with all the correspondences and paperwork when I was out of town. Also, during these years, I was also fortunate to find friends who have helped me immensely in different ways, during my stay at Georgia Tech. Special thanks go to Ganesh, Vidya, Raj, Vishwa, Shalab, Maryam, Soumendu, Vivek, Bhaskar, Winston, Tippi, Jacob, Rajarshi, Mrinmoy, Bevin, Arup and Saikat. I share very good memories with all these people.

I would also like to thank Dr.Amit Bavisi and Mr.Aditya Makharia for their selfless friendship and immense help throughout my stay at Georgia Tech. The days that I have spent with them will always be memorable and irreplaceable in my life.

Finally, I would like to mention the people whose selfless love, blessings, inspiration, guidance and continuing sacrifices have defined my life; my parents Mrs. Shyamali Mukherjee and Mr. Prabir Mukherjee, my sister Jayoti, my brother Sanmoy, my sister-in-laws Papiya and Sanchita, my brother-in-law Rahul, my uncles and aunts, my loving nephew Sashwa, and my newborn and beautiful niece Rai. I would never forget the days when everybody in my family, in spite of all the hardships, would make sure that nothing impedes my studies and opportunities for a better career. I would also like to thank my in-laws Mrs. Kalpana Majumder and Dr. Paritosh Majumder for their love and immense faith in me, and letting me decide on my opportunities abroad, away from home. I derive great strength from the sacrifices of

these people. I would like to pay my tribute and respect to my uncle, Late Prasanta Mukherjee, whose love, inspiration and care was unparalleled. I carry all his memories and words to achieve all my goals in life. I also have received the care and affection of my beloved grandmother, without whose blessings, this effort would not have been successful. Also, a special thanks to the all the other members of the Mukherjee, Ganguly, Chatterjee and Majumder families for all the great times, fun, encouragement, appreciation, love and support. Lastly, but not the least, I would also like to thank my wife Mrs. Moumita Mukherjee, who deserves more praise than I can put down in words. As the best friend, she has loved me, encouraged me, inspired me, and believed in me for years before we got married. As a wife, she has spent more sleepless nights than myself, both at the lab and at home, helping me in everyday work, during the last days of my research. Her love and sacrifice are the some of the biggest gifts in my life.

# TABLE OF CONTENTS

| ACKNO  | OWLE   | DGMENTS                                                        | iv  |

|--------|--------|----------------------------------------------------------------|-----|

| LIST O | F TAE  | BLES                                                           | Х   |

| LIST O | F FIG  | URES                                                           | xii |

| CHAP   | ΓER 1  | INTRODUCTION                                                   | 1   |

| 1.1    | The S  | OP paradigm for RF circuits                                    | 5   |

| 1.2    | Need f | for Layout Scaling Methods in RF Design                        | 8   |

|        | 1.2.1  | Simulation/optimization using circuit solvers                  | 8   |

|        | 1.2.2  | Simulation/optimization using EM solvers                       | 9   |

|        | 1.2.3  | EM-circuit co-simulation                                       | 10  |

|        | 1.2.4  | Circuit augmentation for broadband modeling and circuit tuning | 12  |

| 1.3    | Need f | for DFM (Design-for-Manufacturability) methods in RF design    | 15  |

|        | 1.3.1  | The statistical approach                                       | 16  |

|        |        | 1.3.1.1 Worst case Analysis                                    | 16  |

|        |        | 1.3.1.2 Monte Carlo Analysis                                   | 16  |

|        |        | 1.3.1.3 Design of experiments                                  | 18  |

|        | 1.3.2  | The geometrical approach                                       | 18  |

|        | 1.3.3  | Other conventional methods                                     | 20  |

| 1.4    | Emerg  | ging technologies for SOP applications                         | 21  |

|        | 1.4.1  | LCP-based organic substrate                                    | 21  |

| 1.5    | Compl  | leted Research                                                 | 23  |

| 1.6    | Disser | tation Outline                                                 | 25  |

| CHAP   | ΓER 2  |                                                                |     |

|        |        | BROADBAND MODEL DEVELOPMENT FOR EM-                            |     |

|        |        | BEDDED RF PASSIVES                                             | 26  |

| 2.1    |        | iment with BEMP macromodeling                                  | 29  |

| 2.2    | Exper  | iment with vector fitting                                      | 35  |

| 2.3    | Mathe  | ematical formulation of the augmentation approach              | 40  |

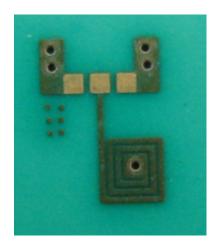

|        | 2.3.1  | Shunt augmentation                                             | 41  |

|        | 2.3.2  | Series augmentation                                            | 45  |

|        | 2.3.3  | Multiple simultaneous augmentation                             | 46  |

| 2.4    | Test c | ases                                                           | 46  |

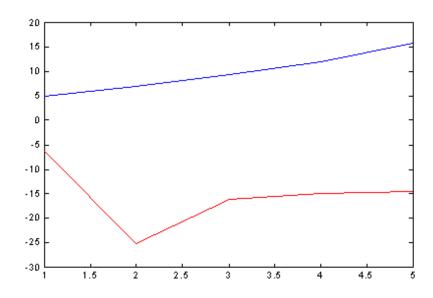

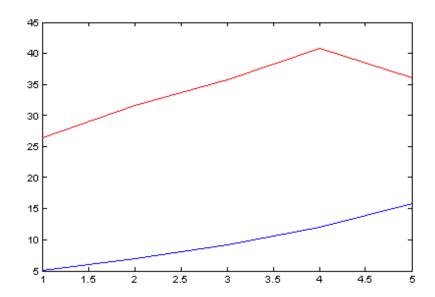

| 2.5    | Summ   | ary                                                            | 55  |

| CHAP | $\Gamma ER 3$ | EFFICIENT DEVELOPMENT OF DESIGN LIBRAR                        | $\mathbf{R}\mathbf{Y}$ |

|------|---------------|---------------------------------------------------------------|------------------------|

|      |               | FOR LAYOUT-LEVEL SIZING OF RF CIRCUITS                        | 56                     |

| 3.1  | Layou         | t-level scaling of RF Circuits: Concept                       | 60                     |

| 3.2  | RF ba         | andpass filters in LCP substrate                              | 61                     |

| 3.3  | Efficie       | ent library development for embedded passives                 | 63                     |

|      | 3.3.1         | Multi-variable nonlinear mapping using ANNs                   | 63                     |

|      | 3.3.2         | Levenberg-Marquadt optimization                               | 65                     |

|      | 3.3.3         | Adaptive data sampling                                        | 69                     |

|      |               | 3.3.3.1 EM modeling of probe-pads and vias                    | 74                     |

|      |               | 3.3.3.2 Adaptive data sampling                                | 75                     |

|      | 3.3.4         | Synthesis and design space exploration                        | 80                     |

| 3.4  | Layou         | t-level sizing of RF bandpass filters                         | 82                     |

|      | 3.4.1         | Lumped circuit modeling                                       | 83                     |

|      | 3.4.2         | Sizing using model mapping                                    | 85                     |

|      | 3.4.3         | Correlation of scaled model with EM simulation                | 92                     |

|      | 3.4.4         | Additional test cases                                         | 92                     |

|      |               | 3.4.4.1 5.5 GHz bandpass filter scaling                       | 93                     |

|      |               | 3.4.4.2 Filter with transmission zeros                        | 96                     |

|      |               | 3.4.4.3 Dual-band filter                                      | 96                     |

| 3.5  | Augm          | entation for model tuning                                     | 99                     |

| 3.6  | Summ          | nary                                                          | 106                    |

|      |               |                                                               |                        |

| CHAP | ΓER 4         |                                                               |                        |

|      |               | OLOGY FOR EMBEDDED RF PASSIVE CIRCUITS                        |                        |

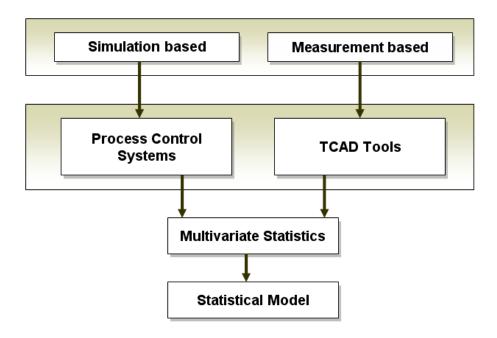

| 4.1  |               | tical design and modeling                                     |                        |

|      | 4.1.1         | Simulation based techniques                                   |                        |

|      | 4.1.2         | Measurement-based techniques                                  | 113                    |

| 4.2  | Perfor        | mance variations in RF bandpass filters                       | 114                    |

| 4.3  | Statist       | tical modeling methodology for embedded RF circuits           | 116                    |

|      | 4.3.1         | Segmented lumped element modeling and simulation              | 117                    |

|      | 4.3.2         | Sensitivity analysis                                          | 119                    |

|      | 4.3.3         | Extraction of probability density functions (pdfs) of perfor- |                        |

|      |               | mance measures                                                | 123                    |

|      | 4.3.4         | Warpage modeling                                              | 129                    |

| 4.4  | Diagno        | osis based on design scaling                                  | 139                    |

|      | 4.4.1         | Filter with transmission zeros                                | 143                    |

| 4.5  | Diagno        | osis based on statistical analysis                            | 146                    |

|        | 4.5.1   | Number of performance measures less than number of physical |               |

|--------|---------|-------------------------------------------------------------|---------------|

|        |         | parameters                                                  | 146           |

|        | 4.5.2   | Number of performance measures more than number of phys-    |               |

|        |         | ical parameters                                             | 149           |

|        |         | 4.5.2.1 Test case: I                                        | 151           |

|        |         | 4.5.2.2 Test case:II                                        | 153           |

| 4.6    | Simula  | tion with non-gaussian parameters                           | 155           |

| 4.7    | Summa   | ary                                                         | 160           |

| СНАРТ  | ER 5    | YIELD OPTIMIZATION OF RF PASSIVE CIRCUIT                    | <b>'S</b> 161 |

| 5.1    | Param   | etric yield                                                 | 164           |

| 5.2    | Yield e | enhancement and optimization                                | 166           |

| 5.3    | Summa   | ary                                                         | 174           |

| СНАРТ  | ER 6    | CONCLUSIONS AND FUTURE WORK                                 | 175           |

| 6.1    | Conclu  | sions                                                       | 176           |

| 6.2    | Future  | work                                                        | 179           |

| 6.3    | Publica | ations and Invention Disclosures                            | 180           |

| APPEN  | DIX A   | CIRCUIT PARTITIONING                                        | 182           |

| APPEN  | DIX E   | B DESIGN GUIDELINES FOR MANUFACTURING IN                    | V             |

|        |         | CURRENT LCP PROCESS                                         | 184           |

|        |         | C VECTOR FITTING BY POLE RELOCATION                         | 186           |

| C.1    | Pole id | lentification                                               | 186           |

| VITA . |         |                                                             | 188           |

| REFER  | ENCE    | S                                                           | 189           |

## LIST OF TABLES

| Table 1  | Correlation between the measured data and neuromodeled data without including the effect of via and CPW pad models                                                                                               | 74    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 2  | Correlation between the measured data and the neuromodeled data after adding the EM models for vias and CPW pads of the spiral inductors                                                                         | 75    |

| Table 3  | Variation in physical parameters for tolerance of 10% in Q                                                                                                                                                       | 77    |

|          |                                                                                                                                                                                                                  |       |

| Table 4  | Variation in physical parameters for a tolerance of $3\%$ in Q $\dots$                                                                                                                                           | 78    |

| Table 5  | Variation in the physical parameters for a 3% tolerance in Q and L                                                                                                                                               | 78    |

| Table 6  | Synthesis results for a 12.5 nH (@2.4GHz) spiral inductor exhibiting Q, area and SRF tradeoffs (for a line spacing of 0.1 mm; 1mm=40 mils)                                                                       | 81    |

| Table 7  | Comparison of the component values for three scaling test cases based on 2.45 GHz reference layout; correlation of EM simulation (Full-wave) data with the data obtained from the polynomial mapped model (poly) | 88    |

| Table 8  | Comparison of component values for three scaling test cases; between polynomial mapped model (poly) and full-wave EM simulation (full-wave)                                                                      | 95    |

| Table 9  | Array showing the fractional factorial plan                                                                                                                                                                      | 120   |

| Table 10 | Variations(unit:mils) in the physical parameters in the synthesized filters, to exhibit similar frequency response as the fabricated prototype: Test case 1                                                      | 142   |

| Table 11 | Variations(unit:mils) in the physical parameters in the synthesized filters, to exhibit similar frequency response as the fabricated prototype: Test case 2                                                      | 145   |

| Table 12 | Statistical parameters of the filter performance metrics: Test case I                                                                                                                                            | 150   |

| Table 13 | Comparison of the diagnosis results with measured variations: Case l                                                                                                                                             | [ 152 |

| Table 14 | Comparison of the diagnosis results with measured variations: Case I                                                                                                                                             | I153  |

| Table 15 | Comparison of the diagnosis results with measured variations: Case III                                                                                                                                           | 153   |

| Table 16 | Statistical parameters of the filter performance metrics: Test case II                                                                                                                                           | 154   |

| Table 17 | Comparison of the diagnosis results with measured variations             | 155  |

|----------|--------------------------------------------------------------------------|------|

| Table 18 | Test case I: Performance measures before and after convex optimization   | ı173 |

| Table 19 | Test case II: Performance measures before and after convex optimization  | 173  |

| Table 20 | Test case III: Performance measures before and after convex optimization | 174  |

## LIST OF FIGURES

| Figure 1  | Conceptual representation of an SOP module                                                                   | 2  |

|-----------|--------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | Limitations in the design flow for RF circuits                                                               | 3  |

| Figure 3  | Layout of a bandpass filter in SONNET EM solver                                                              | 3  |

| Figure 4  | Return loss (S11) variations of an RF bandpass filter                                                        | 7  |

| Figure 5  | Design stages of an RF circuit                                                                               | 7  |

| Figure 6  | Illustration of the concept of space mapping                                                                 | 11 |

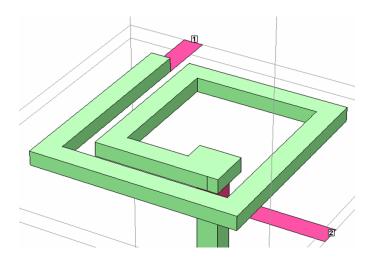

| Figure 7  | SONNET model of a spiral inductor in multi-layer substrate                                                   | 12 |

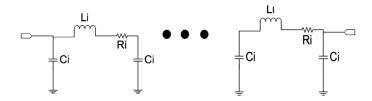

| Figure 8  | Lumped element model of an inductor in LCP substrate                                                         | 13 |

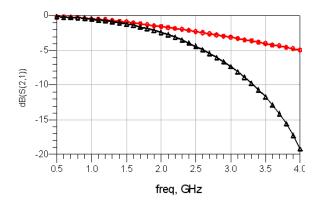

| Figure 9  | Inductor S-parameters                                                                                        | 13 |

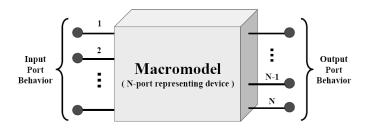

| Figure 10 | Black-box macromodel for an N-port device                                                                    | 14 |

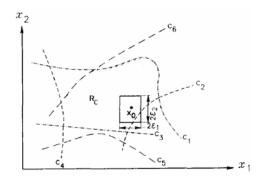

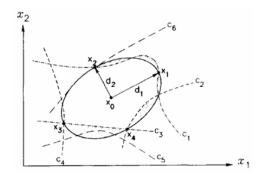

| Figure 11 | Ellipsoidal approximation of feasible design constraint region                                               | 19 |

| Figure 12 | Copper cladded flexible sheet of LCP material                                                                | 22 |

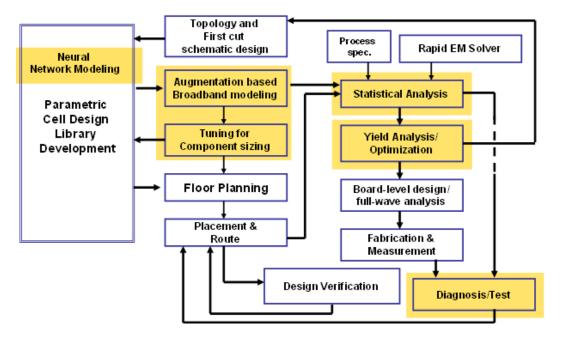

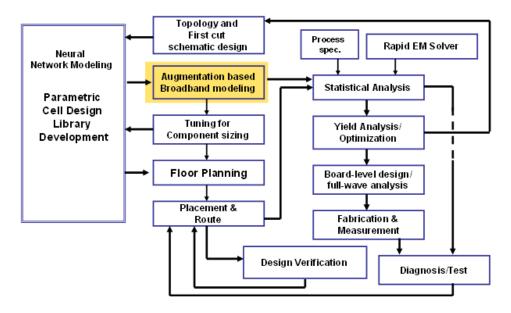

| Figure 13 | RF Design flow; the shaded box represents the focus of this chapter.                                         | 27 |

| Figure 14 | Comparison with recent approaches to broad-band curve-fitting and parameterization                           | 28 |

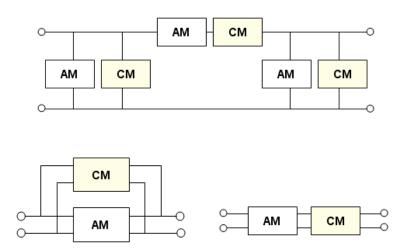

| Figure 15 | Different topologies for circuit augmentation                                                                | 30 |

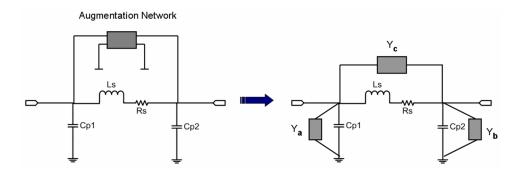

| Figure 16 | Shunt augmentation and its equivalent $\Pi$ -model connection                                                | 30 |

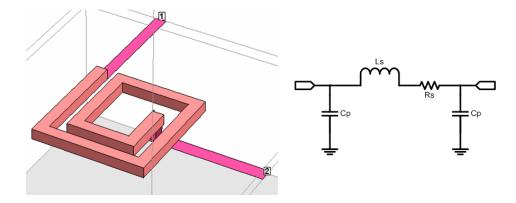

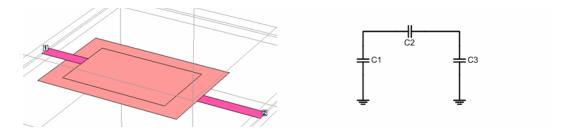

| Figure 17 | (Left):Layout of a spiral inductor in SONNET; (Right): Two-port lumped element model for the inductor        | 32 |

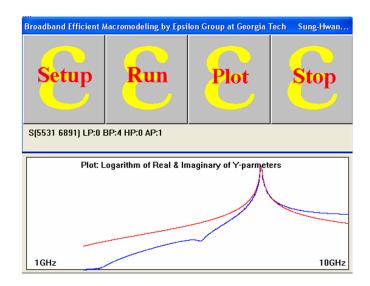

| Figure 18 | Results obtained from the BEMP macromodeling tool                                                            | 32 |

| Figure 19 | A portion of the SPICE netlist, generated by the BEMP macromodeling tool                                     | 33 |

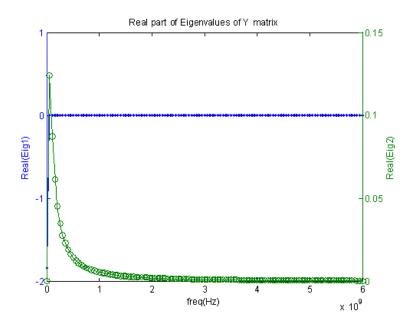

| Figure 20 | Real portion of the eigenvalues of the augmentation matrix                                                   | 34 |

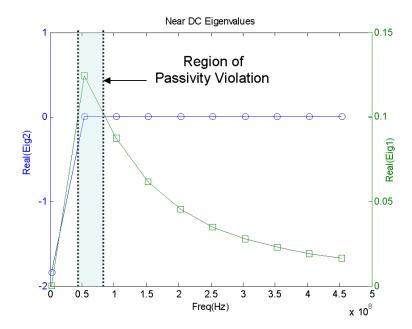

| Figure 21 | Violation of passivity (due to the positive eigenvalues) at near-DC frequencies, by the augmentation network | 35 |

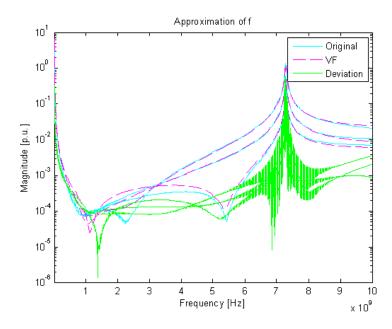

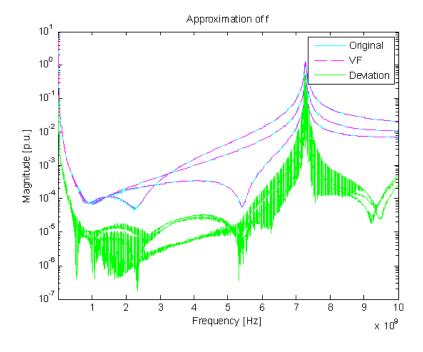

| Figure 22 | Magnitude correlation for $Y_a$ , $Y_b$ , and $Y_c$ , between the difference of circuit-EM parameters, and that obtained from vector fitting (model order = 6) |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

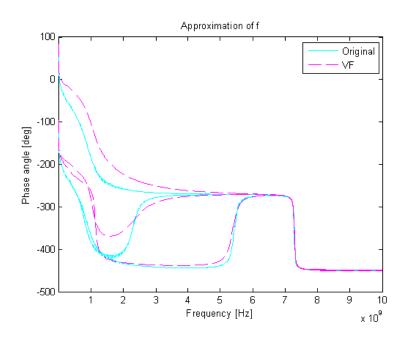

| Figure 23 | Phase correlation for $Y_a$ , $Y_b$ , and $Y_c$ between the difference of circuit-EM parameters, and that obtained from vector fitting (model order = 6)       |

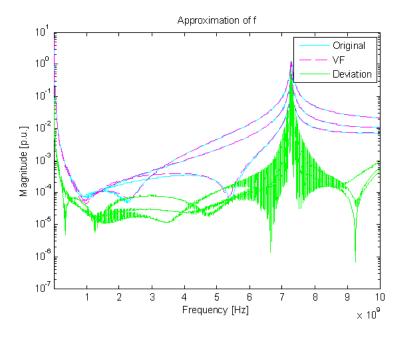

| Figure 24 | Magnitude correlation for $Y_a$ , $Y_b$ , and $Y_c$ between the difference of circuit-EM parameters, and that obtained from vector fitting (model order = 15)  |

| Figure 25 | Phase correlation for $Y_a$ , $Y_b$ , and $Y_c$ between the difference of circuit-EM parameters, and that obtained from vector fitting (model order = 15)      |

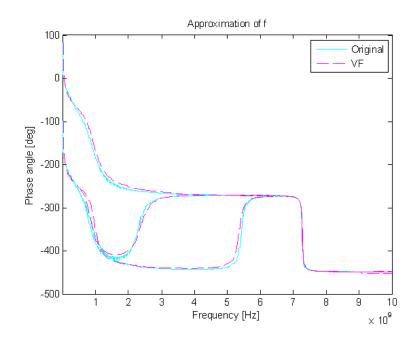

| Figure 26 | Magnitude correlation for $Y_a$ , $Y_b$ , and $Y_c$ between the difference of circuit-EM parameters, and that obtained from vector fitting (model order = 30)  |

| Figure 27 | Phase correlation for $Y_a$ , $Y_b$ , and $Y_c$ between the difference of circuit-EM parameters, and that obtained from vector fitting (model order = 30)      |

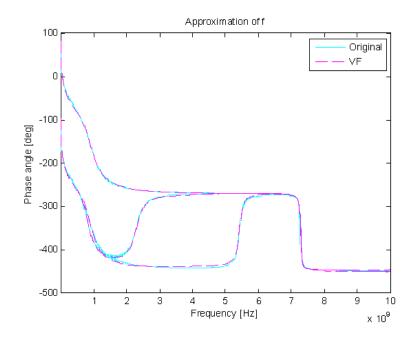

| Figure 28 | Graphical illustration of the node numbering technique, implemented in the series augmentation methodology                                                     |

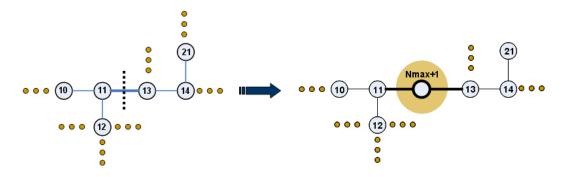

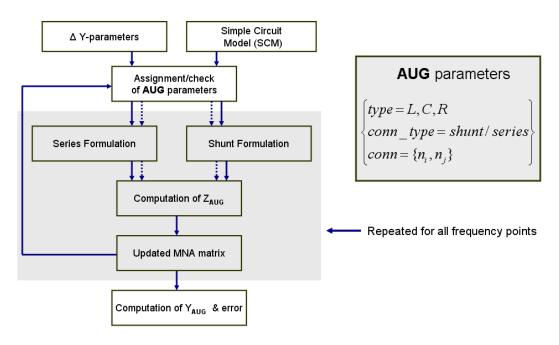

| Figure 29 | Flowchart for series and shunt augmentation                                                                                                                    |

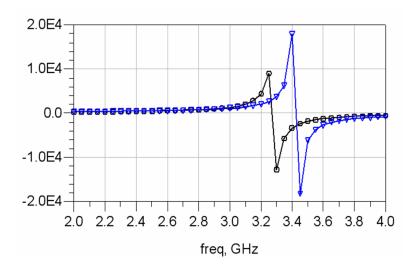

| Figure 30 | Comparison of the Z11-parameters of the EM simulation data with the unaugmented circuit model (S-LCM) of the inductor                                          |

| Figure 31 | Comparison of the Z11-parameters of the augmented circuit model with the EM simulation data                                                                    |

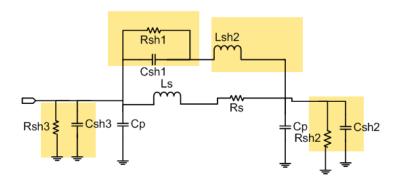

| Figure 32 | Augmented model of the spiral inductor; the augmentation elements are represented by the shaded boxes                                                          |

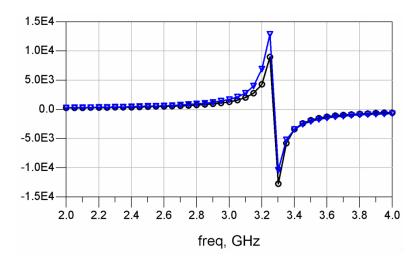

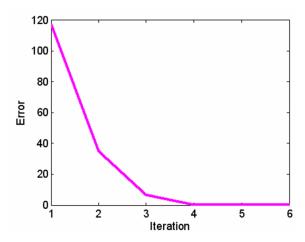

| Figure 33 | Augmentation error as a function of the number of iterations                                                                                                   |

| Figure 34 | Layout of a planar capacitor (in SONNET)                                                                                                                       |

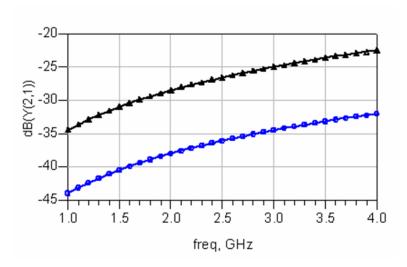

| Figure 35 | Comparison of the Y-parameters of the S-LCM of the capacitor, and that obtained from the EM simulation                                                         |

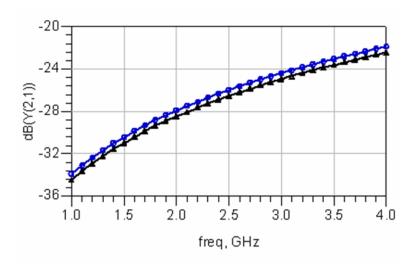

| Figure 36 | Comparison of the Y-parameters of the augmented model of the capacitor, and that obtained from the EM simulation                                               |

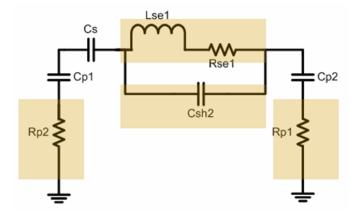

| Figure 37 | resented by the shaded boxes                                                                                                                               | 50 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

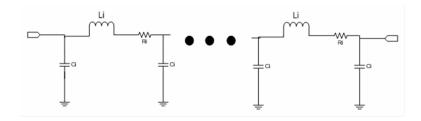

| Figure 38 | Multi-section model for the embedded RF inductor                                                                                                           | 51 |

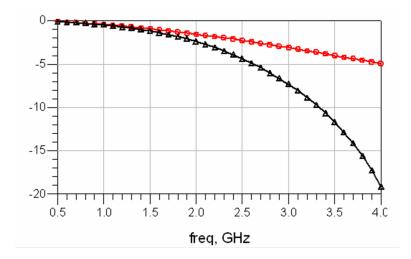

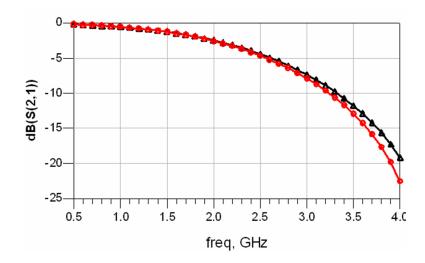

| Figure 39 | Comparison of the S-parameters of the S-LCM (circle) and that obtained from the EM solver (triangle)                                                       | 51 |

| Figure 40 | Correlation between the S-parameters of the augmented model (circle) and that obtained from the EM solver (triangle)                                       | 52 |

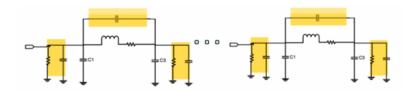

| Figure 41 | Multi-section augmented model for the embedded RF inductor; the shaded boxes represent the sections augmented to the core S-LCM.                           | 52 |

| Figure 42 | Comparison of the Y-parameters of the EM simulation data (data symbol:square) with the simple circuit model (S-LCM) of the inductor (data symbol:traingle) | 53 |

| Figure 43 | Comparison of the Y-parameters of the augmented circuit model (data symbol:circle) with the EM simulation data (data symbol:square).                       | 54 |

| Figure 44 | Augmented model of the spiral inductor; the augmentation elements are represented by the "dotted" boxes                                                    | 54 |

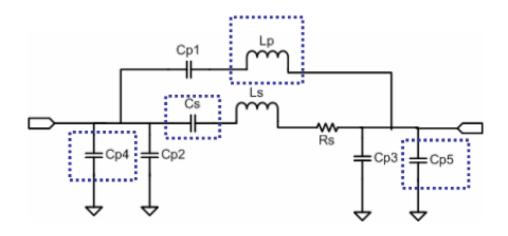

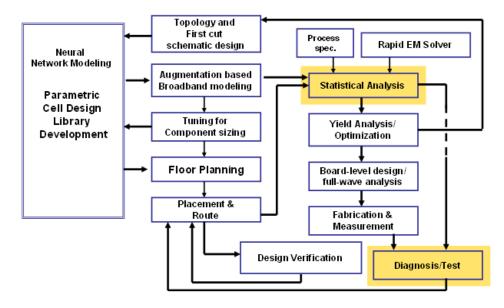

| Figure 45 | RF design flowchart                                                                                                                                        | 57 |

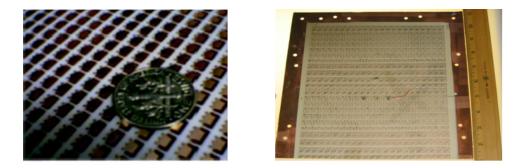

| Figure 46 | Fabricated RF front-end blocks in LCP-based substrates                                                                                                     | 58 |

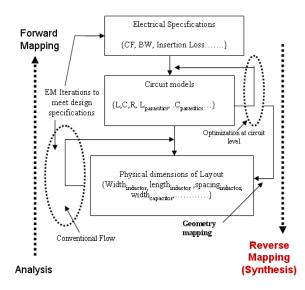

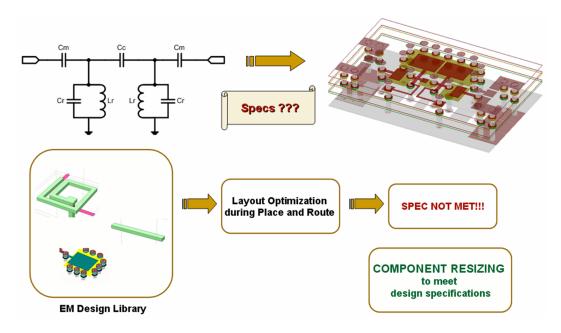

| Figure 47 | Flowchart of conventional RF design and RF design scaling                                                                                                  | 61 |

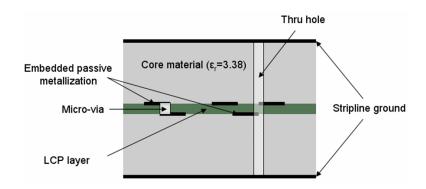

| Figure 48 | Cross-section of the dielectric stackup for the stripline configuration.                                                                                   | 62 |

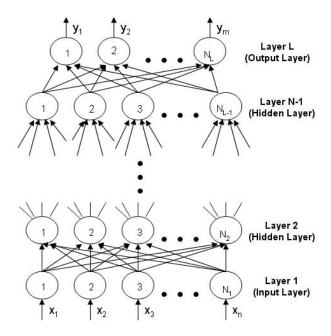

| Figure 49 | Multi-layer perceptron-based neural network structure                                                                                                      | 64 |

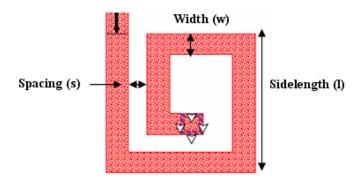

| Figure 50 | Layout of a spiral inductor in SONNET, depicting the different physical parameters                                                                         | 68 |

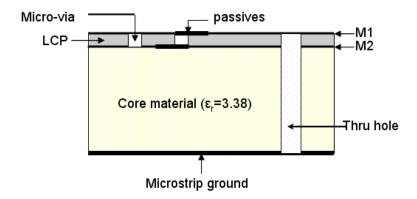

| Figure 51 | Cross-section used for the design of microstrip spiral inductors. $$ . $$ .                                                                                | 68 |

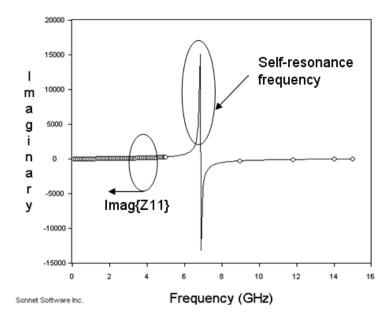

| Figure 52 | Depiction of the self-resonance frequency (SRF) of an inductor. $$ . $$                                                                                    | 69 |

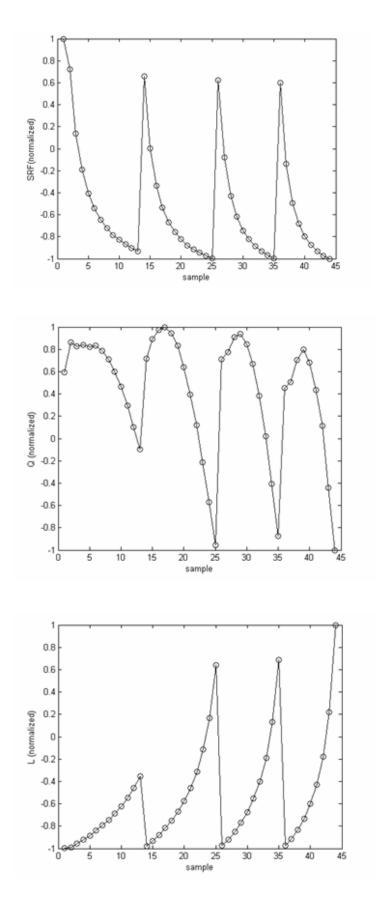

| Figure 53 | Correlation between modeled data and test data during forward mapping; (Top)-Inductance mapping, (Middle)-Quality factor mapping, and (Bottom)-SRF mapping | 71 |

| Figure 54 | Correlation between the test data and the neuromodeled data (using MATLAB's TrainLM ANN model)                                                             | 73 |

| Figure 55 | Photograph of the fabricated microstrip loop inductors                                                                                                     | 74 |

| Figure 56 | SONNET-based EM model for the CPW pads and thruhole vias for the microstrip inductor                                                                                                                                                                                              | 75 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

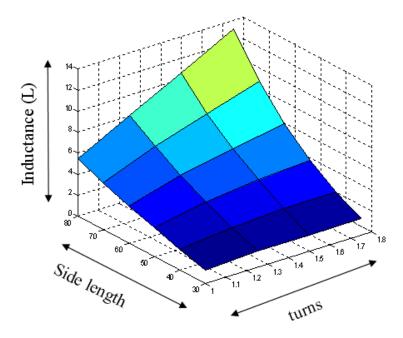

| Figure 57 | Response surface for the inductance(L) of the microstrip inductors.                                                                                                                                                                                                               | 76 |

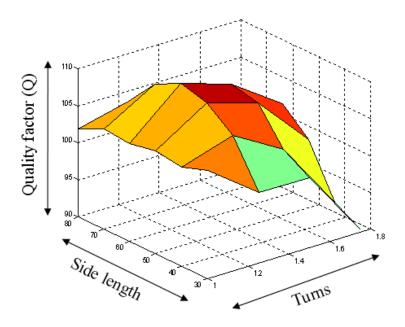

| Figure 58 | Response surface of the quality factor(Q) of the microstrip inductors.                                                                                                                                                                                                            | 77 |

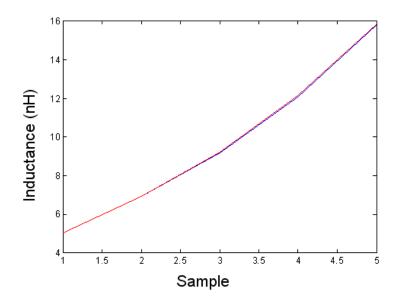

| Figure 59 | ANN-model to EM data correlation using interpolation for test data (same as that used in Figure 54); Red graph is the TrainLM output for test data and Blue graph is the EM simulation result for test data. X- Axis is the test sample number; made continuous by interpolation. | 79 |

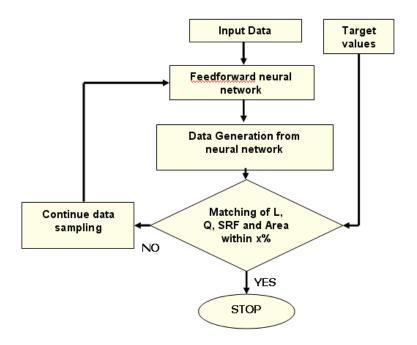

| Figure 60 | Flowchart for the adaptive data sampling algorithm                                                                                                                                                                                                                                | 79 |

| Figure 61 | Algorithm for design space exploration                                                                                                                                                                                                                                            | 81 |

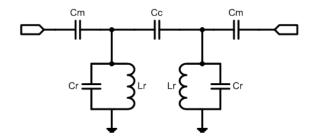

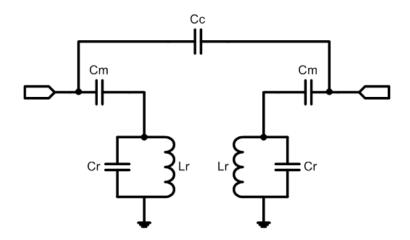

| Figure 62 | Ideal schematic for a second-order capacitively coupled bandpass filter.                                                                                                                                                                                                          | 82 |

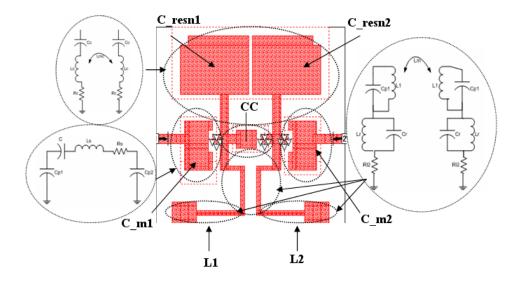

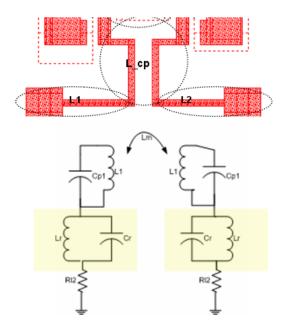

| Figure 63 | Lumped element modeling for segemented sections of the bandpass filter shown in Figure 62                                                                                                                                                                                         | 83 |

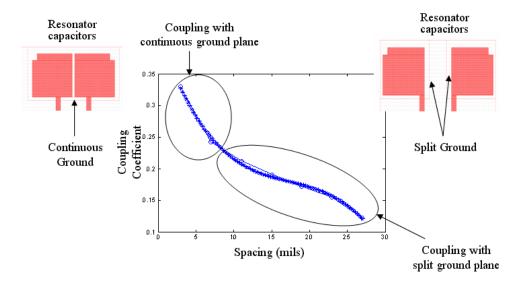

| Figure 64 | Mapping of reference ground plane of the resonator capacitors; separate polynomial functions are used for split and continuous ground plane coupling                                                                                                                              | 85 |

| Figure 65 | Extraction of segmented layout parameters from optimized lumped circuit models                                                                                                                                                                                                    | 89 |

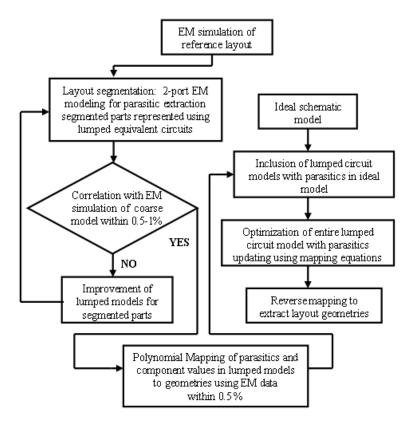

| Figure 66 | Flowchart for optimization and layout-level sizing methodology                                                                                                                                                                                                                    | 90 |

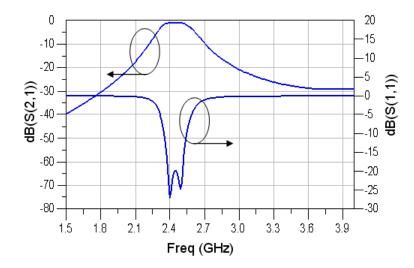

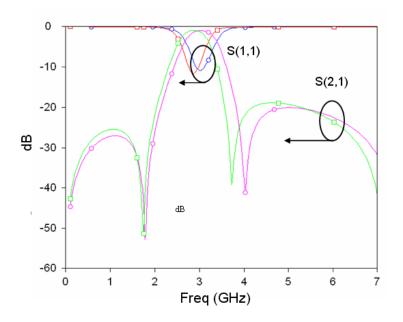

| Figure 67 | S-parameters of the reference design (2.45 GHz bandpass filter)                                                                                                                                                                                                                   | 90 |

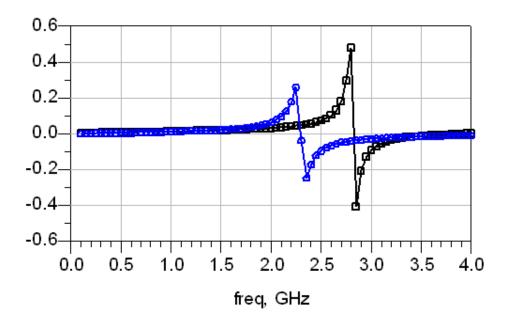

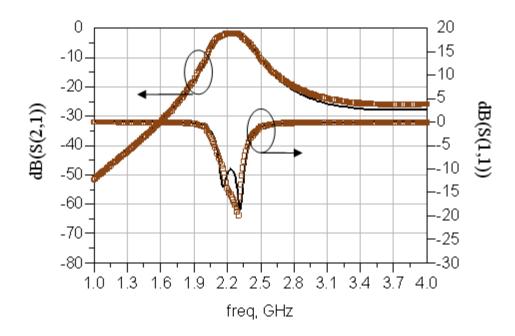

| Figure 68 | Correlation between full-wave data (sampled) and data from scaling methodology (solid) for a 2.2 GHz RF bandpass filter                                                                                                                                                           | 91 |

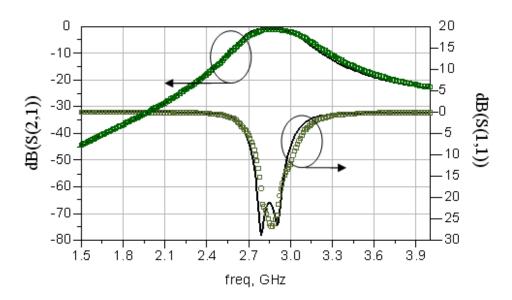

| Figure 69 | Correlation between full-wave data (sampled) and data from scaling methodology (solid) for a 2.8 GHz RF bandpass filter                                                                                                                                                           | 91 |

| Figure 70 | Layout of a second order, capacitively coupled 5.5 GHz bandpass filter in SONNET                                                                                                                                                                                                  | 93 |

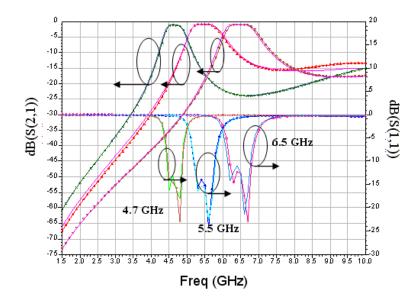

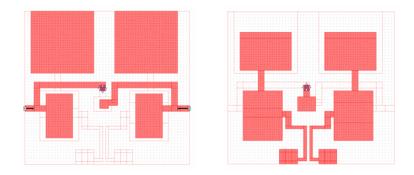

| Figure 71 | Correlation between full-wave data (triangular) and data from scaling (solid) for filters centered at 4.7 and 6.5 GHz based on coarse data of 5.5 GHz filter, shown in the middle                                                                                                 | 94 |

| Figure 72 | Ideal circuit schematic of the inductively coupled resonator filter                                                                                                                                                                                                               | 95 |

| Figure 73 | Layout of the filter (with transmission zeros) in multi-layer LCP-based substrate; (Top)-top plane, and (Bottom)- bottom plane of the filter structure.                                                                                                                           | 95 |

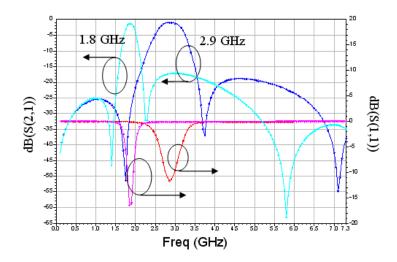

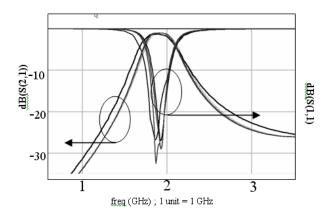

| Figure 74 | S-parameters of the reference and scaled filters; cyan represents the reference design (1.8 GHz) and blue represents the scaled design(2.9 GHz)                                                                                                                                                  | 97         |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

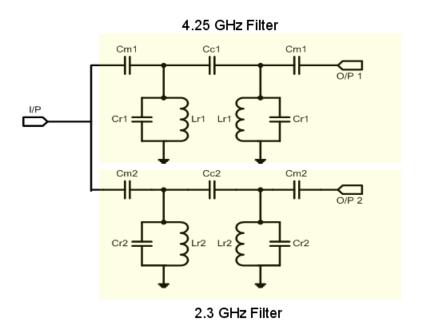

| Figure 75 | Ideal schematic of the 2.3 GHz and 4.25 GHz dual-band filter                                                                                                                                                                                                                                     | 97         |

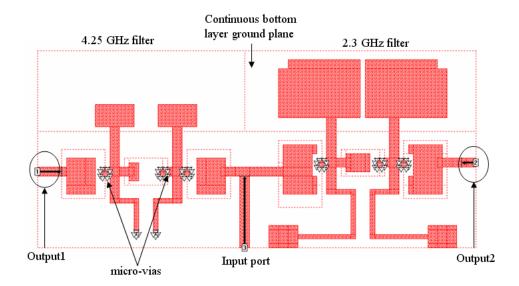

| Figure 76 | Layout of the 2.3 GHz and 4.25 GHz dual-band filter                                                                                                                                                                                                                                              | 98         |

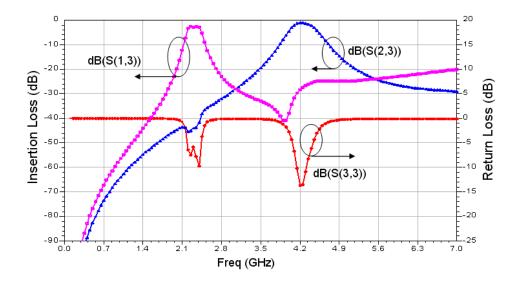

| Figure 77 | S-parameters of the dualband filter                                                                                                                                                                                                                                                              | 99         |

| Figure 78 | High-level description for the tuning requirement in RF circuits                                                                                                                                                                                                                                 | 100        |

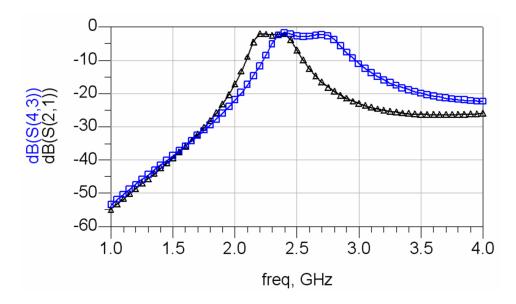

| Figure 79 | Comparison of the S-parameters obtained from the connected broadband model (data symbol:square), and that obtained from the EM simulation of the complete filter layout in SONNET (data symbol:traingle)                                                                                         | 101        |

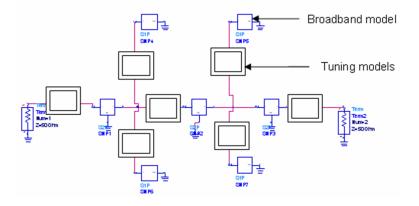

| Figure 80 | Simulation setup for the tuning of the bandpass filter                                                                                                                                                                                                                                           | 101        |

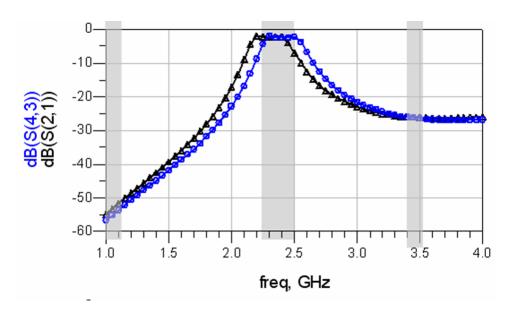

| Figure 81 | Comparison of the S-parameters obtained from the tunable broadband model, and that obtained from the EM simulation of the complete filter layout in SONNET; the frequency points where the specifications need to be satisfied are shaded in gray                                                | 102        |

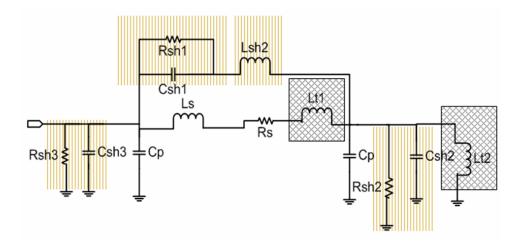

| Figure 82 | Tuned broadband model of the spiral inductor; the elements added during broadband modeling is shown by vertical-lined boxes, and the tuning elements have been shown by the hatch-lined boxes;Lsh2=6.8 nH, Csh1=1.2 pF, Rsh1=2.6 ohm, Csh2=Csh3=0.22 pF, Rsh2=Rsh3=ohm, Lt1=0.43 nH, Lt2=4.45 nH | -44<br>103 |

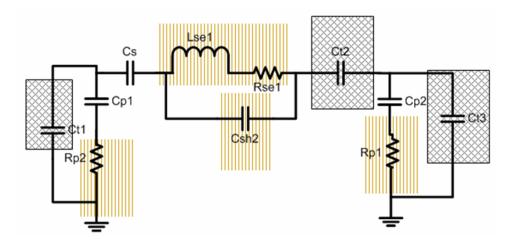

| Figure 83 | Tuned broadband model of the planar resonator capacitor; the elements added during broadband modeling is shown by vertical-lined boxes, and the tuning elements have been shown by the hatch-lined boxes; Lse1=0.4 nH, Rse1=1.2 ohm, Rp1=Rp2=4.6 ohm, Ct2=5.87 pF, Ct1=Ct3=0.78 pF               | 103        |

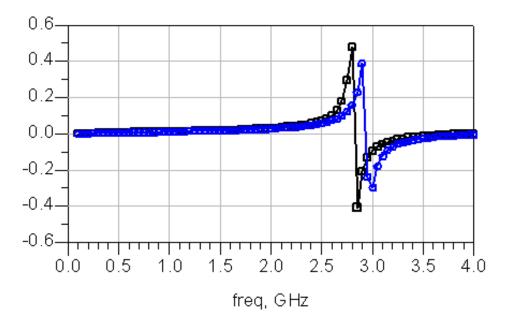

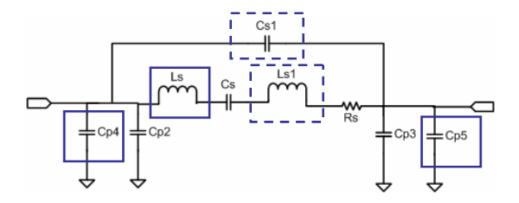

| Figure 84 | Tuned broadband model of the planar matching capacitors; the elements added during broadband modeling is shown by solid-lined boxes, and the tuning elements have been shown by the dotted-lined boxes; Cs1=0.49 pF, Ls=0.65 nH, Rs=2.3 ohm, Ls1=0.22 nH, Cp4=Cp5=0.85 pF                        | 104        |

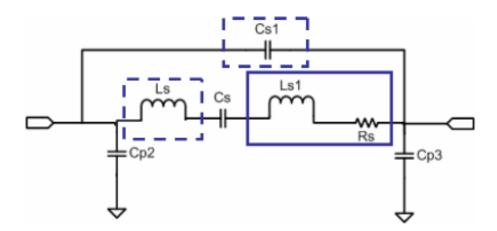

| Figure 85 | Tuned broadband model of the planar center capacitor; the elements added during broadband modeling is shown by solid-lined boxes, and the tuning elements have been shown by the dotted-lined boxes; Cs1=0.13 pF, Ls=0.2 nH, Ls1=0.31 nH, Rs=4.4 ohm                                             | 104        |

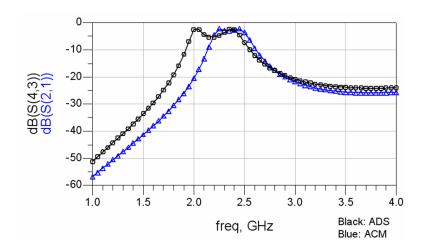

| Figure 8 | 86  | Comparison of the S21-parameters obtained from the augmentation-based technique (corresponds to the response that is shifted to the right) and that obtained from nonlinear, multi-variable optimization using ADS (corresponds to the response that is shifted to the left). | 105  |

|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 8 | 87  | Comparison of the S21-parameters obtained from the augmentation-based technique (triangle) and that obtained from nonlinear, multivariable optimization using ADS (circle)                                                                                                    | 105  |

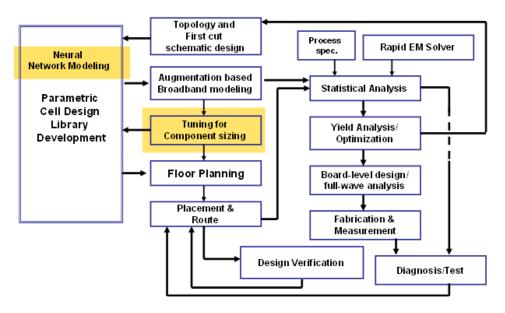

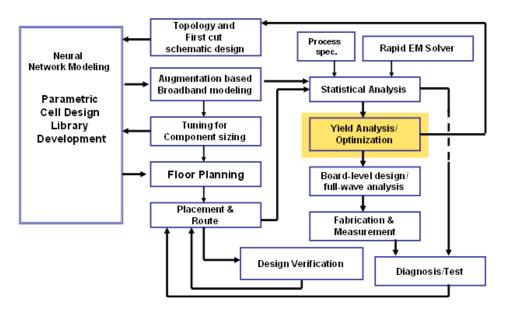

| Figure 8 |     | Focus of Chapter IV (shaded) in the perspective of an RF CAD framework                                                                                                                                                                                                        | 108  |

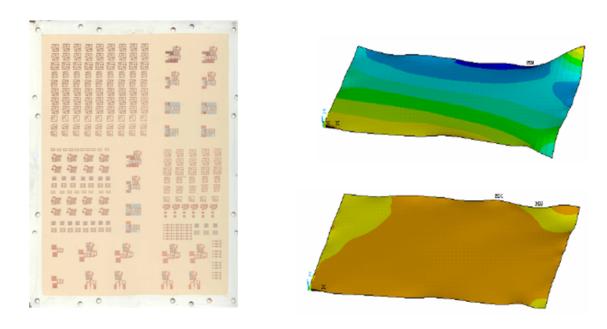

| Figure 8 | 89  | (Left) Visual comparison of the filter size and (right)photograph of an LCP panel                                                                                                                                                                                             | 108  |

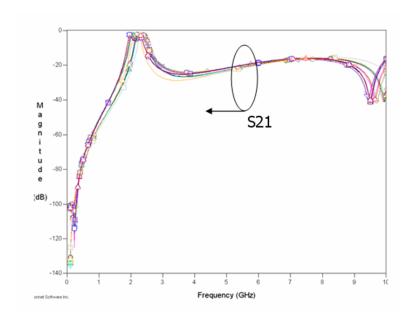

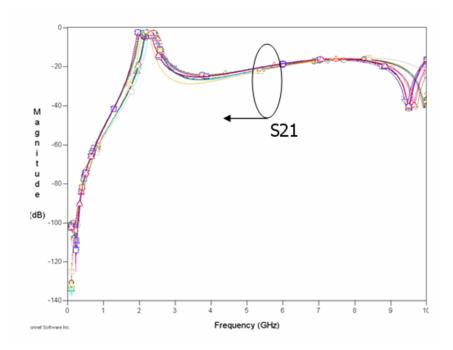

| Figure 9 | 90  | Measurement results of insertion loss (S21) for the fabricated filters.                                                                                                                                                                                                       | 109  |

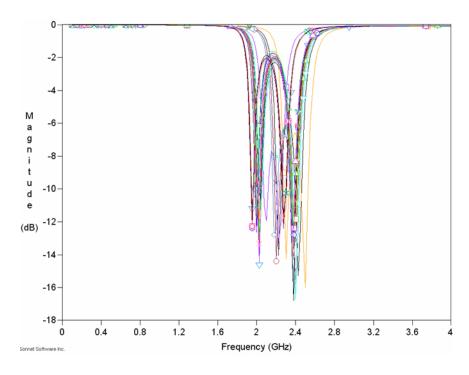

| Figure 9 | 91  | Return loss (S11) variations of an RF bandpass filter                                                                                                                                                                                                                         | 109  |

| Figure 9 | 92  | High-level methodology for statistical design                                                                                                                                                                                                                                 | 112  |

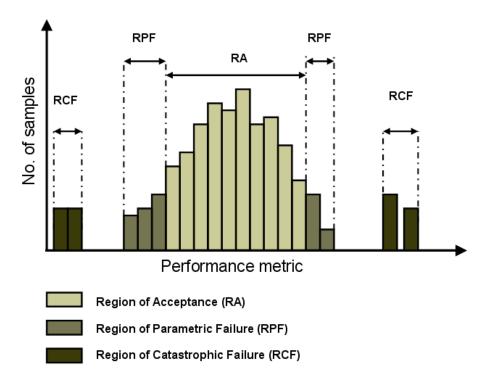

| Figure 9 | 93  | Statistical distribution of a performance metric, illustrating the region of acceptance, the region of parametric failure, and the region of catastrophic failure.                                                                                                            | 113  |

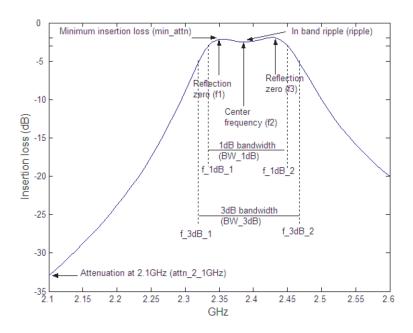

| Figure 9 | 94  | Typical variation of a performance metric (S21) for a bandpass filter for wireless applications                                                                                                                                                                               | 114  |

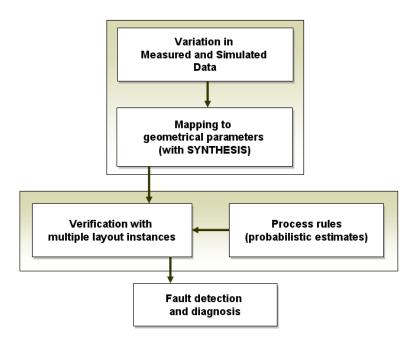

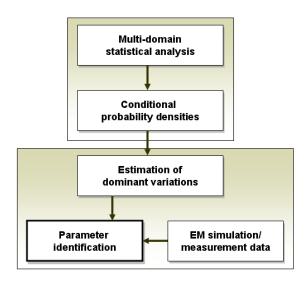

| Figure 9 | 95  | Flowchart of the statistical modeling and diagnosis methodology                                                                                                                                                                                                               | 116  |

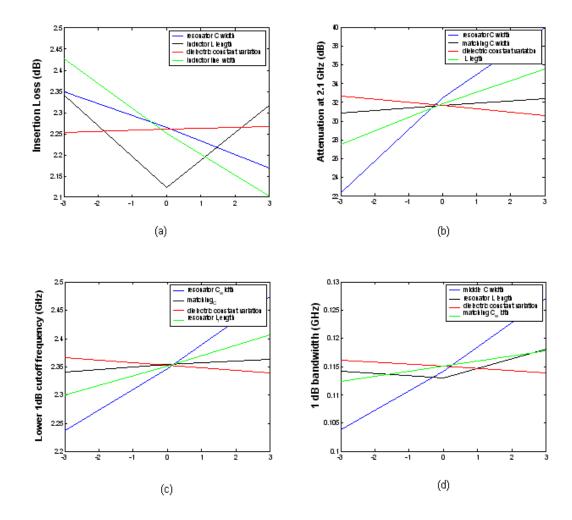

| Figure 9 | 96  | Sensitivity analysis of the performance measures of the bandpass filter                                                                                                                                                                                                       | r121 |

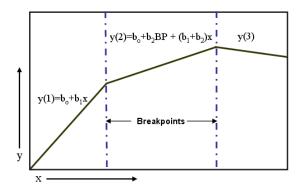

| Figure 9 | 97  | Piecewise linear function approximation for the estimation of weakly nonlinear sensitivities                                                                                                                                                                                  | 124  |

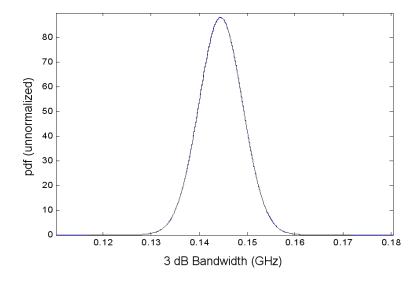

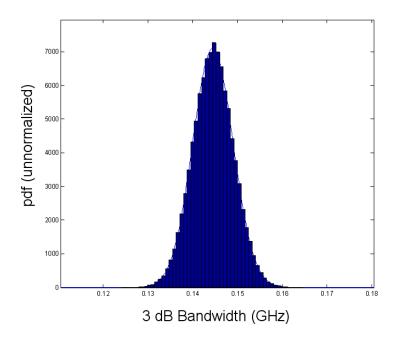

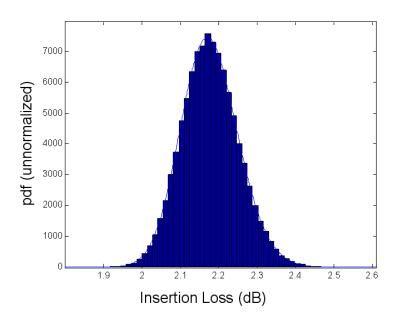

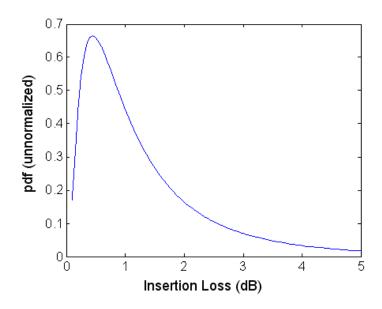

| Figure 9 | 98  | Probability density function for the 3 dB bandwidth                                                                                                                                                                                                                           | 126  |

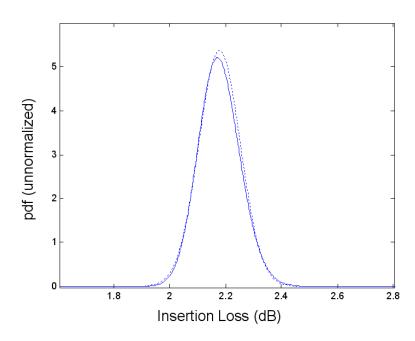

| Figure 9 | 99  | Comparison of probability density functions for minimum attenuation using convolution methodology(solid line) and normal approximation (dotted line)                                                                                                                          | 127  |

| Figure 1 | 100 | Comparison of probability distribution of 3dB bandwidth; Convolution (solid line) and random instances (histogram)                                                                                                                                                            | 127  |

| Figure 1 | 101 | Comparison of probability distribution of insertion loss (S21); Convolution (solid line) and random instances (histogram)                                                                                                                                                     | 128  |

| Figure 1 |     | (Left) Photograph of a 12in × 9in LCP-based panel; (Right) Pictorial representation of the board warpage (figure not to scale)                                                                                                                                                | 129  |

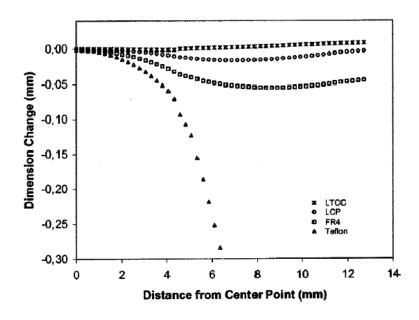

| Figure 103 Out-of-plane displacement as a function of the distance from the center of the board; multiple plots correspond to different board-                |      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| level RF packaging substrates                                                                                                                                 | 130  |

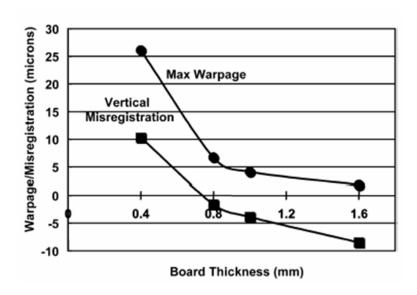

| Figure 104 Board warpage as a function of board thickness                                                                                                     | 130  |

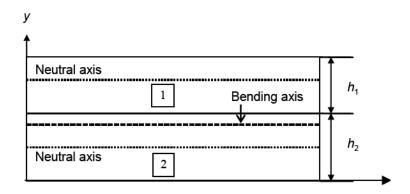

| Figure 105 Two-plate model for the analytical calculation of board warpage. $$ .                                                                              | 132  |

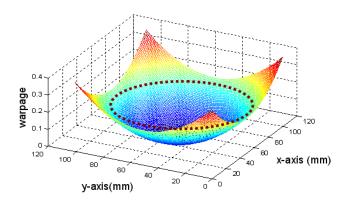

| Figure 106 Board warpage distribution as a function of the distance from the center of the board (point of support during the thermal cycle. $$               | 134  |

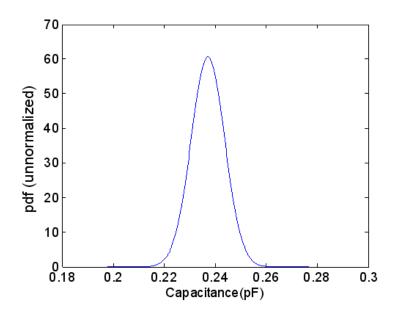

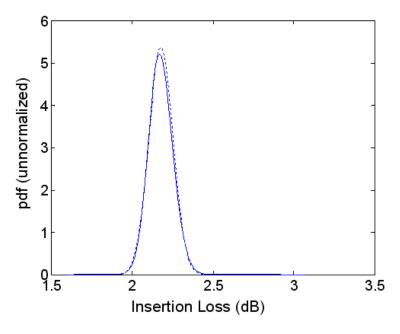

| Figure 107 Probability density function of the capacitance for a capacitor after including the effect of warpage                                              | 136  |

| Figure 108 Probability density function of the insertion loss (S21) after including the effect of warpage                                                     | 136  |

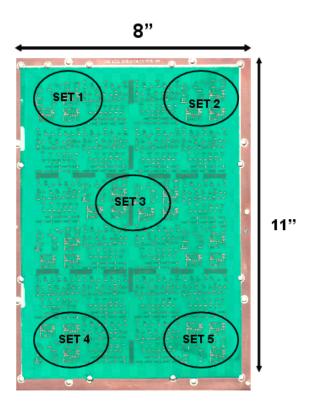

| Figure 109 Fabricated panel of bandpass filters; The circles indicate different sets of filters distributed across the board to study performance variability | 137  |

| Figure 110 Measurement results of return loss (S11) for the fabricated filters                                                                                | 137  |

| Figure 111 Measurement results of return loss (S11) for the fabricated filters                                                                                | 138  |

| Figure 112 Mean deviation of the measured results, from the design specifications, for different coupons                                                      | 138  |

| Figure 113 Model-to-hardware correlation for average deviation of S11 from measurements and the simulations (shown for coupon 1 and 3                         | 139  |

| Figure 114 High-level methodology for the prototype diagnosis                                                                                                 | 140  |

| Figure 115 Results of diagnosis of a bandpass filter: Test case 1                                                                                             | 142  |

| Figure 116 Prototype diagnosis for test case II; A second order bandpass filter with transmission zeros                                                       | 144  |

| Figure 117 S-parameters for the faulty design(green) and the correct design(pink)                                                                             | .145 |

| Figure 118 High-level flow for statistical diagnosis                                                                                                          | 147  |

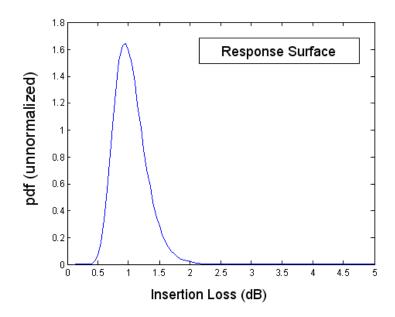

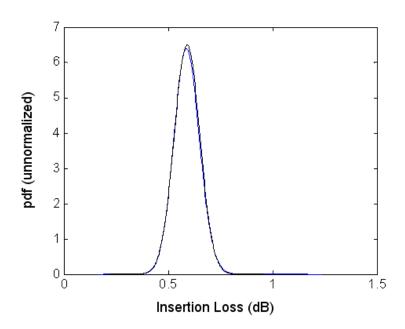

| Figure 119 Probability density function of the Insertion Loss using the response surface methodology                                                          | 157  |

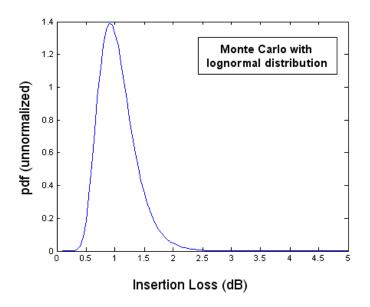

| Figure 120 Probability density function of the Insertion Loss using Monte Carlo simulations in ADS with non-gaussian parameters                               | 157  |

| Figure 121 Lognormal distribution of the Insertion Loss                                                                                                       | 159  |

| Figure | 122 Probability density function of the Insertion Loss after conversion from the lognormal distribution to the gaussian distribution 15                                                                                 | 59         |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure | 23 Focus of Chapter V (shaded) in the perspective of an RF CAD framework                                                                                                                                                | 62         |

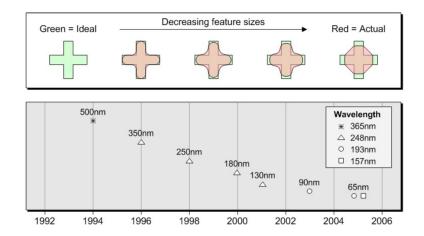

| Figure | 24 Effect of feature shrinkage on IC interconnect manufacturability 16                                                                                                                                                  | $\hat{0}2$ |

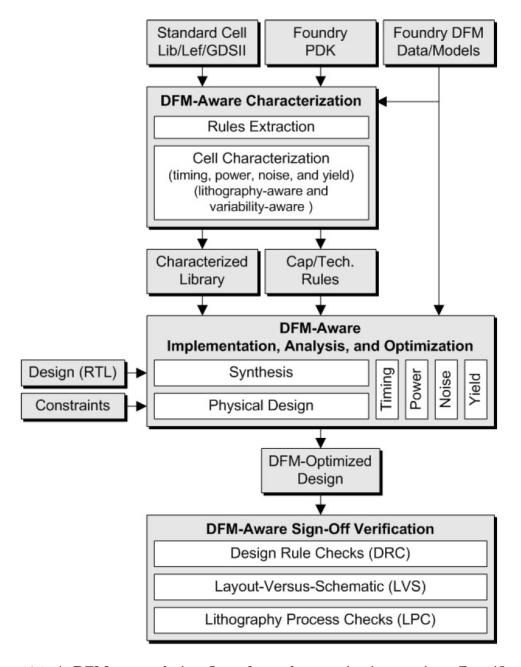

| Figure | 25 A DFM-aware design flow; from characterization to sign-off verification (Courtesy: Magma Design Automation, Inc.)                                                                                                    | 63         |

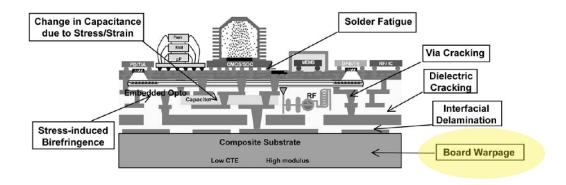

| Figure | 26 Potential failure mechanisms demonstrated on a conceptual SOP module                                                                                                                                                 | 64         |

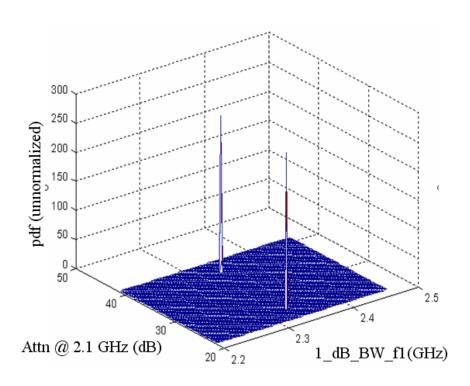

| Figure | 27 Distribution of design acceptability function using simultaneous constraints on Attenuation @ 2.1 GHz and lower-cutoff frequency of 1 dB bandwidth: isolated spikes indicate that such constraints lead to low yield | 67         |

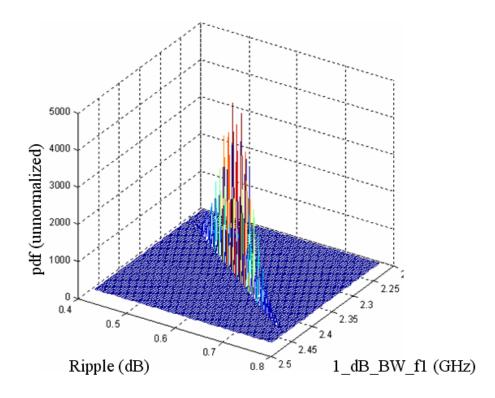

| Figure | 28 Computation of design acceptability function using simultaneous constraints on inband ripple and lower-cutoff frequency of 1 dB bandwidth: distribution shows that such constraints lead to realizable yield.16      | 68         |

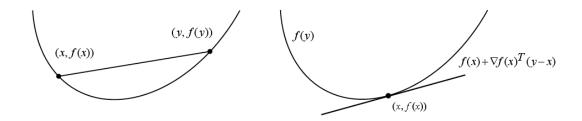

| Figure | 29 (Left):Graph of a convex function; the chord between <i>any</i> two points on the graph lies above the graph. (Right): Graphical illustration of the first-order condition for convexity                             | 69         |

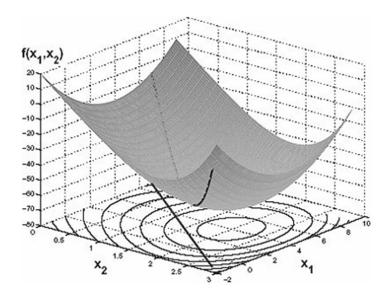

| Figure | 30 Graphical representation of a convex surface                                                                                                                                                                         | 70         |

### CHAPTER 1

### INTRODUCTION

The objective of this research is the development of circuit sizing and statistical design-for-manufacturability methodologies for embedded, passive radio-frequency (RF) circuits.

With the revolutionary development in wireless communications technology, the need is continuously increasing for RF front-end modules that combine low cost, small size and high performance. At the same time, with the convergence of multiple wireless communications standards, the design constraints and manufacturing issues for RF modules are greater than ever. Two factors account for most of these difficulties. The first is the increased complexity of current cellular/wireless devices because of the increase in circuit functionality. Moreover, RF designers must deal simultaneously with multiple design constraints while also meeting several performance specifications across multiple frequency bands. Manual iterations in circuit solvers and field solvers are typically used in design flows to meet such design goals. These design iterations, however, can become computationally prohibitive. Consequently, time-efficient design closure is becoming increasingly difficult in the design of modern communications systems.

Secondly, system on package (SOP)-based technologies have emerged as strong candidates for the integration platform of next-generation, multi-functional communications devices [1], [2], [3]. Unlike a system on chip (SOC) in which the package exists solely for the thermal and mechanical protection of the ICs, SOP provides for an increase in the functionality of the integrated circuit (IC) package by supporting multiple dice and embedded passives. SOP can be viewed as a multichip module (MCM) [4], [5] that has more than one IC but has a better system-level perspective and hence is a more sophisticated packaging technique. A conceptual representation

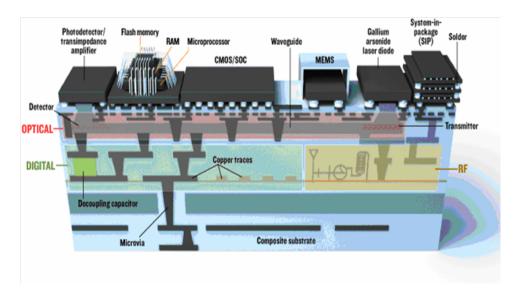

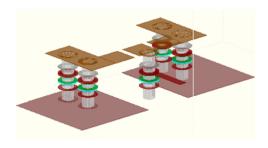

Figure 1. Illustration of an SOP test bed that combines: an optical circuit with waveguide and detector just beneath the surface; RF thin-film components embedded within the package; and digital thin-film components at the bottom.

of a SOP test-bed is shown in Figure 1 [6].

However, the current design flow for the SOP-based systems is not as efficiently modularized into multiple levels of physical and logical abstraction as its SOC counterpart [7]. In addition, the new technologies have not been well-characterized because of the absence of adequate technological data. As a result, design optimization does not translate into manufacturing yield optimization.

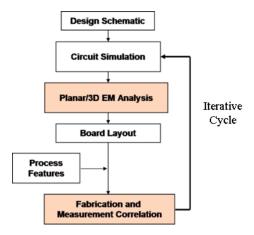

The design of wireless components/modules, operating at very high frequencies and narrow bandwidths, is challenging [8], [9]. For example, high performance RF filters should exhibit low insertion loss, sharp roll-offs for filtering and channel selection, and preferably have low cost [10]. If RF circuit design is to be cost efficient, the design-cycle time must be reduced. The need for fast design closure for SOP-based RF circuits is best explained with the help of a flow chart, shown in Figure 2, of the stages in RF circuit design.

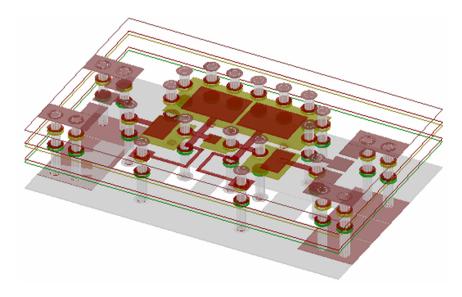

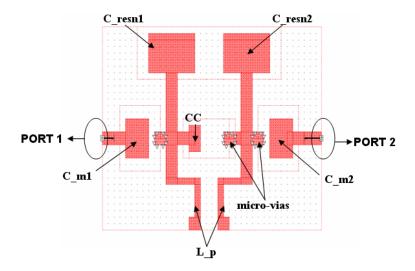

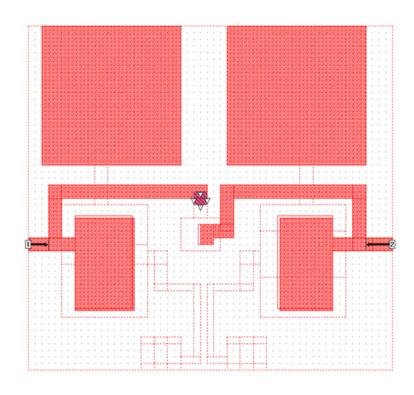

The flow is applied to the design of an RF bandpass filter with quasi-lumped embedded inductors and capacitors in multi-layer substrate. The layout of the filter (including probe-pads, signal vias and thruholes) is shown in Figure 3.

Figure 2. Typical design flow for RF circuits; grey represents time/memory bottleneck in the design flow.

Figure 3. Layout of a bandpass filter in SONNET EM solver.

In Figure 2, the design flow begins with an ideal schematic in a circuit simulator. Design values derived from firsthand calculations are used to quickly arrive at rough estimates of the performance specifications. The optimized design values are then used to extract the layouts of the corresponding circuit components (Ls, Cs, Rs).

Typically, the layouts of the components are chosen from predesigned libraries. In many cases, the design values of the circuit components and library components are not exact matches. In such cases, the component with the closet value is chosen and its geometries are varied so that the required component specs are met. Full-wave electromagnetic (EM) solvers are typically used to tune layouts. EM solvers are computationally expensive but accurate. They capture the physical effects of layout, e.g. the parasitics and the EM coupling. However, multiple iterations are required to obtain the convergence necessary for accurate component values. Furthermore, when the layout components are connected via interconnects at a later stage of the design flow, these interconnects add to the inductance, resistance and parasitic capacitance of the overall circuit [9]. Consequently, the circuit response is modified and manual EM iterations are required again to restore the design specifications for the overall layout.

After fabrication of the design, measurements are performed to verify whether the specifications are met. For designs that deviate significantly from the specifications, the corresponding layouts are manually perturbed via EM simulations to meet the specifications. Clearly, as shown in Figure 2, the iterative cycle continues till the specifications are met and the design is ready to be delivered to the market. In the absence of a robust computer-aided design(CAD) framework, the amount of manual intervention required for design tuning increases exponentially with design size, thereby increasing design cost and time.

The limitations/challenges in this flow are as follows:

(a) EM simulations of complete layouts (which are time and memory intensive) are

a part of the iterative cycle instead of being a part of final verification.

- (b) Design optimization does not ensure high volume manufacturability.

- (c) Design flow lacks diagnosis. Diagnosis is the process of efficiently detecting and correcting faults in design (due to process variations). Commercial circuit simulator (e.g. Agilent's Advanced Design System (ADS) [11]) does circuit-level design of experiments (DOE) for statistical analysis, but it does not have diagnostic capability that can reduce the test time.

The statistical analyses of RF circuits that are solely based on circuit simulators provide fast but inaccurate results. The conventional method used to study the effect of component variations on system performance is to perform Monte Carlo (MC) analysis [12]. The MC analysis with full layout EM simulations is accurate but can be prohibitively time and/or memory-intensive.

### 1.1 The SOP paradigm for RF circuits

Developments in packaging technology have led to potentially cost-effective alternatives for systems integration, namely the system-on-package (SOP) approach [6],[13],[14]. A SOP module permits high levels of functional density by incorporating combinations of wirebond, flip-chip, stacked devices, embedded devices, MEMS, and package-on-package [15]. Moreover, SOP technology requires less power and generates less noise at the interconnect level, allows flexibility in mixing IC technologies, and reduction of board size and cost through inclusion of passive components [9]. Furthermore, compared with existing solutions based on SOC, SOP modules can be developed quicker.

From a designer's perspective, the use of SOP technology provides for design flexibility as well. For example, the noise figure of a low-noise amplifier is strongly dependent on the base/gate inductance of the active device [16]. On-chip solutions are

limited by the low quality factors (Qs) of the passives due to the high substrate losses [17], [18], [19]. In an SOP platform, the critical base inductance can be moved to the package, thereby increasing its Q, while the amplifier transistor can be integrated as a silicon die [16]. Therefore, a co-design approach can be achieved in an SOP design environment, thereby leading to better performance.

Despite the advantages, the use of embedded passive components for the design of RF circuits in SOP is considered bulky and risky. This can be attributed to the low tolerance for variations, the lower yield of the embedded components, and the increased cost of the substrate. The new SOP-based technologies are not yet optimized and well-characterized due to the absence of adequate technology data. Problematically, reference flows are lacking, concept feasibility is time-consuming and often inaccurate, and collaboration across the design chain is poor.

To improve time-to-market via design cycle reduction, SOP design has to move from an **expert methodology** to a **mainstream design methodology** - one that is **automated**, **integrated**, **reliable**, **and repeatable**.

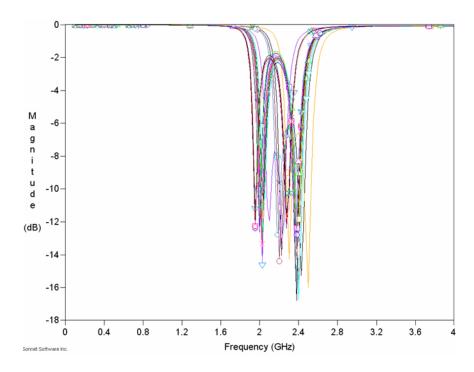

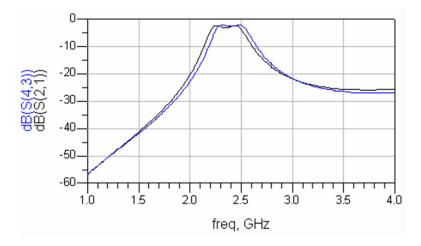

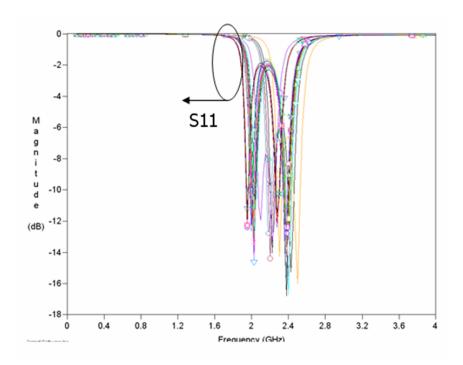

For example, the return loss (S11) variations for a measured set of 50 samples of an embedded RF bandpass filter are shown in Figure 91. The bandpass filters were implemented using organic substrate with multi-layer LCP technology. The filter circuit was designed for a center frequency of 2.4 GHz, and 1 dB bandwidth of 100 MHz. From the figure, it can be seen that the narrow passband varies significantly in different samples due to manufacturing variations. Therefore, in volume manufacturing, it is critical to estimate and optimize the statistical metrics of the performance measures.

The aforementioned discussion summarizes the need for layout scaling techniques and statistical manufacturability analysis for fast design closure and high-volume manufacturability on emerging SOP-based packaging technologies. The focus of this dissertation is depicted by the shaded boxes in the Figure 5.

Figure 4. Return loss (S11) variations of an embedded RF bandpass filter.

Figure 5. Design stages of an RF circuit; the focus areas of the dissertation have been shown by shaded boxes.

### 1.2 Need for Layout Scaling Methods in RF Design

Layout-level circuit scaling is the process of extracting network/layout-level parameters for a component/circuit from an existing set of different design specifications. It is common in digital designs and is being used increasingly in low-frequency analog circuits. Clearly, the key to fast design closure of digital ICs lies, partially, in the modular framework of the SoC CAD tools. A typical digital IC design flow proceeds from concept to cell-based logic design, cell-based logic synthesis, clock insertion, floor-planning, routing, design-for-manufacturability checking, design-rule checking and final tape-out [20]. Design changes in such a cell-based modular framework are time-efficient. The designer needs to specify the changes at a high/behavioral level of abstraction. The corresponding modifications in the low-level circuit blocks are realized through parameterized functional links between different design levels.

Current RF design tools, however, lack the capability of parametric cell approach implemented in a CAD framework. This can be attributed of the complexity of physical effects that needs to be considered while simulating a SOP-based RF module [9]. A few such critical parameters can be substrate coupling, near-field coupling, far-field coupling, component parasitics, large process tolerances and board warpage [9], [21]. Most of the aforementioned parameters are not encountered in silicon-based digital technologies, thereby facilitating a cell-based design flow.

The design emphasis of most wireless products is to provide the smallest form factor solution (hence, the cheapest solution) with the maximum functionality. SOP-based RF modules have emerged as a high-performance solution for designing multi-band wireless systems. Clearly, design cycle time must be reduced if cost-effective fabrication of RF modules on such technologies is to be achieved.

### 1.2.1 Simulation/optimization using circuit solvers

Standard circuit simulators use the description of a circuit in terms of lumped circuit elements and coupled (transmission) lines to account for distributed effects and/or

directly rely on S-parameter (or, equivalently Y or Z-parameter) descriptions of the different parts of the circuit. The circuit simulator approach, in general, relies on a divide-and-conquer technique in which the circuit is subdivided into separate parts for which models exist or can be calculated [22], [23], [24]. Kirchoff's current and/or voltage laws are then applied to obtain the overall circuit equations and solutions.

The advantages of the circuit simulator approach is clear; this approach is fast and, therefore, can be easily integrated with advanced network optimization techniques. However, for proper design of microwave, RF, and high-speed digital circuits, it is necessary to take into account the electromagnetic effects of the actual layout. When considering the more general class of microwave circuits, there is even less evidence of the need to distinguish between the circuit description and EM behavior because physical effects are often an integrated part of the desired circuit performance [25].

### 1.2.2 Simulation/optimization using EM solvers

Based on the reasoning in Section 1.2.1, more reliance on EM solvers for RF circuit design and optimization purposes would seem natural. This straightforward thought, however, has multiple disadvantages. Despite phenomenal progress in the development of field solvers and the availability of powerful computing systems, field solvers nevertheless continue to be slow in comparison with circuit solvers. This slowness is detrimental to their use for optimization, tuning, yield analysis, etc., which require a large number of circuit evaluations. Additionally, lumped-element values derived from EM analysis turn out to be quite sensitive to the parameters that control the EM simulation, in particular, the size of mesh cells [9]. For example, the layout of a second order bandpass filter with via pads and thruholes in SONNET is shown in Figure 3. To accurately capture the effects of the vias, the maximum size of the mesh cells can, at best, be a fraction of the via features. In case of uniform size of mesh cells in the layout, this can lead to a large number of mesh cells, and therefore, long simulation time.

EM solvers are based on different numerical approximation techniques for solving the Maxwell's equations to solve for fields, voltages and/or currents. Quite expectedly, such spatial/temporal discretization-based solution techniques are time and memory intensive. Unlike SoC design flows, SOP-based RF design involves significant amounts of EM simulations to analyze the physical effects of the layout. A full factorial MC analysis in a full-wave EM solver can, therefore, require impractical amounts of CPU time and memory resources for even simple structures.

In summary, the EM/circuit analysis and optimization tradeoff problem can be viewed as follows; EM field simulators offer highly accurate results, but this accuracy most often comes with high memory requirements and slow performance in terms of CPU time. On the other hand, conventional circuit simulators are fast and highly flexible but do not account for all the field effects, and their accuracy hinges strongly on the availability of models. The question naturally arises as to how we can properly combine field analysis and circuit analysis in such a way that their respective advantages are optimally utilized in terms of reduced design cycle time in combination with acceptable performance and manufacturing yield.

### 1.2.3 EM-circuit co-simulation

A wide array of literature exists on the combination of field and circuit analysis for optimization purposes [26], [27], [28]. An early contribution to the combination of field and circuit analysis can be found in [29]. Here, a time-domain simulator is based on a spatial network method (SNM). This work emphasizes on the inclusion on nonlinear elements but the focus is not design scaling of circuit layouts.

Optimization of silicon-based RF inductors based on geometric programming has been described by [30]. However, this method is limited by the use of analytical expressions for inductor parameters. This is because it is difficult to extract accurate, closed-form expressions for inductor parameters in multi-layer substrates. Mapping

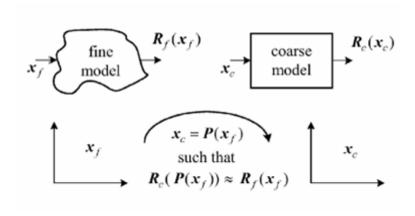

Figure 6. Illustration of the concept of space mapping.

of electrical parameters of inductors to layout parameters using polynomial functions have been shown in [31], [32]. The technique provides good interpolation for single or multiple parameter variations for weakly non-linear data. However, this method does not provide convergence to a unique solution in a multi-variable optimization environment.

Efficient EM optimization using space mapping (SM) is described in [33]. The SM-based algorithm is shown in Figure 6, where a linear mapping is developed between the parameter space of the coarse model and that of the fine model. The coarse model is obtained from extensive, circuit-based simulation data while the fine model is obtained from limited, time-consuming, but accurate EM simulation data. However, these methods are ideally suited for optimizing structures once it has been generated.

Artificial neural network (ANN) based modeling techniques have also been applied for the optimization of linear and nonlinear circuits [34], [35], [36]. Recent work has reported the application of ANN-based coarse models for design optimization of compact RF passive circuits on multi-layer substrates like low temperature co-fired ceramic (LTCC) technology [37], [38]. However, the focus of these works is on time-efficient layout optimization and not layout-level scaling.

Figure 7. SONNET model of a spiral inductor in multi-layer substrate.

### 1.2.4 Circuit augmentation for broadband modeling and circuit tuning

As the RF system design complexity increases, it is imperative that the designer have access to accurate models for passive components and interconnects based on network analyzer measurement data or electromagnetic field solver results. Traditionally, an electrical model is created out of ideal circuit elements to fit the data [39].

Each element of the simple circuit model, if properly constructed, can represent meaningful electrical characteristics of the parameter being modeled. In other words, a "physics-based" model provides the designer with valuable insight into the object being modeled. However, this method has its set of disadvantages. It is very difficult and time-consuming to develop a physical model [40]; the task becomes increasingly difficult with frequency. Also, most of the physics-based modeling approaches provide "nominal" values for the model parameters, i.e. around the frequency where the model is extracted, and therefore, is unsuitable for accurate and broadband circuit-level optimization.

To illustrate the need for broadband modeling, a microstrip spiral inductor, shown in Figure 7, was simulated in SONNET EM solver. The values of the lumped circuit model parameters were extracted at a particular frequency. The circuit model for the inductor is shown in Figure 8. The difference in the frequency responses from

Figure 8. Multi-section lumped element model of a spiral inductor embedded in LCP substrate.

Figure 9. S-parameters from the EM model(black triangles) and the circuit model (red circles).

the EM simulation and that from the circuit model is shown in Figure 9. Clearly, the difference in the S-parameters needs to be minimized. Using ad-hoc modeling approaches, a large amount of trial and error may be required to find the location and value of the additional elements, rendering the procedure intractable for large (n > 20) number of components.

Over the last decade, there has been great interest in macromodeling techniques to fit frequency-domain data. The conceptual representation of the macromodeling approach is shown in Figure 10. The macromodeling technique aims to only match the terminal characteristics of the device. In common macromodeling approaches, the data is typically fit to a set of basis functions in the frequency domain [41], [42]. The methods vary as to how the locations of the basis functions are chosen and how their coefficients are determined. Usually, the methods implement some

Figure 10. Black-box macromodel for an N-port device.

form of least-squares fitting of the coefficients of the data. From the perspective of broadband modeling for design optimization, these approaches have a number of disadvantages. Firstly, the non-physical nature of these models relegates the use of these approaches to applications that only require the terminal characteristics of the devices being modeled. In addition, the presence of controlled sources and non-physical values of passives in the macromodeled data cannot be utilized to correlate the model parameters with the layout parameters. Also, there are a number of constraints these "black-box" models must satisfy: passivity, stability and causality. Of these, passivity is most difficult to guarantee [43], [44], [45].

Clearly, it is necessary to develop an algorithm that can retain the physical nature of the circuit model while providing some augmenting network to minimize the error at higher frequencies. The algorithm in [46] considers such an approach where the circuit model is augmented with a black-box (or purely mathematical) model so as to match the y-parameters of the circuit model with the given measured parameters. It is based on finding a modified network by curve-fitting the difference between the measured parameters and that of an initial circuit model. One of the drawbacks of this approach is that the augmented network is restricted in its placement, only to the terminals of the circuit model. From the perspective of high-frequency/broadband matching, this may not necessarily be the optimum solution. Also, as with any black-box type model, it can become a challenge to ensure passivity. A modification of this approach has been proposed in [47]. However, this approach stills requires the use of

synthesis methods, such as vector-fitting, or other network generation techniques to develop SPICE-equivalent circuits for the augmented elements from their impedance profiles.

Therefore, an automated broadband circuit modeling technique without the drawbacks of "macromodeling" approaches is critical to the development of an efficient SOP-based RF CAD framework.

# 1.3 Need for DFM (Design-for-Manufacturability) methods in RF design

During manufacturing, process variations will inevitably cause design parameters, such as component values, to waver from their nominal values. As a result, the manufactured circuits may no longer meet some performance specifications, such the group delay, gain and bandwidth (in case of a filter, for e.g.), that it was designed to satisfy.

The procedure of design-for-manufacturability (DFM) attempts to select the nominal values of design parameters so as to ensure that the behavior of the circuit remains within specifications, with the greatest probability. In other words, the aim of design centering is to ensure that the manufacturing yield is maximized. This problem has been extensively researched in the domain of digital IC technology. For IC design flows, successful design verification translates to optimum design yield. This can be attributed to the presence of a mature design and manufacturing infrastructure for digital IC/SOC manufacturers. The IC design infrastructure consists of predictive device models, complete digital CMOS characterization, statistical and scalable compact models that are hardware-verified, and a robust, parametric, and hierarchical design automation environment [48],[49].

Previous approaches to solving the design centering problem have traditionally taken two routes:

### 1.3.1 The statistical approach

In electrical engineering, the drive for high yield and high performance have prompted researchers to develop many statistical methodologies. These studies were predominantly aimed for chip or component level yield estimation, and statistical circuit optimization. Although relevant contributions will be referred in the subsequent sections, it is suitable to categorize this effort into three main areas. In this section worst-case, Monte Carlo, and design of experiments (DOE) principles are discussed. Almost all statistical methods can be considered as improvements upon the combinations of these principles.

### 1.3.1.1 Worst case Analysis

The classical approach to account for process and functional uncertainties in a circuit/module is the worst-case analysis. After the worst-case combinations of the design parameters are verified, all products are expected to meet the specifications [50]. However, this conservative design approach has major limitations [51]. First, it requires an initial guess of the worst-case scenario. Full factorial simulations to find the worst-case point is inefficient. Furthermore, with a large number of performance measures, finding the worst-case parameter combination for each performance measure becomes very difficult. Also, the worst-case combination, where all design parameters are at their extremes, has very low probability of occurrence. Therefore, designs that are based on the worst-case analysis may underestimate the performance and increase the design effort.

### 1.3.1.2 Monte Carlo Analysis

The most prevalent methodology in the manufacturing community to estimate the parametric yield of a design is the Monte Carlo (MC) analysis [12]. This technique depends on simulating a large number of design parameter combinations for generating the performance statistics. The values of the design parameters are generated from random variables with associated probability distributions and correlations. Then,

the yield is approximated as the ratio of the number of acceptable instances to the total number of Monte Carlo runs. This can be mathematically formulated as

$$Y = \int_{-\infty}^{\infty} z(x)f(x)dx,$$

(1)

where z(x)=1 if all design values (x) satisfy the specifications, and z(x)=0 otherwise. In Equation 1, f(x) is the joint probability density function of design parameters. Then the yield can be estimated as:

$$\hat{Y} = \frac{1}{N} \sum_{i=1}^{N} z(x_i), \tag{2}$$

and

$$\hat{Y} = \frac{1}{N} \sum_{i=1}^{N} z(x_i) \frac{f(x_i)}{h(x_i)},\tag{3}$$

Depending on the complexity of the simulation model, and the number of process and operational variables, the "simulation space" of the Monte Carlo method may become prohibitively large. This has led to the development of different sampling methods in the field of statistical analysis to optimize the error without exponentially increasing the number of simulations [52], [53], [54], [55]. An excellent survey of these sampling algorithms is provided in [56].