# NOISE SUPPRESSION AND ISOLATION IN MIXED-SIGNAL SYSTEMS USING ALTERNATING IMPEDANCE ELECTROMAGNETIC BANDGAP (AI-EBG) STRUCTURE

A Dissertation Presented to The Academic Faculty

by

### Jinwoo Choi

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology December 2005

**COPYRIGHT © JINWOO CHOI 2005**

# NOISE SUPPRESSION AND ISOLATION IN MIXED-SIGNAL SYSTEMS USING ALTERNATING IMPEDANCE ELECTROMAGNETIC BANDGAP (AI-EBG) STRUCTURE

#### Approved by:

Dr. Madhavan Swaminathan, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Abhijit Chatterjee School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Suresh K. Sitaraman School of Mechanical Engineering Georgia Institute of Technology Dr. Andrew F. Peterson School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. W. Marshall Leach School of Electrical and Computer Engineering Georgia Institute of Technology

Date Approved: November 29, 2005

Dedicated to

my parents

and

my brother and sister, and my aunt

for their support, encouragement, and love

#### **ACKNOWLEDGEMENTS**

First, I would like to thank my advisor, Professor Madhavan Swaminathan, for his guidance and support during my graduate studies. He is an outstanding mentor and a tremendous source of motivation. I would also like to extend my gratitude to the Ph.D. committee members: Professor Andrew F. Peterson, Professor Abhijit Chatterjee, Professor Marshall Leach, and Professor Suresh K. Sitaraman. I appreciate their time and effort in serving on my Ph.D. committee.

I would like to extend special thanks to all current and graduated Epsilon group members. Your friendship, assistance, and opinions will always be appreciated. I would especially like to mention Dr.Vinu Govind, Dr. Joong-Ho Kim, Dr. Nanju Na, Dr. Sungjun Chun, Dr. Sidharth Dalmia, Dr. Erdem Matoglu, Rohan Mandrekar, Bhyrav Mutnury, Souvik Mukherjee, Dr. Jinseong Choi, Dr. Jifeng Mao, Dr. Woopoung Kim, Krishna Srinivasan, Amit Bavisi, Dr. Lixi Wan, Subramanian Lalgudi, Krishna Bharath, Dr. Sung-Hwan Min, Sunanda Janagama, Dr. Toyoda, Dr. Ege Engin, Wansuk Yun, Tae Hong Kim, Nevin Altunyurt, Marie-Solang Milleron, Abhilash Goyal, and Gijin Han.

I would like to thank Dong Gun Kam, Daehyun Chung and Professor Joungho Kim at Korea Advanced Institute of Science and Technology (KAIST) for their help for far field measurements and simulations.

I would like to thank James P. Libous, John Purcell and Michael Nealon at IBM for their encouragement for my studies at Georgia Tech.

I would like to thank Semiconductor Research Corporation (SRC) for providing fund for my research during my graduate study at Georgia Tech.

Finally, I would like to thank my parents, my brother, my sister, and my aunt for their love, support, and encouragement.

## TABLE OF CONTENTS

|                                                                          | Page |

|--------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                         | iv   |

| LIST OF TABLES                                                           | X    |

| LIST OF FIGURES                                                          | xi   |

| SUMMARY                                                                  | xvii |

| CHAPTER 1: Introduction                                                  | 1    |

| 1.1 Power Distribution Network (PDN)                                     | 3    |

| 1.2 Simultaneous Switching Noise (SSN)                                   | 7    |

| 1.3 Decoupling Capacitors                                                | 9    |

| 1.4 Power/Ground Planes                                                  | 12   |

| 1.4.1 TEM Modes                                                          | 13   |

| 1.4.2 TM Modes                                                           | 15   |

| 1.4.3 TE Modes                                                           | 18   |

| 1.4.4 Cavity Resonator Modes                                             | 20   |

| 1.5 Noise Coupling in Mixed-Signal Systems                               | 22   |

| 1.6 Current Isolation Techniques                                         | 24   |

| 1.6.1 Split Planes                                                       | 25   |

| 1.6.2 Split Planes with Ferrite Beads                                    | 27   |

| 1.6.3 Power Segmentation Method                                          | 28   |

| 1.7 Electromagnetic Bandgap (EBG) Structure                              | 30   |

| 1.7.1 Mushroom-type EBG Structure                                        | 31   |

| 1.7.2 Mushroom-type EBG Structure for ultra wide band (UWB) applications |      |

|        | 1.8 Proposed Research and Dissertation Outline                                      | 40   |

|--------|-------------------------------------------------------------------------------------|------|

|        | ER 2: Modeling and Analysis of Power Distribution Network in High-<br>gital Systems | 48   |

|        | 2.1 Efficient Hybrid Methodology for PDN                                            | 51   |

|        | 2.2 Transmission Matrix Method (TMM)                                                | . 54 |

|        | 2.3 Rambus Test Vehicle                                                             | 59   |

|        | 2.4 Modeling of Master-Slave PDN                                                    | . 69 |

|        | 2.5 Modeling and Analysis of Power Supply Noise                                     | 74   |

|        | 2.6 Summary                                                                         | 78   |

|        | ER 3: Alternating Impedance Electromagnetic Bandgap (AI-EBG)                        | 80   |

|        | 3.1 Periodic Structures                                                             | 81   |

|        | 3.2 Bloch Theorem                                                                   | 82   |

|        | 3.3 Design of AI-EBG Structure                                                      | 84   |

|        | 3.4 Equivalent Circuit Representation of AI-EBG Structure                           | 86   |

|        | 3.5 Stopband Center Frequency of AI-EBG Structure                                   | . 89 |

|        | 3.6 Propagation Characteristics of AI-EBG Structure                                 | 91   |

|        | 3.7 Cutoff Frequency of AI-EBG Structure                                            | 96   |

|        | 3.8 Summary                                                                         | 101  |

| СНАРТЕ | ER 4: Modeling and Analysis of AI-EBG Structure                                     | 102  |

|        | 4.1 Modeling and Simulation of AI-EBG Structure                                     | 103  |

|        | 4.2 Model-to-Hardware Correlation of AI-EBG Structure                               | 109  |

|        | 4.3 Parametric Analysis of AI-EBG Structure                                         | 114  |

|        | 4.3.1 Effect of Metal Patch Size                                                    | 114  |

|        | 4.3.2 Effect of Dielectric Constant                                                 | 115  |

|        | 4 3 3 Effect of Metal Branch Size                                                   | 117  |

| 4.3.4 Effect of Dielectric Material                                                                        | 118      |

|------------------------------------------------------------------------------------------------------------|----------|

| 4.3.5 Effect of Multi-layers                                                                               | 120      |

| 4.4 Summary                                                                                                | 122      |

| CHAPTER 5: Noise Suppression in Mixed-Signal Systems using AI-EBG and Characterization of AI-EBG Structure |          |

| 5.1 Mixed-Signal System Simulation                                                                         | 125      |

| 5.2 Design and Fabrication of Mixed-Signal Systems                                                         | 127      |

| 5.3 Noise Measurements                                                                                     | 129      |

| 5.4 Signal Integrity Analysis                                                                              |          |

| 5.4.1 Time Domain Waveforms                                                                                |          |

| 5.4.2 Time Domain Reflectometry Measurement                                                                | 136      |

| 5.5 Field Analysis of AI-EBG Structure                                                                     | 138      |

| 5.5.1 Near Field (NF) Simulation and Measurement                                                           | 139      |

| 5.5.2 Far Field (FF) Simulation and Measurement                                                            | 147      |

| 5.6 Design Methodology                                                                                     | 152      |

| 5.7 Summary                                                                                                | 154      |

| CHAPTER 6: Ultra-Wide Band (UWB) Applications of AI-EBG Structu                                            | ıres 155 |

| 6.1 Introduction                                                                                           | 155      |

| 6.2 Design of Hybrid AI-EBG Structure for UWB                                                              | 157      |

| 6.3 Fabrication and Measurement of Hybrid AI-EBG Structure                                                 | 161      |

| 6.4 Mixed-Signal System Simulation for UWB                                                                 |          |

| 6.5 Ultimate Isolation from DC to Infinite Frequency                                                       | 166      |

| 6.6 Summary                                                                                                | 168      |

| CHAPTER 7: Conclusions and Future Works                                                                    | 169      |

| APPENDIX A: Publications                                                                                   | 173      |

| APPENDIX B: Awards and U.S. Patents                                                                        | 179      |

| REFERENCES | <br> | <br> | <br> | <br> | 181 |

|------------|------|------|------|------|-----|

| Y ATTO     |      |      |      |      | 10  |

| VITA       |      |      |      |      | 194 |

## LIST OF TABLES

|                                                                            | Page |

|----------------------------------------------------------------------------|------|

| Table 1.1 Target impedance tendency and projection based on ITRS 2001      | 6    |

| Table 3.1 Cutoff frequencies for the AI-EBG structures in Figure 4.7       | 100  |

| Table 4.1 Material characteristics of three different dielectric materials | 118  |

| Table 5.1 Wavelengths for the standing waves using equation (5.2)          | 143  |

## LIST OF FIGURES

| Page                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1 Power distribution network for the typical high-speed digital system 3                                                                              |

| Figure 1.2 Equivalent circuit diagram for power distribution network                                                                                           |

| Figure 1.3 Output impedance for the typical power distribution network                                                                                         |

| Figure 1.4 Equivalent circuit for the system where the package and printed circuit board (PCB) metal layers add inductance to the power distribution network 8 |

| Figure 1.5 Model of the real decoupling capacitor                                                                                                              |

| Figure 1.6 Typical response of a real decoupling capacitor                                                                                                     |

| Figure 1.7 Cross section of BaTiO <sub>3</sub> capacitor                                                                                                       |

| Figure 1.8 Parallel-plate waveguide                                                                                                                            |

| Figure 1.9 Schematic of power/ground planes in package and board                                                                                               |

| Figure 1.10 Noise coupling in a mixed-signal system                                                                                                            |

| Figure 1.11 Photo of the fabricated split planes                                                                                                               |

| Figure 1.12 Measured $S_{21}$ for the split planes in Figure 1.10                                                                                              |

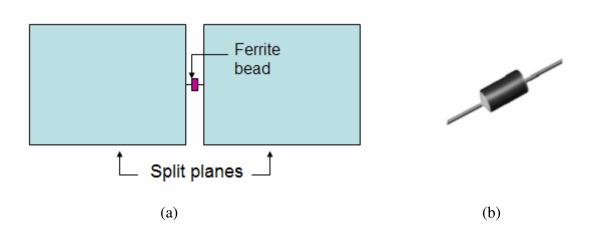

| Figure 1.13 (a) A ferrite bead between split planes and (b) Photo of a ferrite bead 27                                                                         |

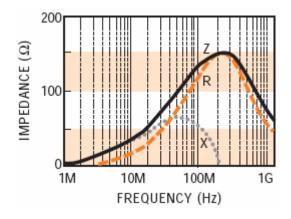

| Figure 1.14 Typical impedance characteristics of a ferrite bead                                                                                                |

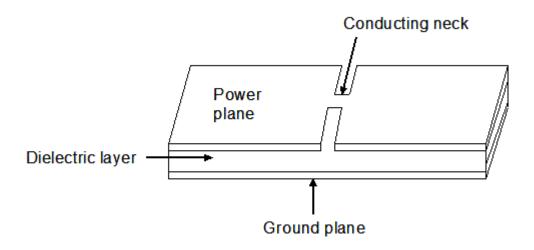

| Figure 1.15 Schematic of power-plane segmentation                                                                                                              |

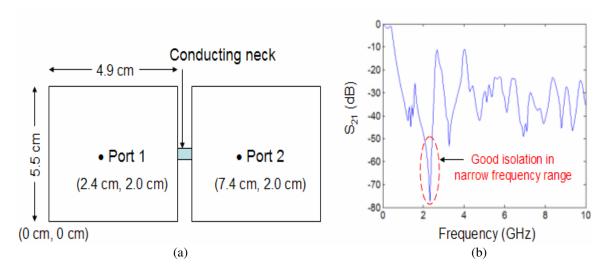

| Figure 1.16 (a) Schematic of the structure for simulation and (b) Simulation results 29                                                                        |

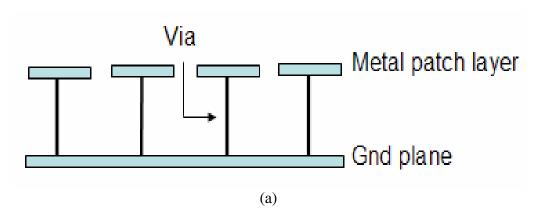

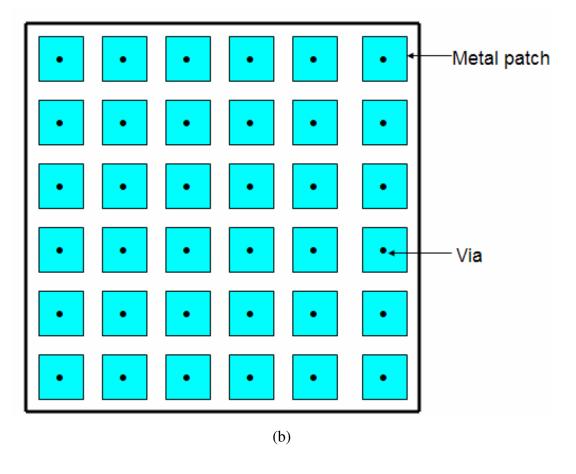

| Figure 1.17 (a) Cross-section of the mushroom-type EBG structure and (b) Top view of the mushroom-type EBG structure                                           |

| Figure 1.18 Origin of capacitance and inductance in mushroom-type EBG structure 32                                                                             |

| Figure 1.19 Parallel LC equivalent circuit for the structure in Figure 1.17                                                                                    |

| Figure 1.20 Geometrical parameters for the mushroom-type EBG structure                                                                                         |

| Figure 1.21 Cross-section of the modified mushroom-type EBG structure 3-                                                                                            | 4          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 1.22 Model for the modified mushroom-type EBG structure                                                                                                      | 5          |

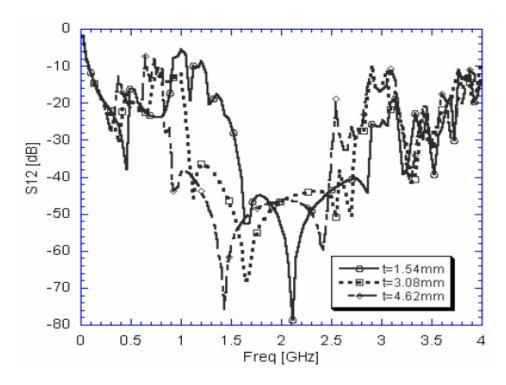

| Figure 1.23 Effect of via length (t) on S-parameter for the modified mushroom-type EBC structure                                                                    |            |

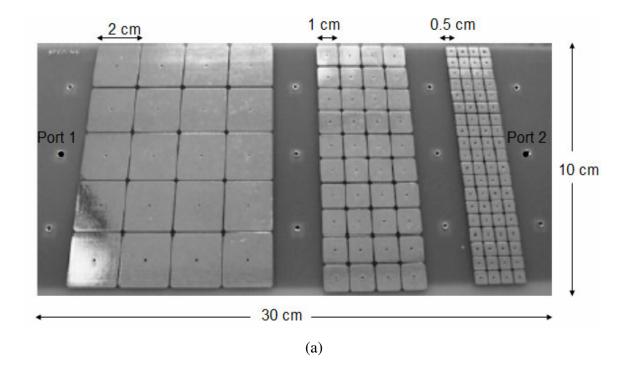

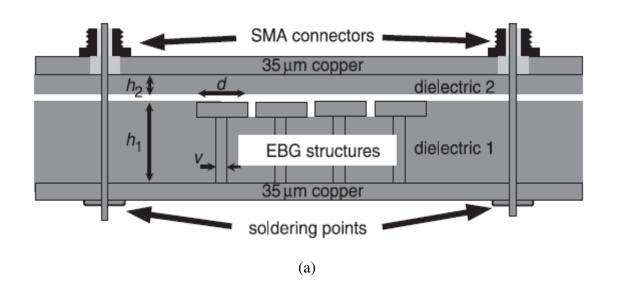

| Figure 1.24 (a) Mushroom-type EBG structure for UWB applications and (b) Measured transmission coefficient (S <sub>21</sub> ) results                               |            |

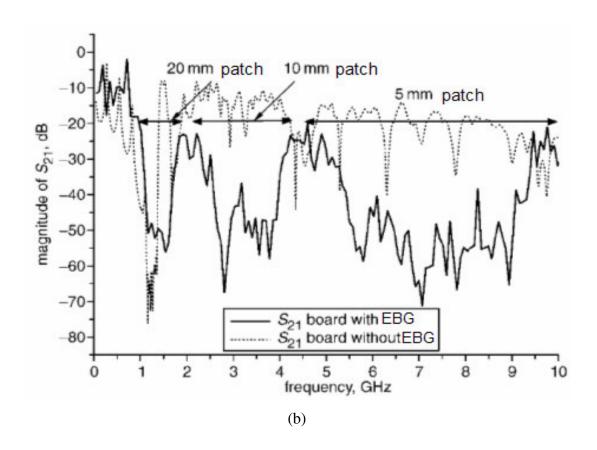

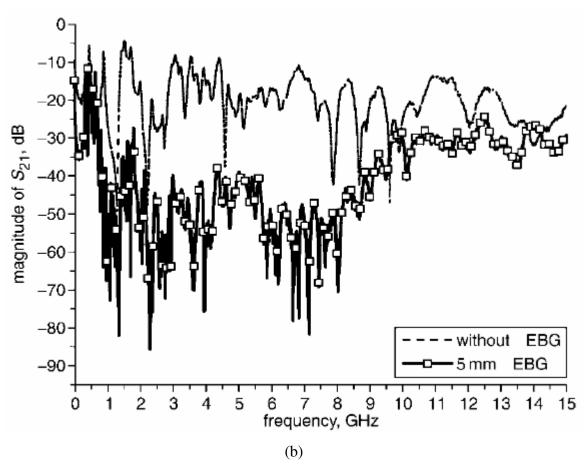

| Figure 1.25 (a) Cross section of the mushroom-type EBG structure with two dielectric materials and (b) Measured transmission coefficient (S <sub>21</sub> ) results | 9          |

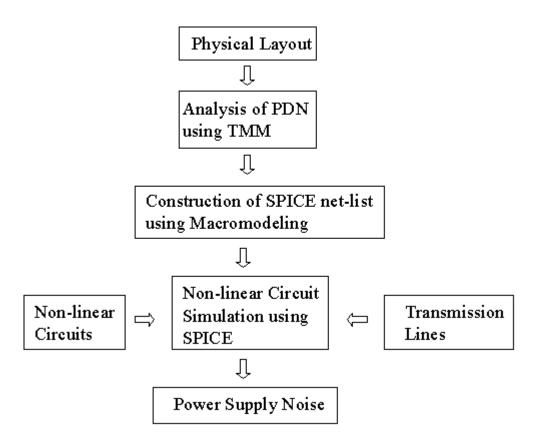

| Figure 2.1 Modeling and simulation methodology for PDN                                                                                                              | 2          |

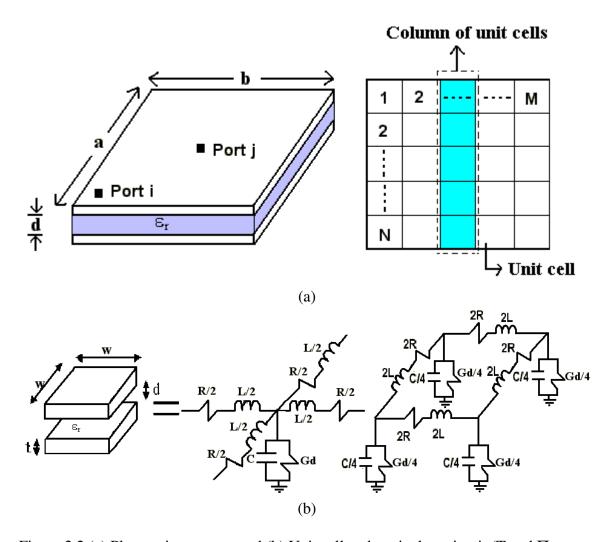

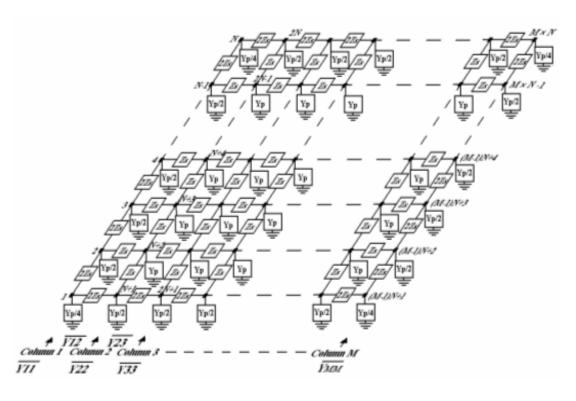

| Figure 2.2 (a) Plane pair structure and (b) Unit cell and equivalent circuit (T and Π models)                                                                       | 55         |

| Figure 2.3 Equivalent circuit for a pair of power/ground planes                                                                                                     | 6          |

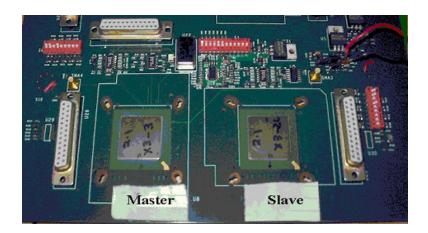

| Figure 2.4 Test vehicle from Rambus                                                                                                                                 | 59         |

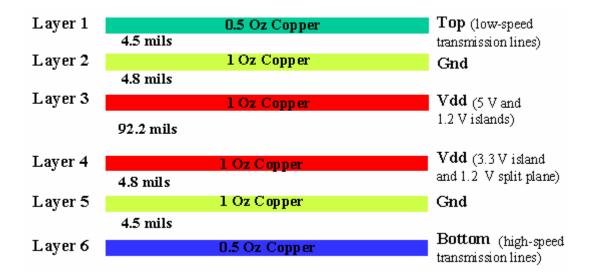

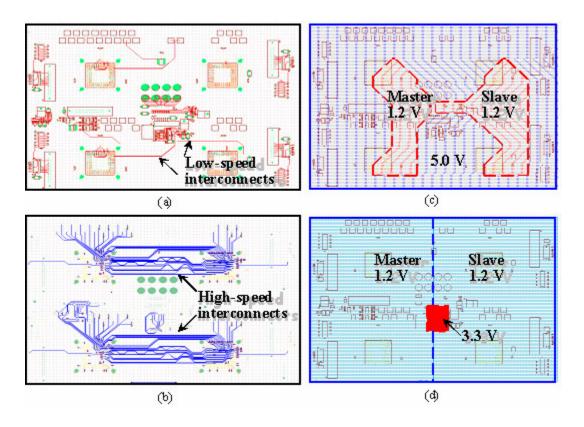

| Figure 2.5 Cross-section of the PCB                                                                                                                                 | 50         |

| Figure 2.6 Power and signal plane layers of the PCB                                                                                                                 | 51         |

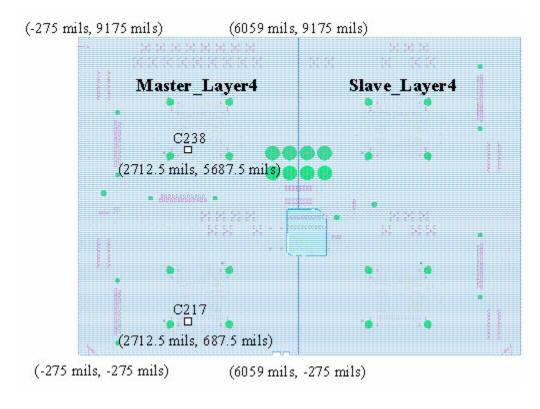

| Figure 2.7 Locations of C217 and C238 sites on layer 4                                                                                                              | 52         |

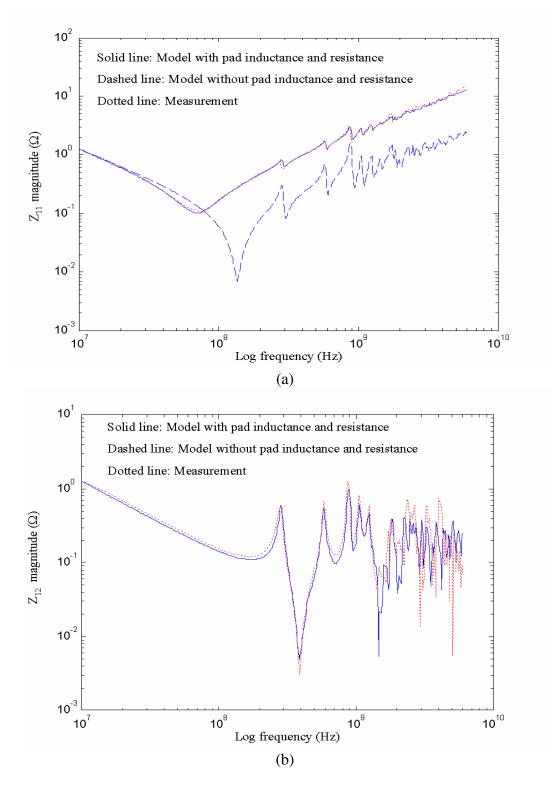

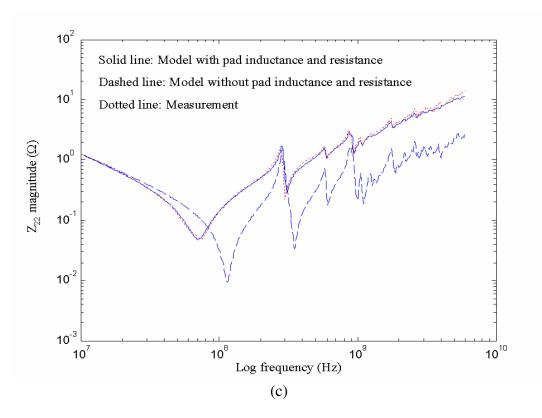

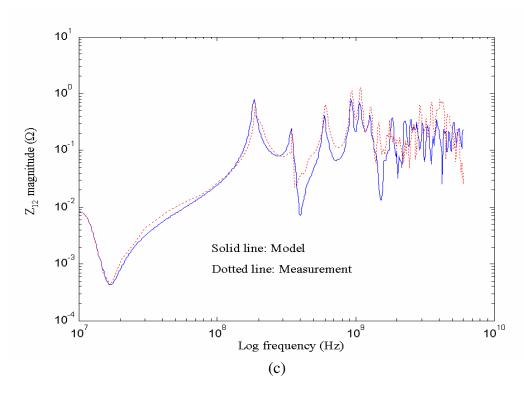

| Figure 2.8 Model-to-hardware correlation with and without pad parasitics 6                                                                                          | 53         |

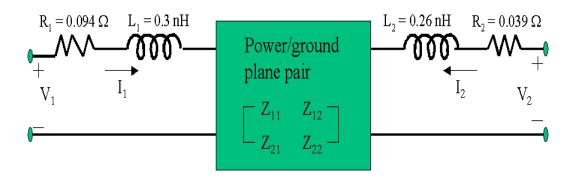

| Figure 2.9 Modified equivalent network of the power/ground planes 6                                                                                                 | 55         |

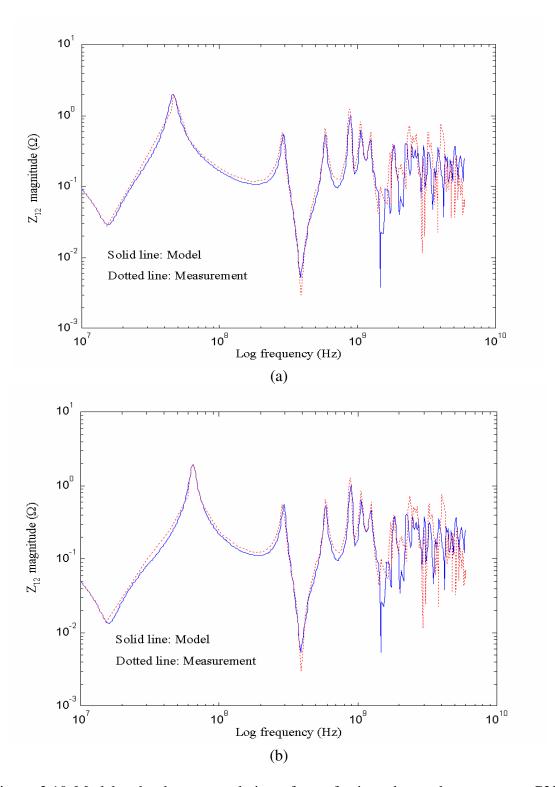

| Figure 2.10 Model-to-hardware correlation of transfer impedances between port C238 and port C217 in layer 4 and layer 5 in the PCB                                  |            |

| Figure 2.11 Model of power/ground plane pair with a decoupling capacitor 6                                                                                          | 59         |

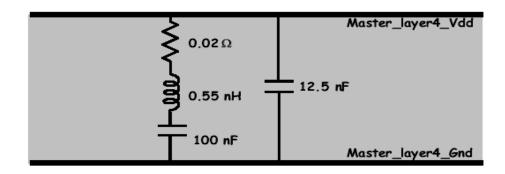

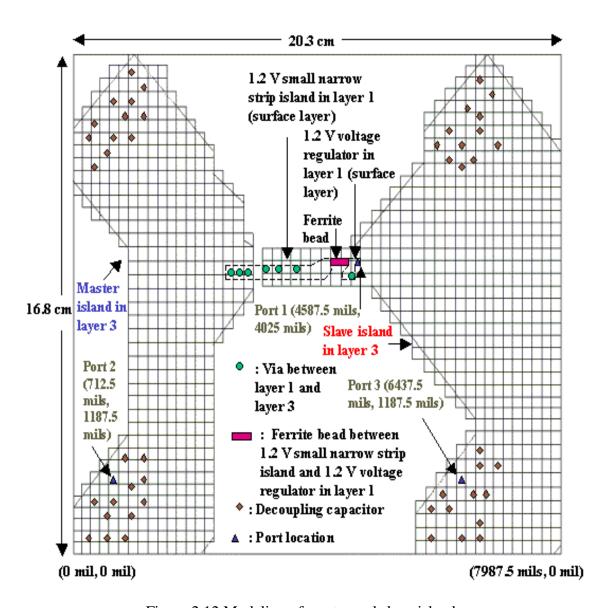

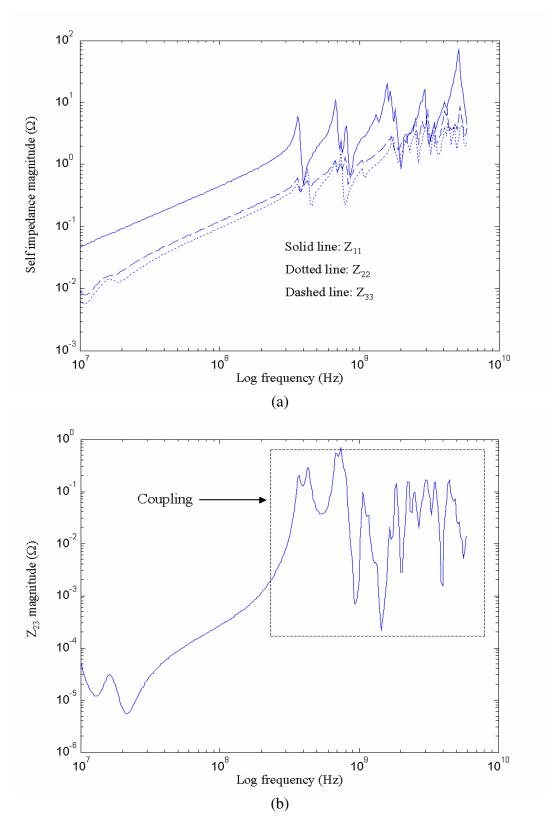

| Figure 2.12 Modeling of master and slave islands                                                                                                                    | 0          |

| Figure 2.13 Impedances of master and slave islands                                                                                                                  | '2         |

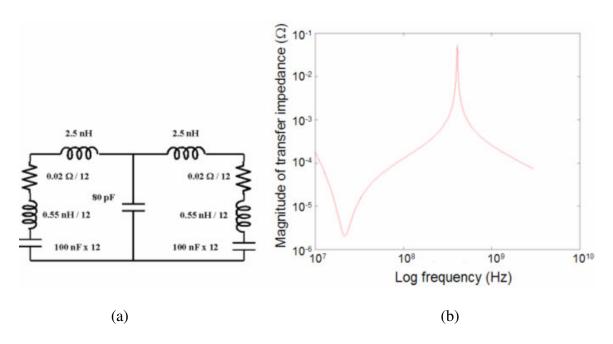

| Figure 2.14 (a)Equivalent circuit for coupling between master and slave islands and (b) its transfer impedance response between port 2 and port 3                   | 3          |

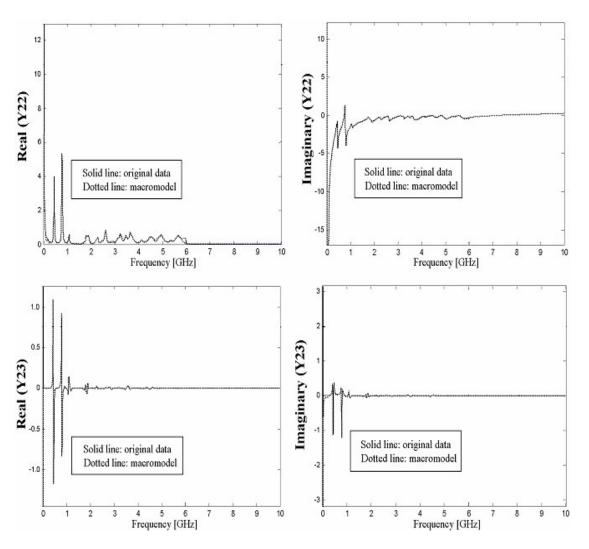

| Figure 2.15 Comparison between the input Y-parameters and macromodels                                                                                               | <i>'</i> 5 |

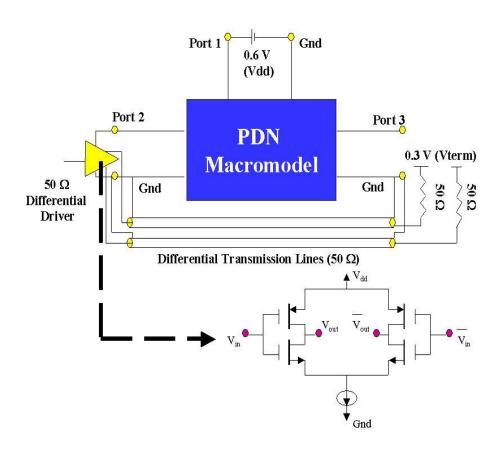

| Figure 2.16 Modeling of power supply noise with differential drivers, transmission lines and PDN macromodel                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

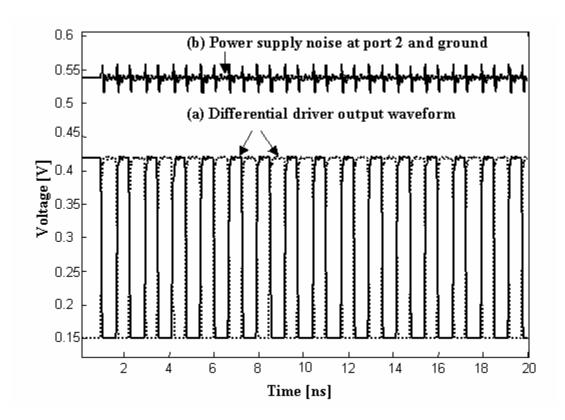

| Figure 2.17 Power supply noise simulation results                                                                                                                    |

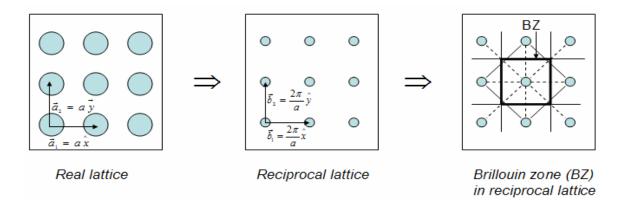

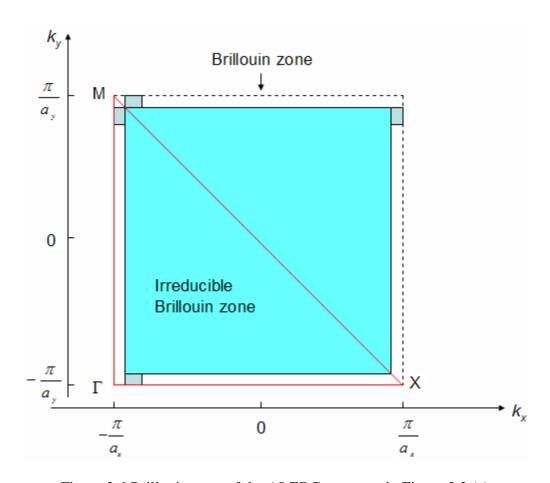

| Figure 3.1 Construction procedures for Brillouin zone (BZ) in reciprocal lattice 83                                                                                  |

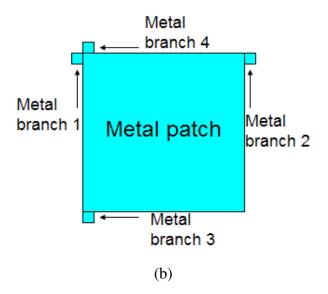

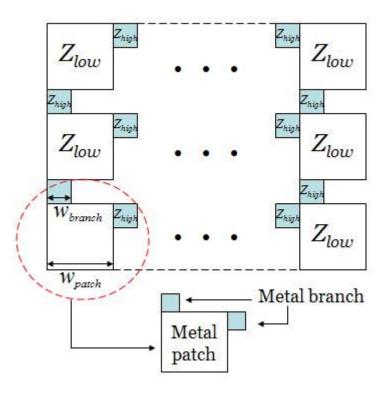

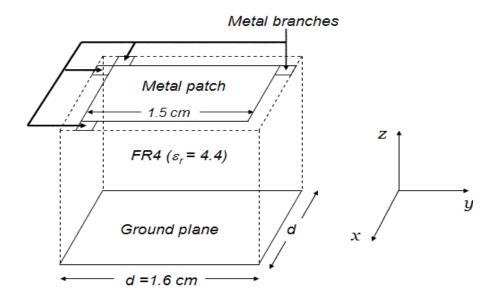

| Figure 3.2 Schematic of three-dimensional (3-D) alternating impedance electromagnetic bandgap (AI-EBG) structure                                                     |

| Figure 3.3 (a) Schematic of periodic pattern in one of power and ground planes and (b) Unit cell                                                                     |

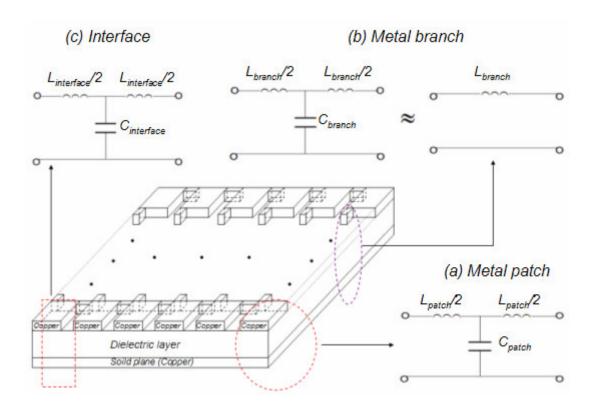

| Figure 3.4 EBG structure with alternating impedance                                                                                                                  |

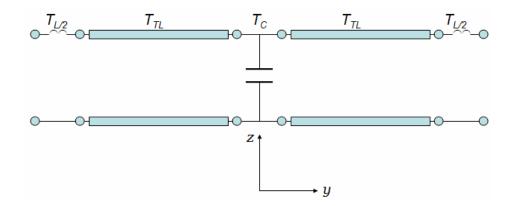

| Figure 3.5 One-dimensional (1-D) equivalent circuits for 3 parts of AI-EBG structure88                                                                               |

| Figure 3.6 Brillouin zone of the AI-EBG structure in Figure 3.3                                                                                                      |

| Figure 3.7 Two-dimensional (2-D) unit cell of the AI-EBG structure                                                                                                   |

| Figure 3.8 Equivalent TL circuit for the unit cell in Figure 3.7 on y-direction                                                                                      |

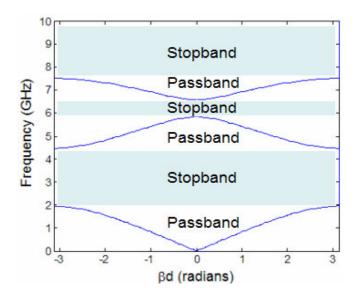

| Figure 3.9 Dispersion diagram of the AI-EBG structure using transmission line network (TLN) method                                                                   |

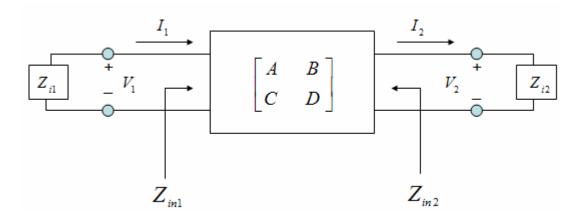

| Figure 3.10 Arbitrary two port network with its image impedances                                                                                                     |

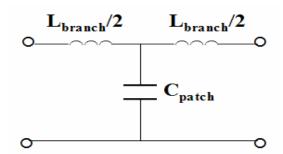

| Figure 3.11 Equivalent circuit of 1-D AI-EBG Structure                                                                                                               |

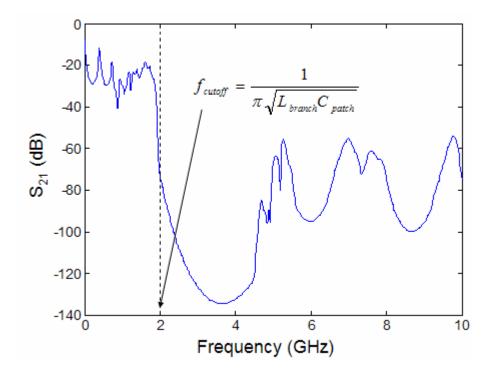

| Figure 3.12 Cutoff frequency of the AI-EBG structure in Figure 4.2 (a) with $S_{21}$ simulation result in Figure 4.2                                                 |

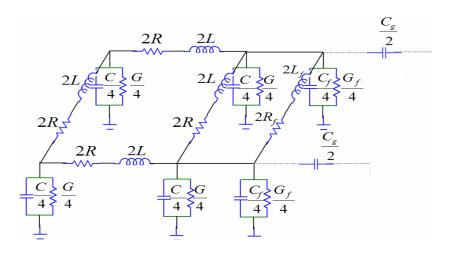

| Figure 4.1 Equivalent $\prod$ circuit for the unit cell including fringing and gap effects 104                                                                       |

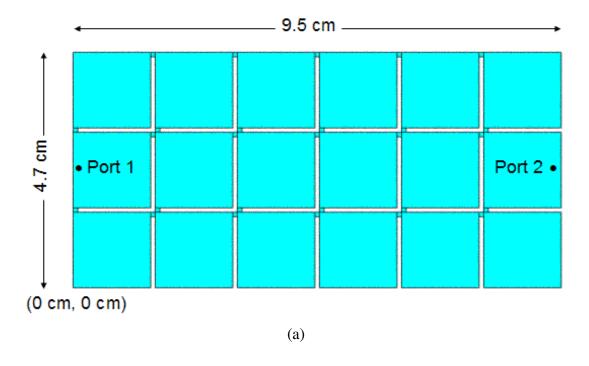

| Figure 4.2 (a) Schematic of the simulated AI-EBG structure and (b) Simulated results of S-parameters for the AI-EBG structure in (a)                                 |

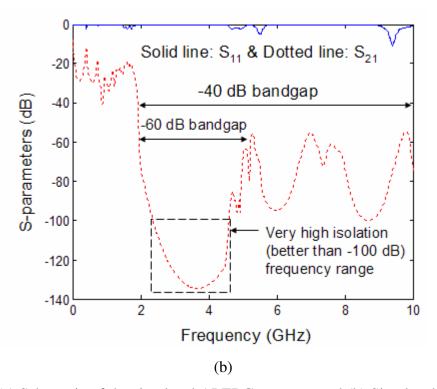

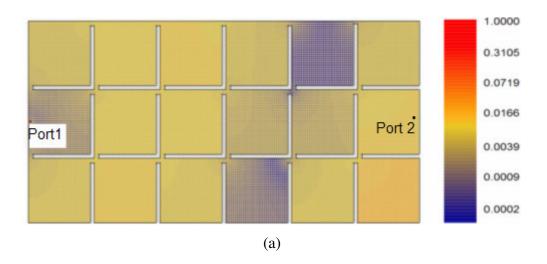

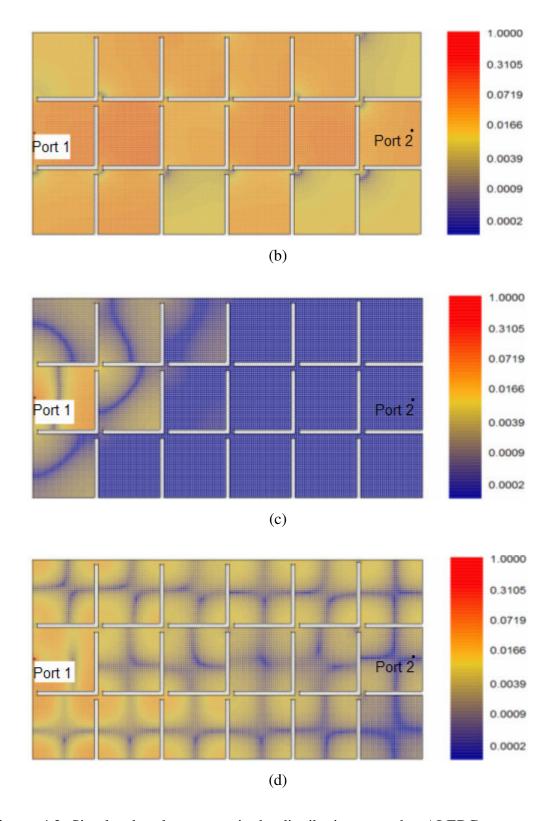

| Figure 4.3 Simulated voltage magnitude distributions on the AI-EBG structure at different frequencies (a) At 500 MHz, (b) At 1.5 GHz, (c) At 4 GHz, and (d) at 7 GHz |

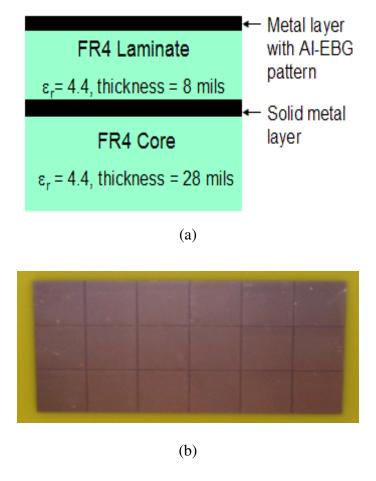

| Figure 4.4 Fabrication of AI-EBG structure (a) Cross section of fabricated AI-EBG structure and (b) Photo of fabricated AI-EBG structure                             |

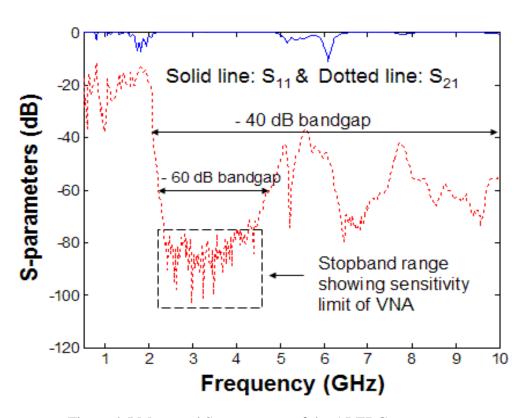

| Figure 4.5 Measured S-parameters of the AI-FRG structure                                                                                                             |

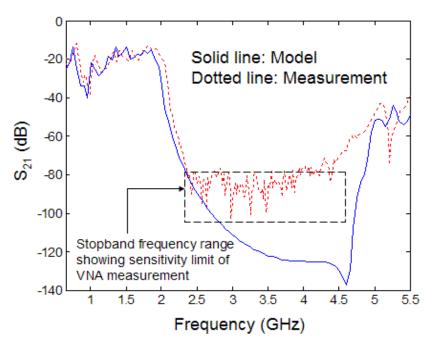

| Figure 4.6 Model-to-hardware correlation for the AI-EBG structure                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

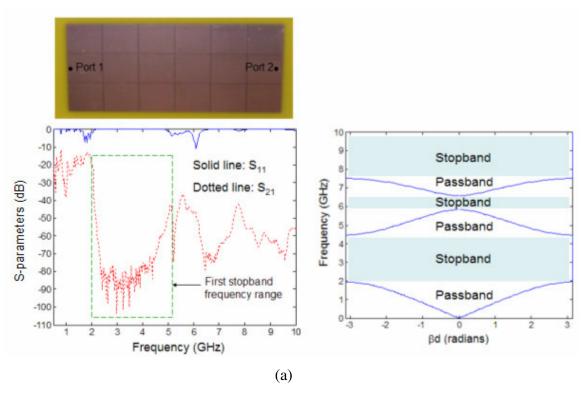

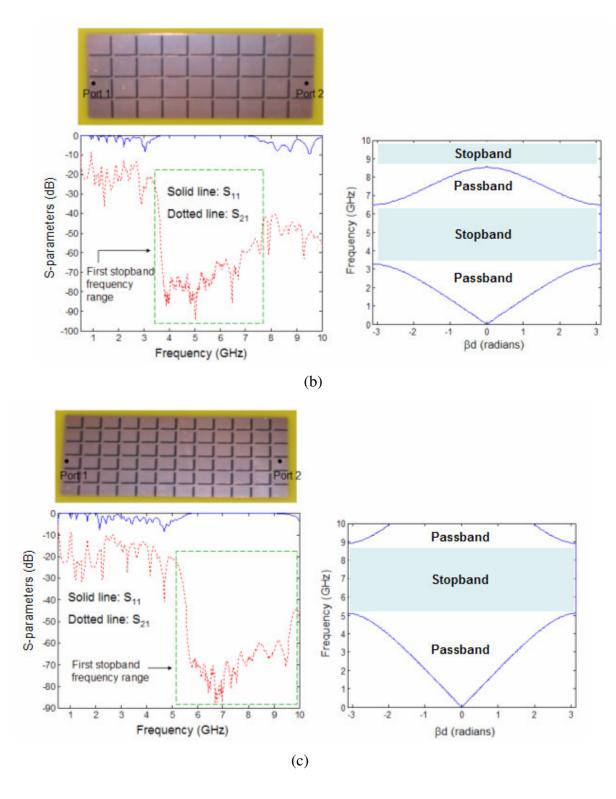

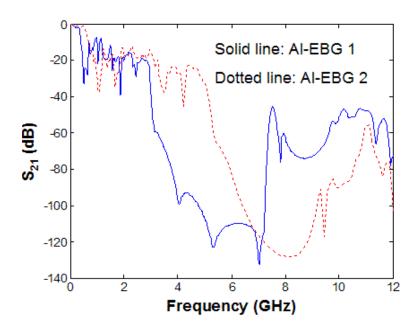

| Figure 4.7 S-parameter measurements: frequency tunability                                                                                                                                                                                         |

| Figure 4.8 Effect of metal patch size in AI-EBG structure                                                                                                                                                                                         |

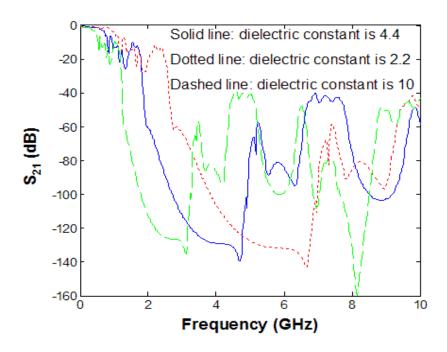

| Figure 4.9 Effect of dielectric constant in AI-EBG structure                                                                                                                                                                                      |

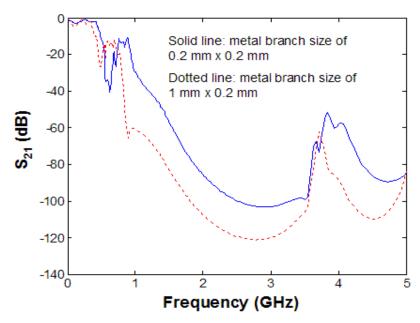

| Figure 4.10 Effect of metal branch size in AI-EBG structure                                                                                                                                                                                       |

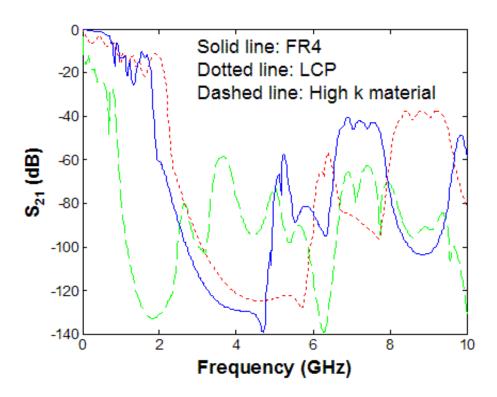

| Figure 4.11 Effect of dielectric material in AI-EBG structure                                                                                                                                                                                     |

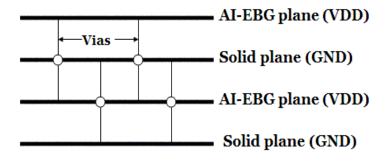

| Figure 4.12 Cross-section of the two plane pair                                                                                                                                                                                                   |

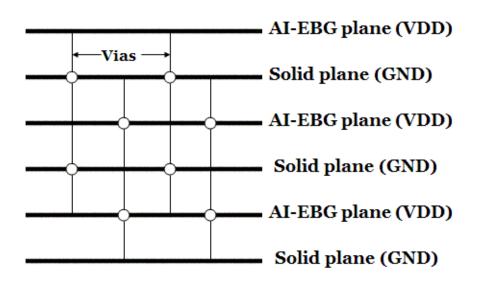

| Figure 4.13 Cross-section of three plane pairs                                                                                                                                                                                                    |

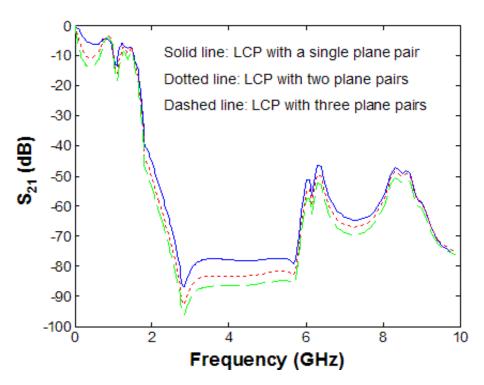

| Figure 4.14 Effect of multi-layers in AI-EBG structure                                                                                                                                                                                            |

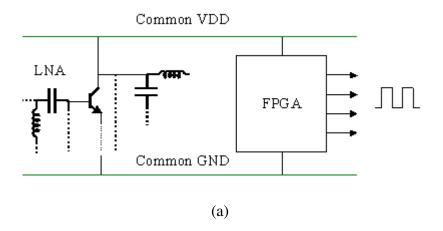

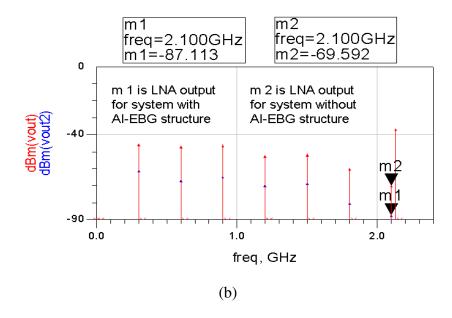

| Figure 5.1 Mixed-signal system simulation (a) Schematic of simulated mixed-signal system (b) Simulation results for mixed-signal systems with and without the AI-EBG structure                                                                    |

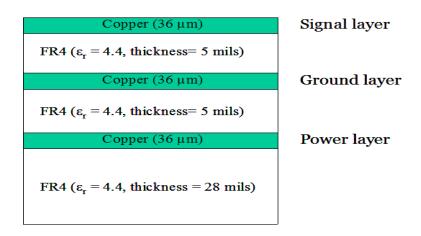

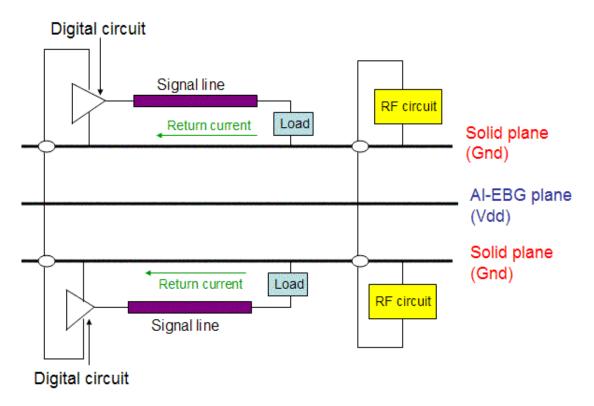

| Figure 5.2 Cross-section of the fabricated mixed-signal systems                                                                                                                                                                                   |

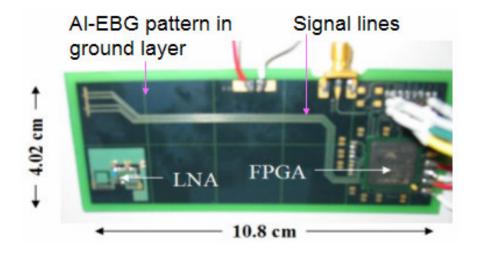

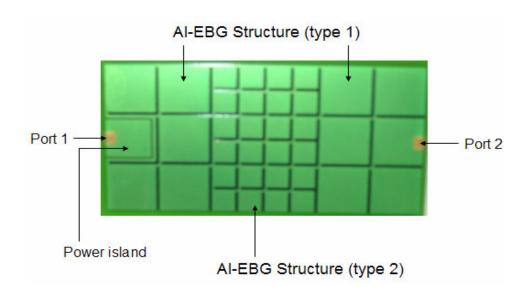

| Figure 5.3 Photo of the mixed-signal system containing the AI-EBG structure 128                                                                                                                                                                   |

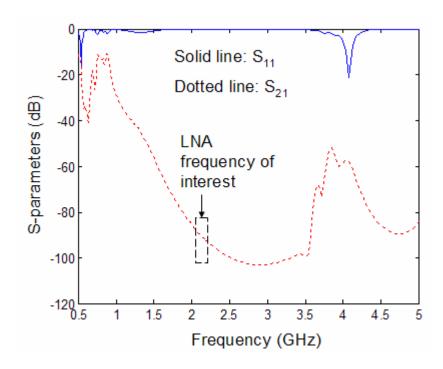

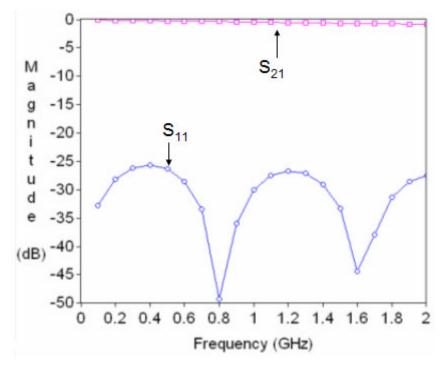

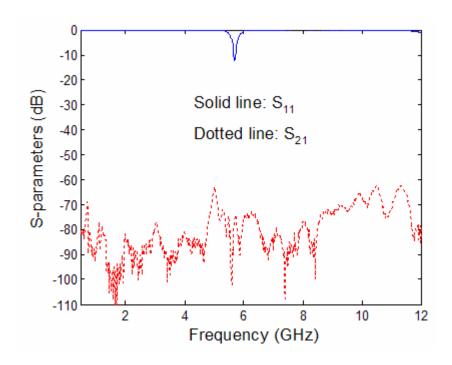

| Figure 5.4 Simulated S-parameters for the AI-EBG based PDN                                                                                                                                                                                        |

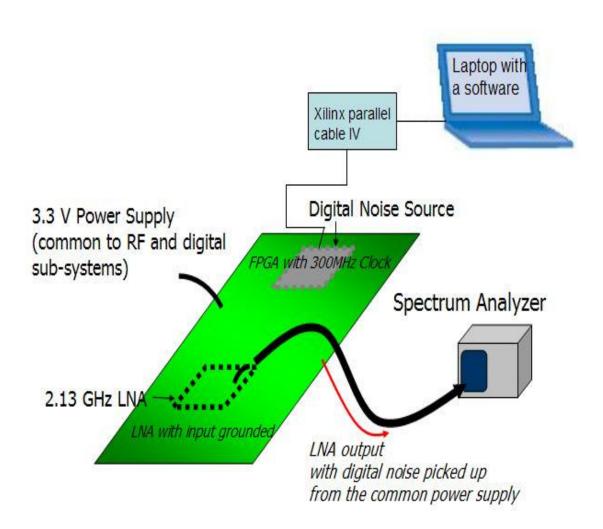

| Figure 5.5 Measurement set-up for noise measurements                                                                                                                                                                                              |

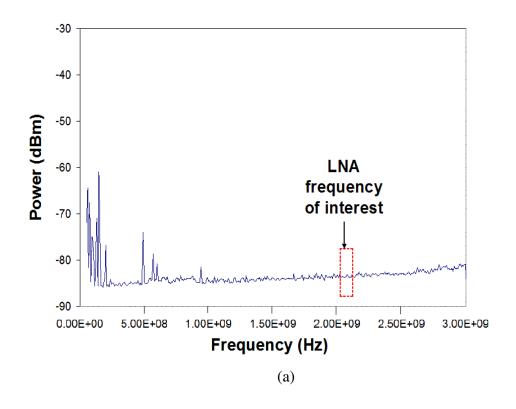

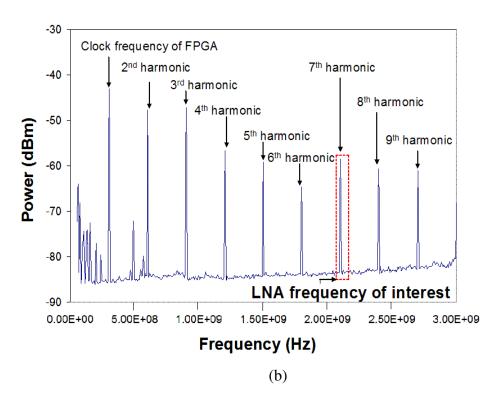

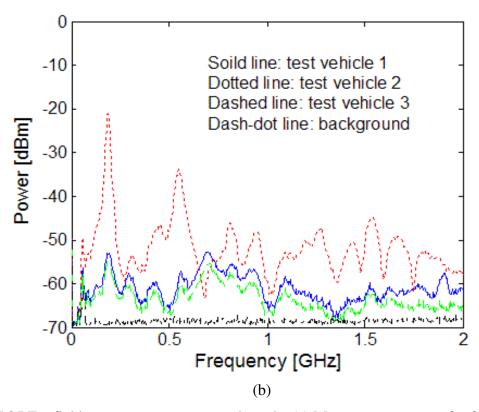

| Figure 5.6 Measured output spectrum of the LNA (a) When the FPGA is completely switched off and (b) When the FPGA is switched on                                                                                                                  |

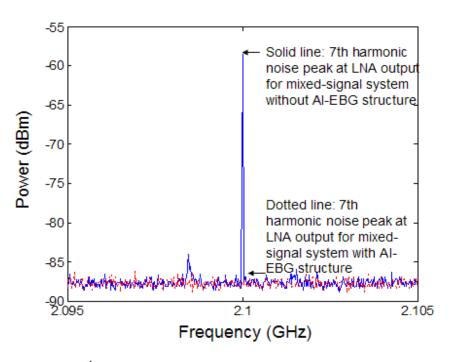

| Figure 5.7 Measured 7 <sup>th</sup> harmonic noise peaks at 2.1 GHz for the test vehicle with and without the AI-EBG structure                                                                                                                    |

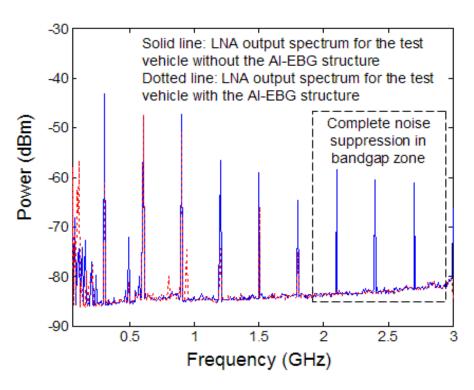

| Figure 5.8 Measured LNA output spectrum for the test vehicles with and without the AI-EBG structure                                                                                                                                               |

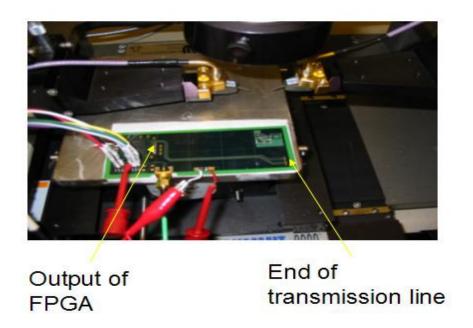

| Figure 5.9 Waveform measurement at two locations on the mixed-signal board 135                                                                                                                                                                    |

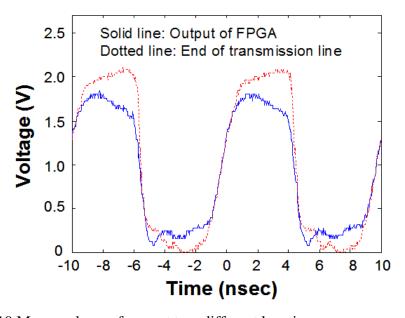

| Figure 5.10 Measured waveforms at two different locations                                                                                                                                                                                         |

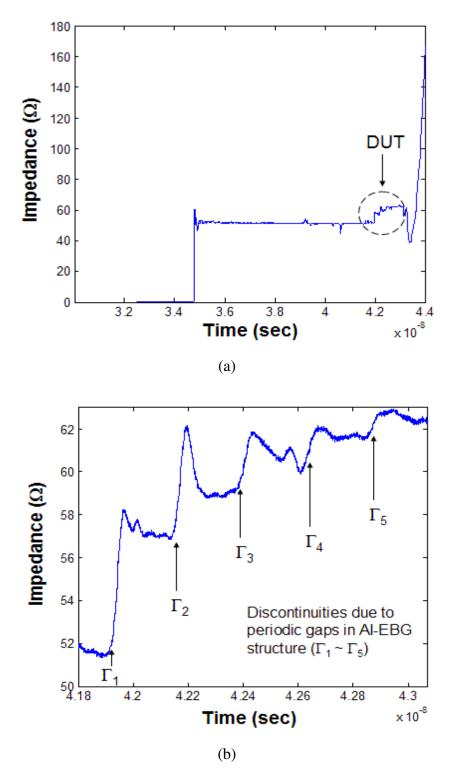

| Figure 5.11 Measured characteristic impedance profile of the first transmission line over AI-EBG structure in the mixed-signal system (a) Characteristic impedance profile of the first transmission line over AI-EBG structure and (b) Magnified |

| characteristic impedance profile of the first transmission line over AI-EBG structure                                                                                                                                                                     | 37  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

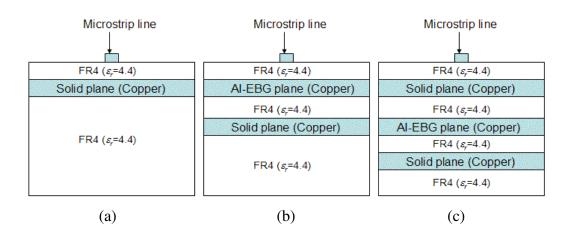

| Figure 5.12 Cross section of the three test vehicle (a) Test vehicle 1 is a microstrip line of a solid plane, (b) Test vehicle 2 is a microstrip line on an AI-EBG structure, and (c) Test vehicle 3 is a microstrip line on an embedded AI-EBG structure |     |

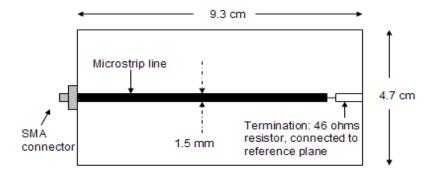

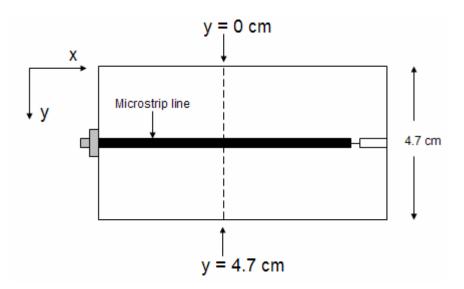

| Figure 5.13 Top view of the test vehicles                                                                                                                                                                                                                 | 11  |

| Figure 5.14 Standing wave patterns on reference plane of the test vehicle 1 (a) resonance pattern at 800 MHz, (b) 2 <sup>nd</sup> resonance pattern at 1.6 GHz, and (3 <sup>rd</sup> resonance pattern at 2.4 GHz                                         | [c] |

| Figure 5.15 S-parameter simulation results of the microstrip line                                                                                                                                                                                         | 42  |

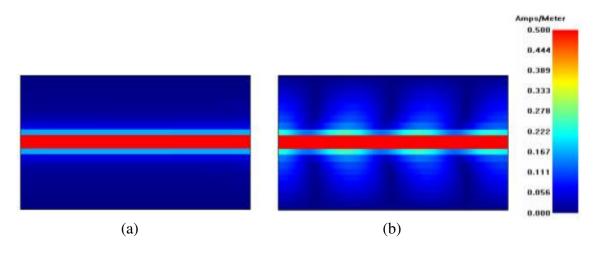

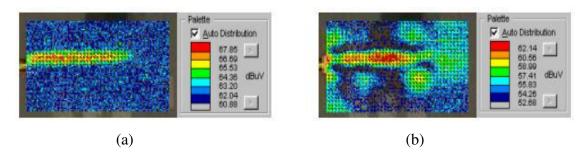

| Figure 5.16 Current density simulation results for test vehicle 1 (a) Current density at 30 MHz and (b) Current density at 2.7 GHz                                                                                                                        |     |

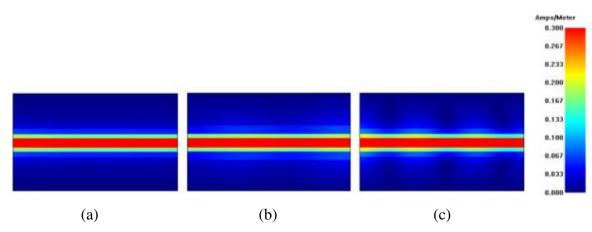

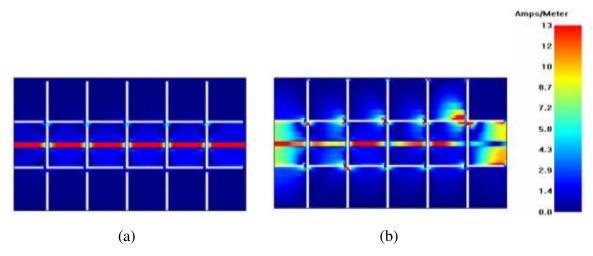

| Figure 5.17 Current density simulation results for test vehicle 2 (a) Current density at 30 MHz and (b) Current density at 2.7 GHz                                                                                                                        |     |

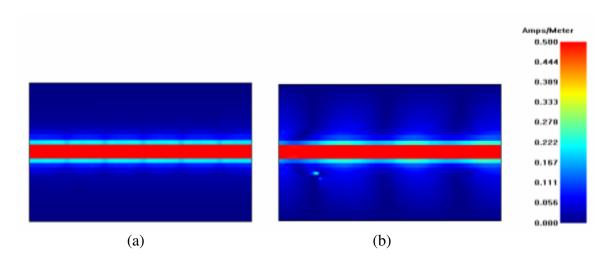

| Figure 5.18 Current density simulation results for test vehicle 3 (a) Current density at 30 MHz and (b) Current density at 2.7 GHz                                                                                                                        |     |

| Figure 5.19 Schematic of y component of the magnetic field at 12 mm above to microstrip line                                                                                                                                                              |     |

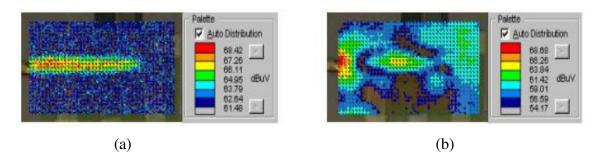

| Figure 5.20 Near field measurement results for the test vehicle 1 (a) Magnetic field intensity at 300 MHz and (b) Magnetic field intensity at 2.7 GHz 14                                                                                                  | .6  |

| Figure 5.21 Near field measurement results for the test vehicle 2 (a) Magnetic field intensity at 300 MHz and (b) Magnetic field intensity at 2.7 GHz                                                                                                     | -6  |

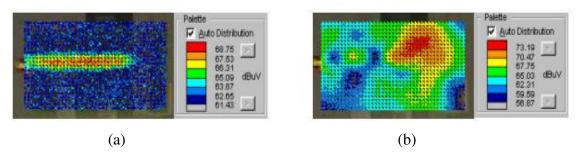

| Figure 5.22 Near field measurement results for the test vehicle 3 (a) Magnetic field intensity at 300 MHz and (b) Magnetic field intensity at 2.7 GHz14                                                                                                   | 17  |

| Figure 5.23 Far field simulation set-up                                                                                                                                                                                                                   | 48  |

| Figure 5.24 Far field simulation results (a) Test vehicle 1 (a solid plane as a reference plane), (b) Test vehicle 2 (an AI-EBG plane as a reference plane), and (c) Te vehicle 3 (a solid plane in an embedded AI-EBG structure as a reference plane)    |     |

| Figure 5.25 Far field measurement set-up and results (a) Measurement set-up for far field measurement results                                                                                                                                             |     |

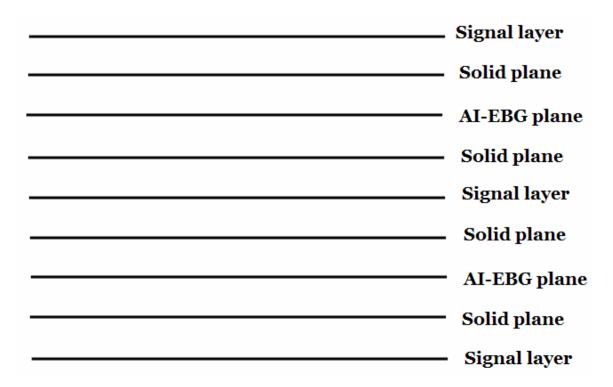

| Figure 5.20 | 6 Plane stack-up for avoiding possible problems related to signal integrity and EMI                                              |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.2  | 7 Plane stack-up for multilayer structure for avoiding possible problems related to signal integrity and EMI                     |

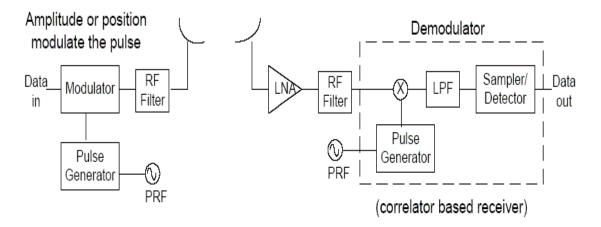

| Figure 6.1  | Ultra wide band (UWB) transceiver architecture                                                                                   |

| Figure 6.2  | Schematic of simulated novel hybrid AI-EBG structure and simulated results of S-parameters for the novel hybrid AI-EBG structure |

| Figure 6.3  | Compact hybrid AI-EBG structure for UWB applications                                                                             |

| Figure 6.4  | Simulated results of S-paramters for the hybrid AI-EBG structure (a) From DC to 11 GHz and (b) From 3 GHz to 11 GHz              |

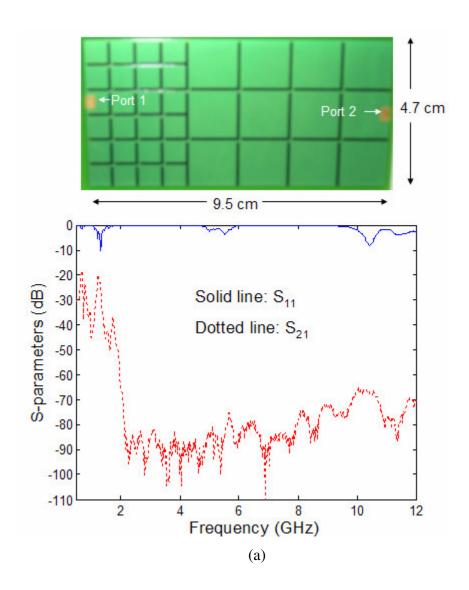

| Figure 6.5  | Photographs of the fabricated hybrid AI-EBG structures and their measured S-parameter results                                    |

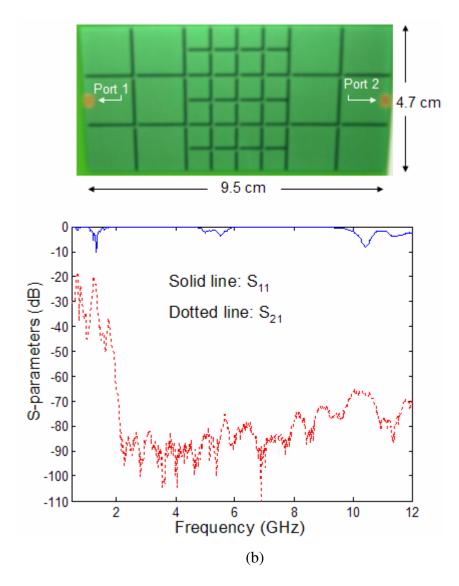

| Figure 6.6  | Photograph of the compact hybrid AI-EBG structure and its measured S-parameter results                                           |

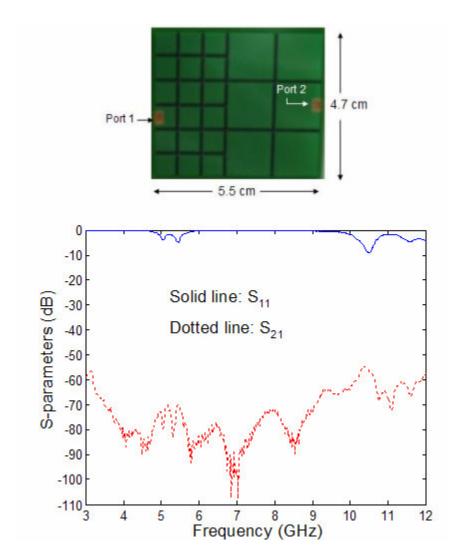

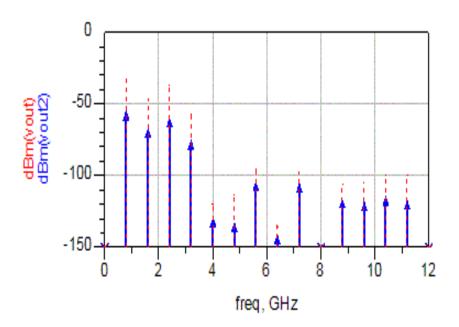

| Figure 6.7  | Mixed-signal system simulation results for UWB application                                                                       |

| Figure 6.8  | Photography of novel structure for ultimate isolation                                                                            |

| Figure 6.9  | Measured S-parameter results for the structure in Figure 6.8                                                                     |

#### **SUMMARY**

With the evolution of technologies, mixed-signal system integration is becoming necessary for combining heterogeneous functions such as high-speed processors, radio frequency (RF) circuits, memory, microelectromechanical systems (MEMS), sensors, and optoelectronic devices. This kind of integration is required for convergent microsystems that support communication and computing capabilities in a tightly integrated module. A major bottleneck with such heterogeneous integration is the noise coupling between the dissimilar blocks constituting the system. The noise generated by the high-speed digital circuits can couple through the power distribution network (PDN) and this noise can transfer to sensitive RF circuits, completely destroying the functionality of noise-sensitive RF circuits.

One common method used for mixed-signal integration in the package is splitting the power and/or ground planes. The gap in the power and ground planes can partially block the propagation of electromagnetic waves. However, electromagnetic energy can still couple through the split, especially at frequencies greater than 1 GHz. The AI-EBG structure in this dissertation has been developed to suppress unwanted noise coupling in mixed-signal systems and this AI-EBG structure shows excellent isolation (-80 dB ~ -140 dB), which results in a noise coupling-free environment in mixed-signal systems. The AI-EBG structure would be part of the power distribution network (PDN) in systems and is expected to have a significant impact on noise suppression and isolation in mixed-signal systems in the future.

## **CHAPTER 1**

# **INTRODUCTION**

The integration of wireless technologies in handsets and mobile computers is forcing the integration of high-speed digital circuits with analog and radio frequency (RF) circuits. When the output drivers or internal logic circuits of a microprocessor switch simultaneously, the power supply noise generated from the noisy digital circuits can deteriorate the performance of sensitive RF/analog circuits. RF front-end circuits like low noise amplifiers (LNAs) need to detect low-power signals, and are extremely sensitive in nature. A large noise spike in or close to the operating frequency band of the device can de-sensitize the circuit, destroying its functionality. To prevent this, all radio architectures include filters and other narrow band circuits, which prevent the noise in the incoming spectrum from reaching the LNA. However, there are no systematic means for filtering noise from other sources – for example, noise can couple through the power rail and appear at the output of the LNA, where it can degrade the performance of the downstream circuits. Thus, an efficient noise suppression technique is required for isolating sensitive RF/analog circuits from noisy digital circuits.

The sensitivity of RF/analog circuits to power supply noise has resulted in difficulties for integration of digital and RF/analog subsystems. One common method used for mixed-signal integration in the package is splitting the power and/or ground planes [1]. The gap in the power and ground planes can partially block the propagation of electromagnetic waves. For this reason, split planes are usually used to isolate sensitive

RF/analog circuits from noisy digital circuits. However, electromagnetic energy can still couple through the split [10], especially at frequencies greater than 1 GHz. Hence, this method only provides marginal isolation (-20 dB ~ -60 dB) at frequencies above ~ 1 GHz and becomes ineffective as system operating frequency increases. Further, as systems become more and more compact, use of multiple power supplies becomes expensive. The use of ferrite beads across the split can result in a common power supply; however, since ferrite beads resonate above 200 MHz, the coupling between split islands increases at higher frequencies. The power segmentation method was proposed recently in [13], [14] but this method only provides good isolation at high frequencies over a narrow frequency band and since this narrow frequency band is fixed by the size of the structure, this frequency band is not tunable. Hence, the development of noise isolation methods is required for enabling integration of mixed-signal systems.

The focus of this dissertation is on noise suppression and isolation in mixed-signal systems using a novel electromagnetic bandgap (EBG) structure called alternating impedance EBG (AI-EBG) structure. The AI-EBG structure in this dissertation has been developed to suppress unwanted noise coupling in mixed-signal systems and this AI-EBG structure shows excellent isolation (-80 dB ~ -140 dB), which results in a noise coupling-free environment in mixed-signal systems. The AI-EBG structure would be part of the power distribution network (PDN) in systems and is expected to have a significant impact on noise suppression and isolation in future mixed-signal systems.

### 1.1 Power distribution network (PDN)

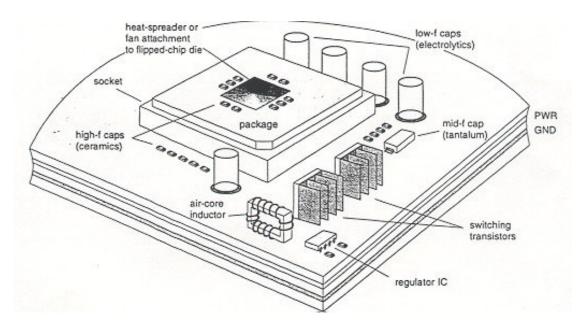

A power distribution network (PDN) is used to deliver power to core logic and I/O circuits in any semiconductor system. The PDN for the typical high-speed digital system is shown in Figure 1.1 and consists of power and ground planes in the board, power and ground planes in the package, a switching regulator, and decoupling capacitors. The PDN supplies drivers (switching circuits) that generate signals and receivers that receive the signals, with voltage and current to function. With advances in silicon technology, power supply voltage has reduced according to the scaling rules while the amount of power required has increased with every computer generation. As a result, the current delivery requirement for the power distribution network has increased greatly and the tolerance for the power supply noise has decreased. It has been recognized that the power supply noise induced by large numbers of simultaneously switching circuits in the power distribution network can limit their performance [1]-[5].

Figure 1.1 Power distribution network for the typical high-speed digital system [1].

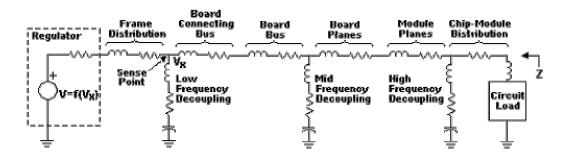

Figure 1.2 shows the electrical equivalent circuit of the PDN, which can be mapped from the mechanical structure of the system in Figure 1.1 [1]. For a superior design of the power distribution network, the impedance of the power/ground planes should be designed to be as low as possible over the entire bandwidth of the signal [8]. As a result, the frequency-dependent driving point impedance (Z) of the PDN at the circuit terminals shown in Figure 1.2 should be kept very small compared to the impedance of the circuit load of each chip to avoid large voltage drops in the PDN.

Figure 1.2 Equivalent circuit diagram for power distribution network [1].

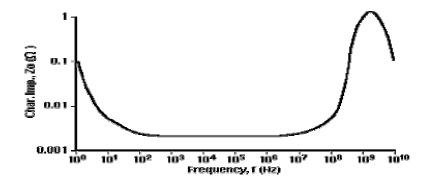

A typical output impedance plot for the PDN looking back from the circuit loads is shown in Figure 1.3 [1]. At low frequencies, a power distribution network acts as a capacitor. In the mid-frequency range, a good network should behave as a transmission line with very low characteristic impedance, with the latter being orders of magnitude lower than the impedance of the circuit load. As the frequency increases beyond the mid-frequency range, the network has an inductive behavior with multiple resonant frequencies.

Figure 1.3 Output impedance for the typical power distribution network [1].

Since the fast switching speed of the digital circuits results in sudden current demand, noise generated can degrade system performance [1]-[6]. A major source of this noise can be attributed to the power distribution network (PDN) of the package and board. For future high-speed digital systems, one method to suppress noise is to design the PDN by identifying a target impedance [8], which has to be met over a broad frequency range. Based on the allowed ripple on the power supply rails, the target impedance for the PDN can be computed as

$$Z_{t \text{ arget}} = \frac{V_{dd} \times 0.05}{I} \tag{1.1}$$

where  $V_{dd}$  is a power supply voltage, I is the current, 0.05 is the 5 % ripple voltage allowed. Using the above equation, the target impedance for various cases can be computed as in Table 1.1. For example, in 2005, a target impedance of 0.48 m $\Omega$  is required using (1.1). Based on the International Technology Roadmap for Semiconductors (ITRS) voltage and power projections, the target impedance is expected to reduce by a factor of 2 per computer generation, with a target impedance requirement of 0.06 m $\Omega$  in the year 2016. This is 16 times lower than the 0.93 m $\Omega$  required in 2001.

Since transient currents cause voltage fluctuations, a high-speed digital system has to meet the target impedance over a broad bandwidth (at least from DC to 5 GHz in 2005). In addition to suppressing noise by maintaining a small self-impedance, a small target transfer impedance is also required between the processor and noise-sensitive areas of the system.

Several major components are currently used to meet the target impedance over the wide frequency range. The voltage regulator module (VRM) is effective up to about 1 kHz. Bulk capacitors supply current and maintain a low PDN impedance from 1 kHz to 1 GHz. High frequency ceramic capacitors maintain the PDN impedance from 1 MHz to 1

Table 1.1 Target impedance tendency and projection based on ITRS 2001

| Year | Power (W) | Vdd (V) | Current (A) | Frequency | $Z_{\text{target}} \left( \text{m}\Omega \right)$ |

|------|-----------|---------|-------------|-----------|---------------------------------------------------|

|      |           |         |             | (MHz)     |                                                   |

| 1991 | 5         | 5       | 1           | 16        | 500                                               |

| 1996 | 25        | 2.6     | 10          | 300       | 27                                                |

| 2001 | 130       | 1.1     | 118         | 1700      | 0.93                                              |

| 2003 | 150       | 1.0     | 150         | 3090      | 0.67                                              |

| 2005 | 170       | 0.9     | 189         | 5170      | 0.48                                              |

| 2007 | 190       | 0.7     | 271         | 6740      | 0.26                                              |

| 2010 | 218       | 0.6     | 363         | 12000     | 0.17                                              |

| 2013 | 251       | 0.5     | 502         | 19000     | 0.1                                               |

| 2016 | 288       | 0.4     | 720         | 29000     | 0.06                                              |

GHz [74]. Electromagnetic bandgap (EBG) structures have been suggested to meet the target impedance goals over 1 GHz [26].

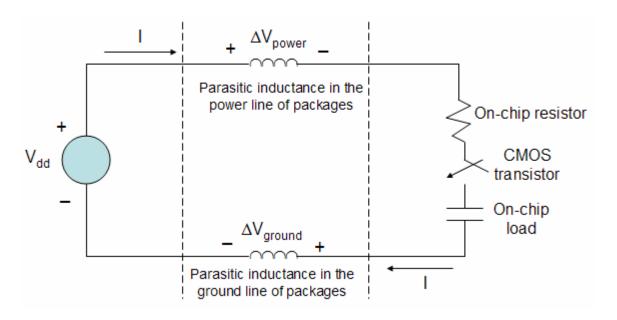

### 1.2 Simultaneous Switching Noise (SSN)

Simultaneous switching noise (SSN) refers to a noise fluctuation or voltage glitch generated in a digital system due to rapid changes in current caused by switching of many circuits in the system at the same time [32]. SSN is also referred to as "delta-I" noise because of its direct dependence on the rate of change of current or called "ground bounce" since the voltage glitch corresponds to an effective change of the power supply voltage and therefore can be seen as a shift in the internal ground reference voltage level. With recent advances in CMOS technology resulting in a faster device switching speed and higher package density, simultaneous switching noise (SSN) induced by a large number of internal and external switching circuits has become a critical issue in highspeed digital systems. SSN is mainly caused by inductance in the PDN associated with the board, package, and chip. Figure 1.4 shows an equivalent circuit for the system where the package and printed circuit board (PCB) metal layers add inductance to the power distribution network [2]. In this system, the voltage and current to the chip are supplied from a power supply on the motherboard through the metal layers on the package and PCB. The local supply on the chip acts as a non-ideal supply, primarily because the route taken by the power supply current through the board, package, and chip introduces a series inductance L into the system. There is a serious side effect of series inductance in the power supply circuitry. Whenever the power supply current changes in the presence of series inductance, the local  $V_{dd}$  level will drop since the current flowing through an

inductor cannot change instantaneously. Consequently, the transient supply currents flowing through these interconnections cause voltage fluctuations on the power supply rails of the chip. This voltage fluctuation, which is referred to as SSN, is given by:

$$\Delta V_{SSN} = NL_{eff} \frac{di}{dt} \tag{1.2}$$

where N is the number of simultaneously switching drivers,  $L_{eff}$  is the effective inductance of the power distribution network, and di/dt is the current slew rate of a single driver.

It is important to note that the effective inductance can be defined only for a loop of current. As shown in (1.2), the SSN is directly proportional to the current slew rate and

Figure 1.4 Equivalent circuit for the system where the package and printed circuit board (PCB) metal layers add inductance to the power distribution network [2].

the effective inductance. As a result, controlling the total allowed system noise requires controlling either the driver's slew rate or the effective inductance. However, the control

of the driver's slew rate requiring driver slowdown is not adequate because it adds delay to the driver output and can ultimately increase the machine cycle time. Hence, reducing the effective inductance is the proper solution. In the next section, traditional and advanced methods using decoupling capacitors to mitigate SSN are discussed.

### 1.3 Discrete and Embedded Decoupling Capacitors

A traditional method to suppress SSN is through decoupling capacitors on the board, package, and chip. Decoupling capacitors are connected between the power and the ground planes in order to lower the impedance of the power distribution network as well as supply current bursts for fast switching circuits [70]-[72].

To support the peak current needs of fast switching circuits, decoupling capacitors accumulate charge over the clock cycle, and then rapidly discharge during fast transitions. Power supplies cannot fulfill this role since voltage regulators respond too slowly and since the regulators are typically too far away. Decoupling capacitors provide fast switching drivers with extra current required to charge the load capacitor instead of the power supply. As a result, the power supply noise is reduced since the inductive effect in the loop current path is decreased by the decoupling capacitors.

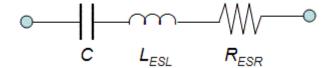

The decoupling capacitors are expected to behave as a short circuit between the power/ground planes at high frequencies. However, it has been found that the parasitic inductance of the leads and mounting pads of the decoupling capacitors strongly limits their power supply noise mitigation ability [26]. In fact, the decoupling capacitor behaves as a series RLC resonant circuit, which becomes close to a short circuit only around its self-resonant frequency. As a result, the decoupling capacitor can be represented as a

series RLC circuit, as shown in Figure 1.5, and the impedance of the decoupling capacitor can be represented by the following equation:

$$Z_{real\_decap} = R_{ESR} + j\omega L_{ESL} + \frac{1}{j\omega C}$$

(1.3)

where  $Z_{real\_decap}$  is the impedance of real decoupling capacitor,  $R_{ESR}$  is the equivalent series resistance (ESR),  $L_{ESL}$  is the equivalent series inductance (ESL), C is the capacitance, and  $\omega = 2\pi f$  is the angular frequency.

Figure 1.5 Model of the real decoupling capacitor.

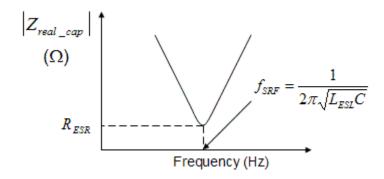

The self-resonant frequency of the real decoupling capacitor is given by

$$f_{SRF} = \frac{1}{2\pi\sqrt{L_{ESI}C}} \tag{1.4}$$

at which the reactive impedances are cancelled and the impedance of the decoupling capacitor has a magnitude of  $R_{ESR}$ , which is the minimum magnitude of the impedance, as shown in Figure 1.6.

Due to this kind of characteristic of the decoupling capacitors, different kinds of decoupling capacitors should be used over the wide frequency range, depending on the package structure. Based on the resonant frequency, the decoupling capacitors can be categorized into low-frequency, mid-frequency, and high-frequency capacitors, and incorporated at appropriate places throughout the system, as shown in Figure 1.1, for

Figure 1.6 Typical response of a decoupling capacitor.

filtering the frequency components of current changes caused by circuit switching.

Typically, low-frequency and mid-frequency decoupling capacitors are mounted on the package and board, and high-frequency decoupling capacitors for f > 1GHz are buried in the chip as trench capacitors. However, it should be noted that it is almost impossible to lower the impedance of the PDN at frequencies greater than 1 GHz using decoupling capacitors since the parasitic inductance of the decoupling capacitor is dominant at high frequencies.

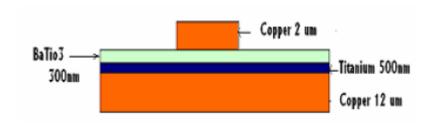

In general, the decoupling capacitors can be either discrete or embedded. The decoupling capacitors mentioned above are discrete decoupling capacitors. The embedded capacitors provide better high-frequency performance since they have less parasitic inductance but cannot suppress the intrinsic modes of the parallel-plate waveguide, which will be discussed in the next section. Another disadvantage of the embedded capacitors is that the process for the embedded capacitors is not standardized

and therefore the process can be a high-cost process. For example, Figure 1.7 shows the cross section of Barium Titanate (BaTiO<sub>3</sub>) capacitor that was developed at the Packaging Research Center (PRC) at Georgia Tech. This embedded capacitor was fabricated using a hydrothermal process. In this process, nanograined ultra thin crystalline Barium Titanate thin films were synthesized on laminated copper foils using the low cost low temperature (< 100 °C) hydrothermal process. Hydrothermal synthesis of BaTiO<sub>3</sub> involves treating Ti-coated copper clad laminates with Ba2+ ions in highly alkaline solution at 95 °C. With this method high k thin films can be integrated into organic packages using standard printed wiring board processes such as lamination and lithography [73].

Figure 1.7 Cross section of BaTiO<sub>3</sub> capacitor [73].

#### 1.4 Power/Ground Planes

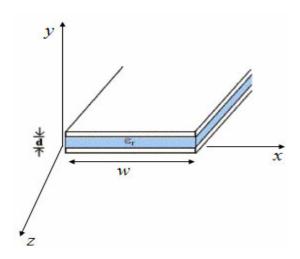

The power/ground plane pair in a power distribution network behaves like a parallel-plate waveguide at high frequencies. A time-varying current flowing through vias in the PDN due to switching of the digital circuit causes the excitation of electromagnetic (EM) waves, which propagates between power and ground planes in the package and board. These waves reflect from the edges in the power distribution network

of the package and board and cause resonances over the frequency range, which increases the impedance magnitude of PDN at certain resonant frequencies. Hence, it is important to analyze the power/ground plane pair as a parallel-plate waveguide. The parallel-plate waveguide can support transverse electromagnetic (TEM), transverse magnetic (TM), and transverse electric (TE) waves, in addition to cavity resonator modes.

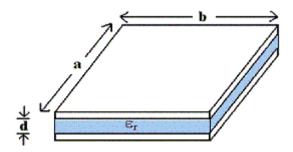

Consider a parallel-plate waveguide consisting of two perfectly conducting plates separated by a dielectric material as shown in Figure 1.8. The dimensions in the x and z directions are assumed to be much larger than the dielectric thickness d, which makes fringing fields on the edges of the structure and any variation in the x direction neglected.

Figure 1.8 Parallel-plate waveguide.

## **1.4.1 Transverse Electromagnetic (TEM) Waves**

Transverse electromagnetic (TEM) waves represent waves in which electric and magnetic fields are perpendicular to each other and both are transverse to the direction of wave propagation. For example, if propagation in the z direction, TEM waves are waves

that contain neither  $E_z$  nor  $H_z$  where  $E_z$  is the electric field component in the z direction and  $H_z$  is the magnetic field component in the z direction. The TEM wave solution can be obtained by solving Laplace's equation for the electrostatic potential  $\Phi(x, y)$  between the two conducting plates:

$$\nabla^2 \Phi(x, y) = 0, \qquad \text{for } 0 \le x \le w \text{ and } 0 \le y \le d$$

(1.5)

Assuming that the upper conducting plate has a potential  $V_{dd}$  and lower conducting plate has a potential zero, we get

$$\Phi\left(x,d\right) = V_{dd},\tag{1.6}$$

$$\Phi\left(x,0\right) = 0. \tag{1.7}$$

Since we assume that there is no variation in x direction, the general solution to (1.5) for  $\Phi(x, y)$  is

$$\Phi(x, y) = A_1 + A_2 y, \qquad (1.8)$$

where  $A_1$  and  $A_2$  are unknown constants.

Using the boundary conditions in (1.6) and (1.7), we have

$$\Phi(x,y) = \frac{V_{dd}}{d}y. \tag{1.9}$$

The transverse electric field is then obtained as

$$\bar{E}(x, y, z) = -\nabla \Phi(x, y) e^{-jkz} = -\frac{V_{dd}}{d} e^{-jkz} \hat{y}, \qquad (1.10)$$

where  $k = \omega \sqrt{\mu \varepsilon}$  is the propagation constant of the TEM wave.

Then, magnetic field can be calculated as

$$\bar{H}(x, y, z) = \frac{1}{\eta} \hat{z} \times \bar{E}(x, y, z) = \frac{V_{dd}}{\eta d} e^{-jkz} \hat{x},$$

(1.11)

where  $\eta = \sqrt{\frac{\mu}{\varepsilon}}$  is intrinsic impedance of the dielectric material between two conducting plates.

The voltage V between the two conducting plates can be obtained as

$$V = -\int_{y=0}^{y=d} E_y dy = V_{dd} e^{-jkz}, \qquad (1.12)$$

where  $E_y = -\frac{V_{dd}}{d}e^{-jkz}$ .

The total current flowing on the upper conducting plate can be calculated as

$$I = \int_{x=0}^{x=w} \bar{J}_{S} \cdot z dx = \int_{x=0}^{x=w} (-y \times \bar{H}) \cdot z dx = \frac{wV_{dd}}{\eta d} e^{-jkz},$$

(1.13)

where  $J_s = -\bar{y} \times \bar{H}$  is surface current density on the upper conducting plate.

Hence, the characteristic impedance of the parallel-plate waveguide is given by

$$Z_{0} = \frac{V}{I} = \frac{\eta d}{w}. \tag{1.14}$$

It should be noted that the characteristic impedance of the parallel-plate waveguide depends only on the material parameters and the geometry of the waveguide.

### 1.4.2 Transverse Magnetic (TM) Waves

Transverse magnetic (TM) waves represent waves that do not have a component of the magnetic field in the direction of wave propagation. For example, for propagation along the z direction, TM waves are waves that contain nonzero  $E_z$  but  $H_z = 0$ .

The Helmholtz equation or wave equation for  $\bar{E}$  is given as:

$$\nabla^2 \overline{E} + \omega^2 \mu \varepsilon \overline{E} = 0, \tag{1.15}$$

where  $\mu$  is the permeability of the medium and  $\varepsilon$  is the permittivity of the medium.

For  $E_z$ , the Helmholtz equation can be written as

$$\left(\frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2} + \frac{\partial^2}{\partial z^2} + k^2\right) E_z = 0, \tag{1.16}$$

where  $k = \omega \sqrt{\mu \varepsilon}$  is the propagation constant of the medium.

Since  $E_z(x, y, z) = e_z(x, y)e^{-j\beta z}$ , equation (1.16) can be reduced to a two-dimensional wave equation for  $e_z$  as:

$$\left(\frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2} + k_c^2\right) e_z(x, y) = 0, \tag{1.17}$$

where  $k_c^2 = k^2 - \beta^2$ .

Since the dimension in the x direction is assumed to be much larger than the dielectric thickness d, making any variation in the x direction neglegible (i.e.,  $\frac{\partial}{\partial x} = 0$ ), equation (1.17) becomes

$$(\frac{\partial^2}{\partial y^2} + k_c^2)e_z(x, y) = 0.$$

(1.18)

The general solution to equation (1.18) is of the following form

$$e_z(x, y) = A_1 \sin k_c y + A_2 \cos k_c y.$$

(1.19)

Applying the boundary conditions that  $e_z(x, y)$  should be zero at y = 0 and d, we obtain

$$A_2 = 0$$

and  $k_c = \frac{n\pi}{d}$ ,  $n = 0, 1, 2 ...$  (1.20)

Hence, the electric field in the z direction can be written as

$$E_z(x, y, z) = A_n \sin \frac{n\pi y}{d} e^{-j\beta z}$$

(1.21)

The transverse field components can be derived as follows:

$$H_{x} = \frac{j\omega\varepsilon}{k_{c}^{2}} \frac{\partial E_{z}}{\partial y} = \frac{j\omega\varepsilon A_{n}}{k_{c}} \cos\frac{n\pi y}{d} e^{-j\beta z}, \qquad (1.22)$$

$$H_{y} = -\frac{j\omega\varepsilon}{k_{c}^{2}} \frac{\partial E_{z}}{\partial x} = 0, \tag{1.23}$$

$$E_x = -\frac{j\beta}{k_z^2} \frac{\partial E_z}{\partial x} = 0, \tag{1.24}$$

$$E_{y} = -\frac{j\beta}{k_{c}^{2}} \frac{\partial E_{z}}{\partial y} = -\frac{j\beta A_{n}}{k_{c}} \cos \frac{n\pi y}{d} e^{-j\beta z}.$$

(1.25)

For n=0,  $E_z=0$  and  $\beta=k=\omega\sqrt{\mu\varepsilon}$ , which means that  $TM_0$  mode is identical to the TEM mode for the parallel-plate waveguide. For  $n\geq 1$ , each n corresponds to a different  $TM_n$  mode with its propagation constant given by

$$\beta = \sqrt{k^2 - k_c^2} = \sqrt{k^2 - \left(\frac{n\pi}{d}\right)^2}.$$

(1.26)

For a TM wave to propagate, its propagation constant should be real, which requires that the wave number, k, be larger than the cut-off wave number,  $k_c$ . Thus, the cut-off frequency for the TM<sub>n</sub> mode can be defined as

$$f_c = \frac{k_c}{2\pi\sqrt{\mu\varepsilon}} = \frac{n}{2d\sqrt{\mu\varepsilon}}.$$

(1.27)

Hence, the lowest TM mode is TM<sub>1</sub> mode with a cut-off frequency of  $f_c = \frac{1}{2d\sqrt{\mu\varepsilon}}$ . All

higher order modes have cut-off frequencies equal to multiples of this cut-off frequency.

The wave impedance of the TM modes is given by

$$Z_{\scriptscriptstyle TM} = -\frac{E_{\scriptscriptstyle y}}{H_{\scriptscriptstyle x}} = \frac{\beta}{\omega \varepsilon} = \frac{\beta \eta}{k} = \eta \sqrt{1 - \left(\frac{\omega_{\scriptscriptstyle c}}{\omega}\right)^2}.$$

(1.28)

It is important to note that wave impedances are purely real for  $f > f_c$  but purely imaginary for  $f < f_c$ . The phase velocity can be written as

$$v_{p} = \frac{\omega}{\beta} = \frac{c}{\sqrt{1 - \left(\frac{\omega_{c}}{\omega}\right)^{2}}}.$$

(1.29)

It should be noted that the phase velocity is a function of frequency. The group velocity is given by

$$v_{g} = \frac{d\omega}{d\beta} = c\sqrt{1 - \left(\frac{\omega_{c}}{\omega}\right)^{2}}.$$

(1.30)

#### 1.4.3 Transverse Electric (TE) Waves

Transverse electric (TE) waves represent waves that do not have a component of the electric field in the direction of propagation. For example, for a wave propagating in the z direction, TE waves contain nonzero  $H_z$  but  $E_z = 0$ .

The Helmholtz equation or wave equation for  $\bar{H}$  is given as:

$$\nabla^2 H + \omega^2 \mu \varepsilon H = 0. \tag{1.31}$$

For  $H_z$ , the Helmholtz equation can be written as

$$\left(\frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2} + \frac{\partial^2}{\partial z^2} + k^2\right)H_z = 0,$$

(1.32)

where  $k = \omega \sqrt{\mu \varepsilon}$  is the propagation constant of the medium.

Since  $H_z(x, y, z) = h_z(x, y)e^{-j\beta z}$ , equation (1.16) can be reduced to a two-dimensional wave equation for  $h_z$ :

$$\left(\frac{\partial^2}{\partial x^2} + \frac{\partial^2}{\partial y^2} + k_c^2\right) h_z(x, y) = 0, \tag{1.33}$$

where  $k_c^2 = k^2 - \beta^2$ .

Since the dimension in the x direction is assumed to be much larger than the dielectric thickness d, making any variation in the x direction neglegible (i.e.,  $\frac{\partial}{\partial x} = 0$ ), equation (1.17) becomes

$$\left(\frac{\partial^2}{\partial y^2} + k_c^2\right) h_z(x, y) = 0. \tag{1.34}$$

The general solution to equation (1.18) is of the following form:

$$h_z(x, y) = A_1 \sin k_c y + A_2 \cos k_c y.$$

(1.35)

The electric field component,  $E_x$ , can be calculated as

$$E_x(x, y, z) = -\frac{j\omega\mu}{k_c^2} \frac{\partial H_z}{\partial y} = -\frac{j\omega\mu}{k_c} (A_1 \cos k_c y - A_2 \sin k_c y) e^{-j\beta k}.$$

(1.36)

Applying the boundary conditions that  $E_x$  should be zero at y = 0 and d, we obtain

$$A_2 = 0$$

and  $k_c = \frac{n\pi}{d}$ ,  $n = 1, 2 ...$  (1.37)

Hence, the magnetic field in the z direction can be written as

$$H_{z}(x, y, z) = A_{n} \cos \frac{n\pi y}{d} e^{-j\beta z}.$$

(1.38)

The transverse field components can be derived as follows:

$$H_{x} = -\frac{j\beta}{k_{z}^{2}} \frac{\partial H_{z}}{\partial x} = 0, \tag{1.39}$$

$$H_{y} = -\frac{j\beta}{k_{z}^{2}} \frac{\partial H_{z}}{\partial y} = \frac{j\beta A_{n}}{k_{z}} \sin \frac{n\pi y}{d} e^{-j\beta z}, \qquad (1.40)$$

$$E_{x} = -\frac{j\omega\mu}{k_{c}^{2}} \frac{\partial H_{z}}{\partial y} = \frac{j\omega\mu A_{n}}{k_{c}} \sin\frac{n\pi y}{d} e^{-j\beta z}, \qquad (1.41)$$

$$E_{y} = -\frac{j\omega\mu}{k_{c}^{2}} \frac{\partial H_{z}}{\partial x} = 0.$$

(1.42)

The propagation constant of the TE<sub>n</sub> mode is given by

$$\beta = \sqrt{k^2 - k_c^2} = \sqrt{k^2 - \left(\frac{n\pi}{d}\right)^2}.$$

(1.43)

It should be noted that the propagation constant of the  $TE_n$  mode is the same as that of the  $TM_n$  mode. The cut-off frequency for the  $TE_n$  mode can be defined as

$$f_c = \frac{k_c}{2\pi\sqrt{\mu\varepsilon}} = \frac{n}{2d\sqrt{\mu\varepsilon}}.$$

(1.44)

Hence, the lowest TE mode is the TE<sub>1</sub> mode with a cut-off frequency of  $f_c = \frac{1}{2d\sqrt{u\varepsilon}}$ .

All higher modes have cut-off frequencies equal to multiples of this cut-off frequency.

The wave impedance of the TE modes is given by

$$Z_{TE} = \frac{E_x}{H_y} = \frac{\omega \mu}{\beta} = \frac{k\eta}{\beta} = \frac{\eta}{\sqrt{1 - \left(\frac{\omega_c}{\omega}\right)^2}}.$$

(1.45)

#### 1.4.4 Cavity Resonator Modes

Power/ground planes represent large metal layers separated by a small dielectric distance, as shown in Figure 1.9. Due to the small dielectric distance, power/ground planes in the package and PCB are capacitive at low frequencies and are therefore ideal

for supplying power to the integrated circuits. However, with increasing frequency, planes become inductive and resonate at discrete frequencies [1]. Conventional power

Figure 1.9 Schematic of power/ground planes in package and board.

and ground planes have a dielectric thickness of less than 100 mils and the dielectric thickness is becoming thinner with advances in technology. The lowest TM and TE modes for the parallel-plate waveguide have cut-off frequencies in the order of hundreds of gigahertz, which implies TM and TE modes of the parallel-plate waveguide are not a major concern for the systems operating at 10 GHz and below. For example, TM<sub>1</sub> and TE<sub>1</sub> modes for the power/ground planes with a dielectric thickness of 4.5 mils occur at 618 GHz by equations (1.27) and (1.44). Therefore, the only modes of concerns are the TEM modes of the parallel-plate waveguide and cavity resonator modes due to the finite size of the power/ground planes [77]. For the modes derived for the parallel-plate waveguide in previous sections, it was assumed that the conducting planes have infinite length in the x and z directions. However, real power and ground planes have finite size of width and length, which means that waves propagating to the edges of the power/ground planes have to be reflected back and forth. These reflections combine to

produce a cavity resonator mode at certain frequencies. The rectangular cavity resonator modes occur at the following frequencies [30]:

$$f_{cavity} = \frac{1}{2\pi\sqrt{\mu\varepsilon}} \sqrt{\left(\frac{m\pi}{a}\right)^2 + \left(\frac{n\pi}{b}\right)^2 + \left(\frac{p\pi}{d}\right)^2},$$

(1.46)

where  $\mu$  is the permeability of a dielectric material,  $\varepsilon$  is the permittivity of a dielectric material, and m, n, and p are mode numbers equal to  $0, 1, 2, \ldots$ , except that at least one of the mode numbers must be nonzero. The parameters a, b, and d are the dimensions in Figure 1.9. In practical power/ground planes, the dielectric thickness d is much smaller than the width (a) and the length (b), which means the standing wave patterns along dimension d will be at frequencies that are ten to hundred of times larger than the resonant frequencies of waves along the width and length of power/ground planes. Hence, the cavity resonant frequencies in equation (1.46) for practical power/ground planes can be obtained with p=0 and written as:

$$f_{cavity} = \frac{1}{2\pi\sqrt{\mu\varepsilon}}\sqrt{\left(\frac{m\pi}{a}\right)^2 + \left(\frac{n\pi}{b}\right)^2} \ . \tag{1.47}$$

# 1.5 Noise Coupling in Mixed-Signal System

With the evolution of technologies, mixed-signal system integration is becoming necessary for combining heterogeneous functions such as high-speed processors, radio frequency (RF) circuits, memory, microelectromechanical systems (MEMS), sensors, and optoelectronic devices. This kind of integration is required for convergent microsystems that support communication and computing capabilities in a tightly integrated module. A

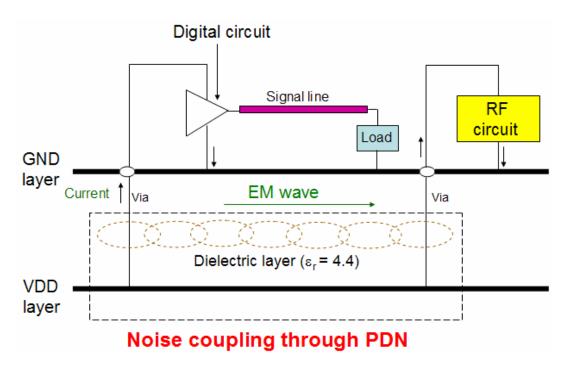

major bottleneck with such heterogeneous integration is the noise coupling between the dissimilar blocks constituting the system [9]. The noise generated by the high-speed digital circuits can couple through the power distribution network (PDN) and this noise can transfer to sensitive RF circuits, completely destroying the functionality of noise-sensitive RF circuits. Figure 1.10 shows the noise coupling mechanism due to electromagnetic (EM) waves in a mixed-signal system. The time-varying current flowing through a via due to switching of the digital circuits can cause the excitation of EM waves.

Figure 1.10 Noise coupling in a mixed-signal system.

Since a power/ground plane pair used to supply power to the switching circuits behaves like a parallel-plate waveguide at high frequencies [30], the EM wave propagates between the power/ground plane pair and couples to the RF circuit, causing failure of the

RF circuit. To prevent this noise coupling, traditional isolation techniques have used split planes with multiple power supplies [10], split planes and ferrite beads with a single power supply [12] and power-plane segmentation [13], [14]. All these methods have two fundamental problems namely, a) they provide poor isolation in the -20 dB to -60 dB range [10] above 1 GHz and b) they provide narrow band capability. Hence, the development of better noise isolation methods for the integration of digital and RF functions is necessary. One method for achieving high isolation over broad frequency range is through the use of electromagnetic band gap (EBG) structures. EBG structures are periodic structures that suppress wave propagation in certain frequency bands while allowing it in others. For power delivery networks, EBG structures can be constructed by patterning the ground plane. In this dissertation, a novel EBG structure based on the alternating impedance (AI-EBG) concept is discussed for use in power delivery networks.

#### 1.6 Current Isolation Methods

Decoupling capacitors are usually used to suppress simultaneous switching noise in digital systems. However, the decoupling capacitors are not good enough for noise suppression and isolation in mixed-signal systems since noise-sensitive RF circuits exist in the systems. Currently, there are three methods for isolating sensitive RF circuits from noisy digital circuits in mixed-signal systems: split planes [10], split planes with ferrite beads [12], and power-plane segmentation [13], [14]. Each of these methods is described in detail.

#### 1.6.1 Split Planes

One typical approach to isolate the sensitive RF/analog circuits from the noisy digital circuits is to split the power plane or both power and ground planes [10]. The gap in power plane or ground plane can partially block the propagation of electromagnetic waves. For this reason, split planes are usually used to isolate sensitive RF/analog circuits from noisy digital circuits. Although split planes can block the propagation of electromagnetic waves, part of the electromagnetic energy can still couple through the gap [10]. Hence, this method only provides a marginal isolation (-20 dB  $\sim$  -60 dB) at high frequencies (usually above  $\sim$  1 GHz) and could create a serious problem as the sensitivity of RF circuits increases and the operating frequency of the system increases. Generally, split planes provide good isolation (-70 dB  $\sim$  -80 dB) at low frequencies (usually below  $\sim$  1 GHz) but show poor isolation (-20 dB  $\sim$  -60 dB) at high frequencies because of electromagnetic coupling. In addition to this, split planes sometimes require separate power supplies to maintain the same DC level, which is not cost effective.

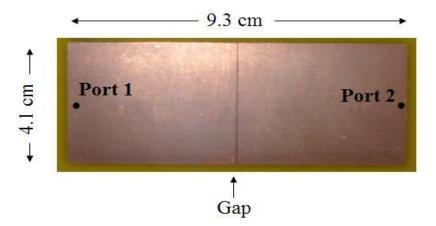

Figure 1.11 Photo of the fabricated split planes.

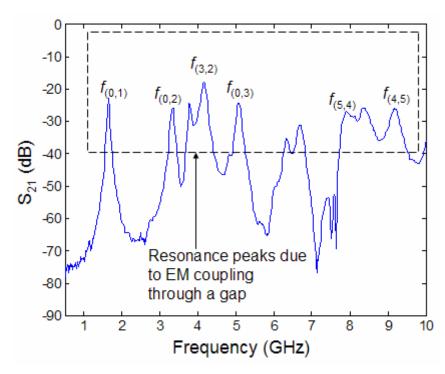

Figure 1.12 Measured transmission coefficient (S21) for the split planes in Figure 1. Some cavity resonator modes are shown by equation (1.10).

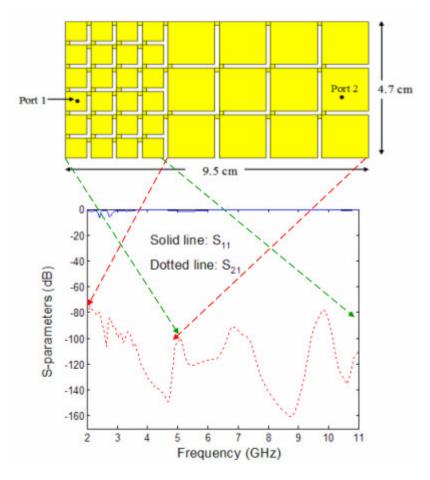

Figure 1.11 shows a fabricated structure containing split planes. The size of the structure is 9.3 cm x 4.1 cm and port 1 and port 2 are located around at the edges. Figure 1.12 shows the measured transmission coefficient ( $S_{21}$ ) between port 1 and port 2. It is clear that split planes show good isolation up to 1 GHz but show poor isolation at high frequencies (over 1 GHz). It is observed in Figure 1.12 that there are many resonance peaks above 1 GHz as a result of EM coupling through the gap. This measurement proves that electromagnetic energy can still couple through the split, especially at frequencies greater than 1 GHz. Hence, this method only provides marginal isolation (-20 dB  $\sim$  -60 dB) at frequencies above  $\sim$ 1.5 GHz, and becomes ineffective as system operating frequency increases. The resonance peaks in Figure 1.12 can be calculated using (1.47) and some cavity resonance modes are shown in Figure 1.12.

#### 1.6.2 Split Planes with Ferrite Beads

Since split planes require multiple power supplies to maintain the same DC level, if that system requires the same DC level, the use of split planes is not cost effective. So, for a system that requires the same DC level, a ferrite bead is placed between the split planes, as shown in Figure 1.13 (a). A ferrite bead is a dowel-like device which has a center holes and is composed of ferromagnetic material. Figure 1.13 (b) shows a ferrite bead. When placed onto a current carrying conductor it acts as an RF choke. It offers a convenient, inexpensive, yet a very effective means of RF shielding, parasitic suppression and RF decoupling. The simple equivalent circuit for a ferrite bead is a single inductor. Since an inductor is a shorted circuit at the DC, a ferrite bead can provide a DC path

Figure 1.13 (a) A ferrite bead between split planes and (b) Photo of a ferrite bead [75].

for the split planes. Hence, a single power supply can be used for the split planes with a ferrite bead. However, a real ferrite bead does not behave like an ideal inductor. Figure 14 shows typical impedance characteristic over a wide frequency range. The impedance

of the ferrite bead starts to drop around 200 MHz, which makes isolation worse after 200 MHz. Hence, this method also cannot provide good isolation at the high frequencies.

Figure 1.14 Typical impedance characteristics of a ferrite bead [75].

#### 1.6.3 Power-plane segmentation method

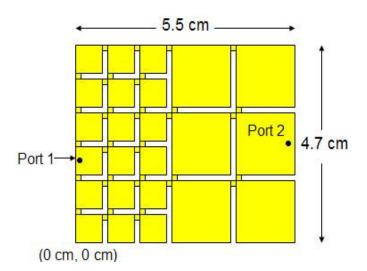

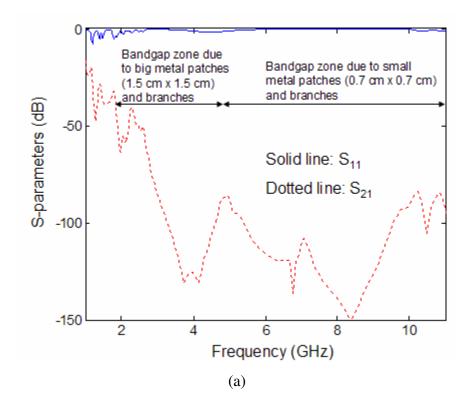

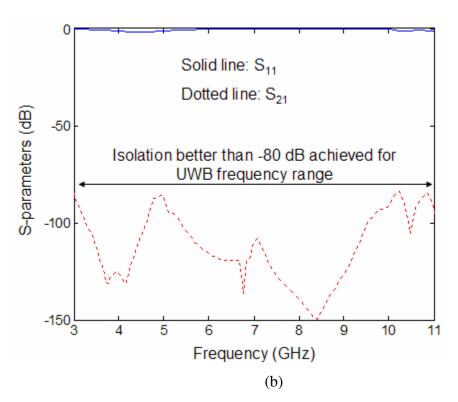

A power-plane segmentation method was recently reported in [13], [14]. In this method, split planes are connected through a narrow conducting neck. Figure 1.15 shows the schematic of power-plane segmentation. This method provides good isolation (-50 dB  $\sim$  -80 dB) in a narrow high-frequency range (frequency range: 300 MHz  $\sim$  700 MHz). But this narrow high-frequency range is not controllable since the size of the split planes determines this high-frequency range. For example, a structure with the power-plane segmentation in Figure 1.16 (a) was simulated. In this case, the size of the split power planes was 4.9 cm x 5.5 cm, the size of the ground plane was 10 cm x 5.5 cm, and the size of the narrow conducting neck was 0.2 cm x 0.5 cm. The transmission coefficient (S<sub>21</sub>) between two ports in Figure 1.16 (a) is shown in Figure 1.16 (b). Hence, this

method is not appropriate for wide-band applications and is not good enough for mixedsignal system applications that require a higher isolation level.

Figure 1.15 Schematic of power-plane segmentation.

Figure 1.16 (a) Schematic of the structure for simulation and (b) Simulation results.

# 1.7 Electromagnetic Bandgap (EBG) Structure

Electromagnetic bandgap (EBG) structures have become popular because of their ability for suppressing unwanted electromagnetic mode transmission and radiation in microwave and millimeter waves [15]-[17]. The EBG structures are periodic structures in which the propagation of electromagnetic waves is forbidden in certain frequency bands. In these EBG structures, the constructive and destructive interference of electromagnetic waves results in transmission and reflection bands [18]. The EBG structure has also been called a photonic bandgap (PBG) structure or a frequency selective surface (FSS). A common feature of periodic structures is the existence of frequency bands where electromagnetic waves are highly attenuated and do not propagate. Analogous to an electrical crystal where periodic atoms presents a bandgap prohibiting electron propagation, a photonic crystal is made of macroscopic dielectrics periodically placed (or embedded) within a surrounding medium. The periodic nature of the structure produces a photonic bandgap (PBG) within which photons (waves) are forbidden in a certain frequency range [18].

In 1987, a three-dimensional (3-D) periodic structure was realized by Yablonovitch [20] by mechanically drilling holes into a block of dielectric material. This structure prevents the propagation of microwave radiation in any three-dimensional (3-D) spatial direction, whereas the material is transparent in its solid form at these wavelengths. These artificially engineered structures are generically known as photonic bandgap (PBG) structures or photonic crystals. Although "photonic' refers to light, the principle of "bandgap" applies to electromagnetic waves of all wavelengths. Consequently, there is controversy in the microwave community about the use of the

term "photonic" [21], and the term "electromagnetic bandgap (EBG) structure" or "electromagnetic crystal" is being proposed [22].

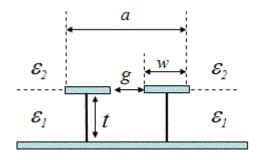

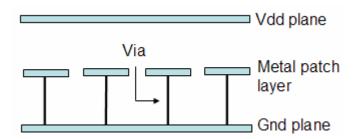

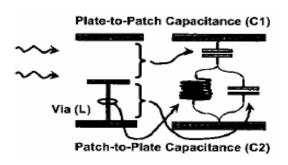

#### 1.7.1 Mushroom-type EBG structure

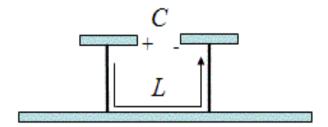

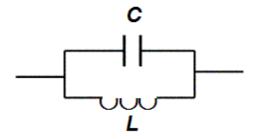

The mushroom-type EBG structure was originally developed by D. Sievenpiper in 1999 for antenna applications [23]-[25]. Figure 1.17 shows the schematic of the mushroom-type EBG structure. By incorporating a special texture on a conducting surface, it is possible to alter its radio frequency electromagnetic properties [23], [24]. It has been proved that an antenna on a mushroom-type ground plane produces a smoother radiation profile than a similar antenna on a conventional metal ground plane, with less power wasted in the backward direction [23]. In this mushroom-type EBG structure, capacitance comes from the fringing electric field between adjacent metal patches and inductance comes from the currents in the ground plane and in the metal patch layer, as shown in Figure 1.18. Hence, the behavior of the structure can be described as a parallel resonant circuit in Figure 1.19.

Figure 1.17 (a) Cross-section of the mushroom-type EBG structure and (b) Top view of the mushroom-type EBG structure [29].

Figure 1.17 (a) Cross-section of the mushroom-type EBG structure and (b) Top view of the mushroom-type EBG structure [29].

Figure 1.18 Origin of capacitance and inductance in mushroom-type EBG structure [29].

Figure 1.19 Parallel LC equivalent circuit for the structure in Figure 1.17 [29].

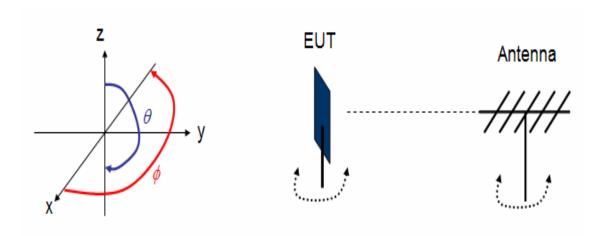

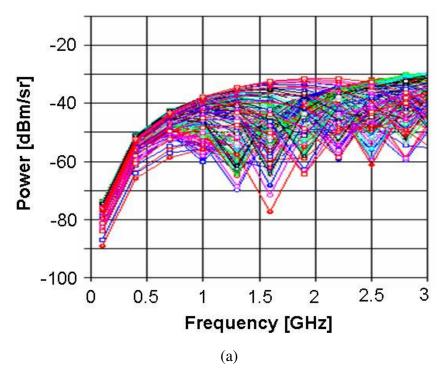

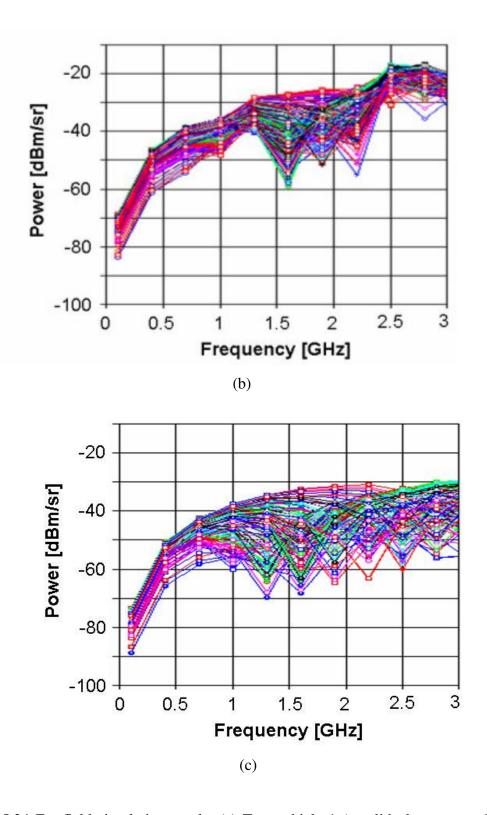

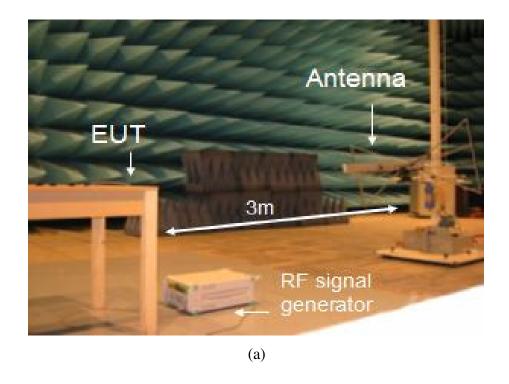

The fringing capacitance between adjacent metal patches can be derived using conformal mapping, a common method for solving two-dimensional electric field distributions [29]. The inductance in this structure can be derived easily from basic EM equations. Therefore, we have the following C and L equations for the structure in Figure 1.18.