# MACROMODELING OF NONLINEAR DRIVER AND RECEIVER CIRCUITS

A Thesis Presented to The Academic Faculty

by

**Bhyrav Mutnury**

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy

School of Electrical and Computer Engineering Georgia Institute of Technology December 2005

# MACROMODELING OF NONLINEAR DRIVER AND RECEIVER CIRCUITS

#### Approved by:

Dr. Madhavan Swaminathan (Advisor) Professor, Department of ECE Georgia Institute of Technology

Dr. Sung-Kyu Lim Asst. Professor, Department of ECE Georgia Institute of Technology

Dr. Suresh K. Sitaraman Professor, Department of ME Georgia Institute of Technology Dr. Abhijit Chatterjee Professor, Department of ECE Georgia Institute of Technology

Dr. David C. Keezer Professor, Department of ECE Georgia Institute of Technology

Date Approved: 08-03-2005

#### **ACKNOWLEDGEMENTS**

First, I want to thank my advisor, Professor Madhavan Swaminathan, for his guidance and support during my graduate studies. He is an outstanding scientist, mentor, and a tremendous source of motivation. I will always be grateful for his valuable advice and insight. I would also like to extend my gratitude to the Ph.D. committee: Professor Abhijit Chatterjee, Professor David C. Keezer, Professor Sung Kyu Lim, and Prof. Suresh K. Sitaraman. I appreciate their time and effort in serving on my committee. I extend special thanks to all current and graduated members of the research group. Your friendship, assistance, and opinions will always be appreciated. I would especially like to mention Nanju Na, Sungjun Chun, Sung-Hwan Min, Vinu Govind, Woopoung Kim, Erdem Matoglu, Jinwoo Choi, Jinseong Choi, Sidharth Dalmia, Jifeng Mao, Prathap Muthana, Rohan Mandrekar, Amit Bavisi, Tae Hong Kim, Wansuk Yun, Raghavan Madhavan, Di Qian, Joongho Kim, Krishna Srinivasan, Subramanian Natarajan Lalgudi, Souvik Mukherjee, Krishna Bharat and Lixi Wang. I would like to thank Moises Cases, Nam Pham, and Daniel de Araujo from IBM, Austin, for their support and encouragement throughout my PhD. I would like to thank James Libous at IBM for his support and encouragement for my studies.

# TABLE OF CONTENTS

| AC  | KNOWLED        | GEMENTS                                            | iii  |

|-----|----------------|----------------------------------------------------|------|

| LIS | T OF TABL      | ES                                                 | viii |

| LIS | T OF FIGU      | RES                                                | viii |

| SUI | MMARY          |                                                    | XV   |

| CH  | APTER I IN     | TRODUCTION                                         | 1    |

| 1.1 | Macromode      | ling                                               | 3    |

| 1.2 | Rationale fo   | or Nonlinear Driver/Receiver Macromodeling         | 5    |

| 1.3 | Existing Dr    | iver and Receiver Macromodels                      | 7    |

|     | 1.3.1          | IBIS Driver Models                                 | 8    |

|     | 1.3.2          | IBIS Driver Modeling Limitations                   | 12   |

|     | 1.3.3          | IBIS Receiver Models                               | 16   |

| 1.4 | Proposed R     | esearch and Dissertation Outline                   | 17   |

| CH. | APTER II N     | ACROMODELING OF DIGITAL DRIVERS                    | 23   |

| 2.1 | Radial Basi    | s Function Based Modeling                          | 25   |

|     | 2.1.1          | Limitations of RBF Modeling Approach               | 29   |

| 2.2 | Classification | on of Driver Circuits                              | 31   |

| 2.3 | Static Chara   | acteristic Modeling                                | 32   |

|     | 2.3.1          | Test Results                                       | 35   |

| 2.4 | Spline Fund    | tion with Finite Time Difference (SFWFTD) Modeling | 39   |

|     | 2.4.1          | Test Results                                       | 44   |

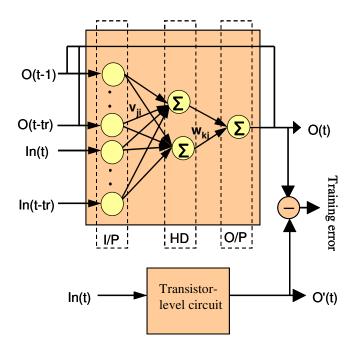

| 2.5 | Recurrent N    | Jeural Network Modeling                            | 46   |

|     | 2.5.1          | RNN Driver Modeling                                | 49   |

|     | 2.5.2          | Test Results                                       | 50   |

| 2.6 | Measureme      | nt to Model Correlation                            | 52   |

| 2.7 | Pre-emphas     | is Driver Modeling                                 | 56   |

|     | 2.7.1          | Test Results                                       | 58   |

| 2.8 | Summary        |                                                    | 59   |

| CH  | APTER III I  | MACROMODELING OF DRIVERS WITH MULTIPLE PORTS    | 61   |

|-----|--------------|-------------------------------------------------|------|

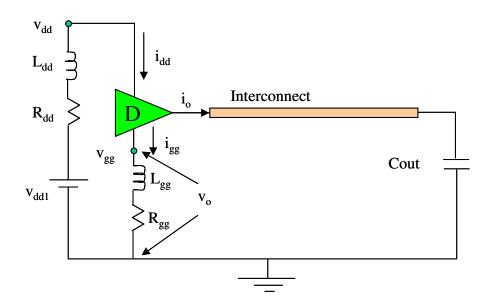

| 3.1 | Effect of Po | ower Distribution Network (PDN)                 | 62   |

| 3.2 | Non-Ideal l  | Power Supply and Ground Nodes                   | 65   |

|     | 3.2.1        | Non-Ideal Power Supply Node                     | 65   |

|     | 3.2.2        | Non-Ideal Power Supply and Ground Nodes         | 71   |

| 3.3 | Test Result  | s                                               | 78   |

| 3.4 | Summary      |                                                 | 88   |

| СН  | APTER IV     | MACROMODELING OF DIFFERENTIAL DRIVER CIRCUITS V | VITH |

| PRI | E-EMPHAS     | IS                                              | 89   |

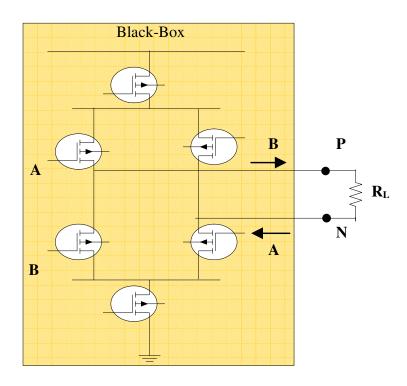

| 4.1 | IBIS Differ  | ential Driver Model                             | 91   |

| 4.2 | Differential | Driver Modeling                                 | 92   |

| 4.3 | Pre-emphas   | sis Differential Driver Modeling                | 98   |

| 4.4 | Spice Netli  | st                                              | 100  |

| 4.5 | Test Result  | s                                               | 101  |

| 4.6 | Summary      |                                                 | 105  |

| СН  | APTER V R    | RECEIVER MACROMODEING                           | 107  |

| 5.1 | Receiver M   | Iodeling Approaches – Prior Art                 | 109  |

|     | 5.1.1        | Limitations of Receiver Modeling Techniques     | 111  |

| 5.2 | Receiver M   | Iodeling Methodology                            | 112  |

|     | 5.2.1        | Receiver Input Characteristics Modeling         | 112  |

|     | 5.2.2        | Receiver Output Characteristics Modeling        | 117  |

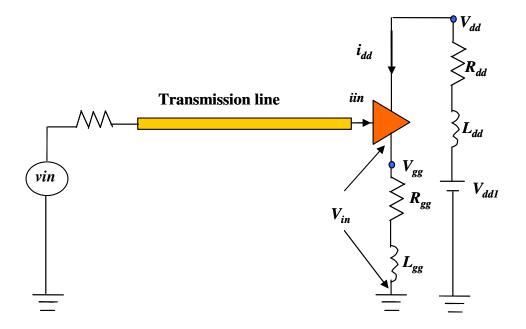

| 5.3 | Extension t  | o Multiple Ports                                | 120  |

|     | 5.3.1        | Receiver Input Characteristics Modeling         | 120  |

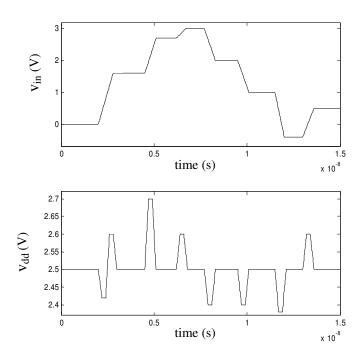

|     | 5.3.2        | Receiver Output Characteristics Modeling        | 122  |

| 5.4 | Spice Netli  | st Generation                                   | 124  |

| 5.5 | Test Result  | 'S                                              | 125  |

|     | 5.5.1        | Two-port Results                                | 125  |

|     | 5.5.2        | Four-port Results                               |      |

| 5.6 | Summary      |                                                 | 136  |

| СН  | APTER VI     | SCALABLE DRIVER AND RECEIVER MACROMODELS        | 138  |

| 6.1 | Scalable M   | acromodels                                      | 140  |

|     | 6.1.1          | Temperature Scalable Differential Driver Macromodels | 140 |

|-----|----------------|------------------------------------------------------|-----|

|     | 6.1.2          | Extension to Multiple Variables                      | 142 |

| 6.2 | Test Results   |                                                      | 144 |

|     | 6.2.1          | Differential Driver Results:                         | 144 |

|     | 6.2.2          | Single-ended Driver and Receiver Results:            | 146 |

| 6.3 | Statistical ar | nd Yield Analysis                                    | 149 |

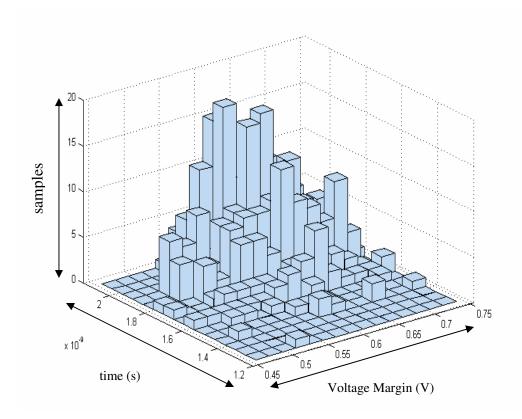

|     | 6.3.1          | Test Results                                         | 152 |

| 6.4 | Summary        |                                                      | 155 |

| СН  | APTER VII      | CONCLUSION AND FUTURE WORK                           | 157 |

| 6.1 | Conclusions    | s                                                    | 158 |

| 6.2 | Future Worl    | C                                                    | 161 |

| 6.3 | Publications   | s                                                    | 164 |

| APl | PENDIX A       |                                                      | 167 |

| APl | PENDIX B       |                                                      | 168 |

| RE  | FERENCES .     |                                                      | 169 |

| VIT | `A             |                                                      | 179 |

# LIST OF TABLES

| Table 2.1 | Driver input rise time Vs. number of basis functions needed                 | . 30 |

|-----------|-----------------------------------------------------------------------------|------|

| Table 2.2 | CTT parallel on-chip termination measurement Vs simulation result           | . 55 |

| Table 2.3 | Computational speed-up and mean square error for driver macromodels         | . 60 |

| Table 3.1 | Memory reduction and computational speed-up for driver macromodels          | . 87 |

| Table 4.1 | Comparison between IBM driver and RNN macromodel.                           | 105  |

| Table 5.1 | Accuracy, simulation speed-up and memory reduction for test cases           | 137  |

| Table 6.1 | Temperature, power supply voltage and process variations for the best case, |      |

| typic     | al case and worst case for IBM DDR2 driver circuit                          | 143  |

# LIST OF FIGURES

| Figure 1.1 Operating frequency trends in Intel microprocessors                                 |

|------------------------------------------------------------------------------------------------|

| Figure 1.2 Power supply voltage trends in microprocessors                                      |

| Figure 1.3 Black-box macromodel of an N-port device                                            |

| Figure 1.4 Black-box macromodel of a nonlinear circuit.                                        |

| Figure 1.5 IBIS driver model schematic                                                         |

| Figure 1.6 IBIS driver pull-down curve                                                         |

| Figure 1.7 IBIS driver pull-up curve                                                           |

| Figure 1.8 IBIS driver rising and falling waveforms.                                           |

| Figure 1.9 Voltage waveforms at the near-end and the far-end of the transmission line for      |

| transistor-level driver circuit (straight line) and IBIS model (dashed line)                   |

| Figure 1.10 Voltage waveforms at the near-end and the far-end of the transmission line         |

| for transistor-level driver circuit (straight line) and spline function with finite time       |

| difference model (dashed line)                                                                 |

| Figure 1.11 Voltage waveforms at the near-end and the far-end of the transmission line         |

| for a transistor-level driver circuit and SSN when multiple drivers are switching 15           |

| Figure 1.12 Voltage waveforms at the near-end and the far-end of the transmission line         |

| for an IBIS driver model and SSN when multiple IBIS driver models are switching.               |

|                                                                                                |

| Figure 1.13 IBIS receiver model schematic                                                      |

| Figure 1.14 Procedure for driver/receiver modeling                                             |

| Figure 2.1 Different radial basis functions with varying widths                                |

| Figure 2.2 Voltage Identification signal at the driver output to estimating $f_1$ for 1ns rise |

| time                                                                                           |

| Figure 2.3 Current Identification signal at the driver output corresponding to Figure 2.2.     |

| 27                                                                                             |

| Figure 2.4 Driver input rise time Vs. simulation time required for transistor-level IBM        |

| driver (straight line) and RBF driver model (dashed line)                                      |

| Figure 2.5 DC relation between driver output current and output voltage when driver                                   |   |

|-----------------------------------------------------------------------------------------------------------------------|---|

| input is HIGH                                                                                                         | 3 |

| Figure 2.6 Weighting functions $w_1(t)$ and $w_2(t)$                                                                  | 4 |

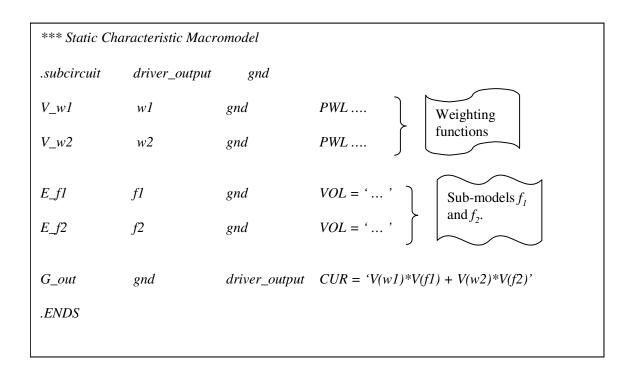

| Figure 2.7 Spice netlist representation for a static characteristic model                                             | 5 |

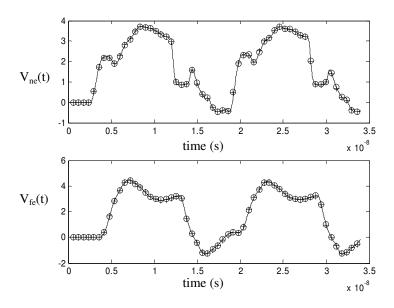

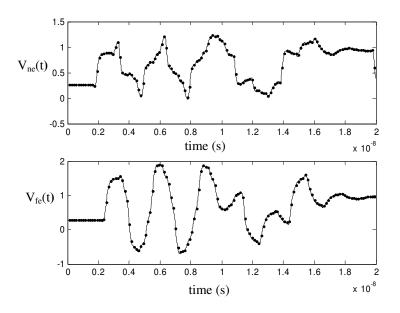

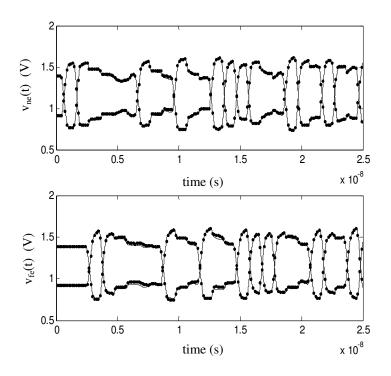

| Figure 2.8 Near-end $V_{\text{ne}}(t)$ and far-end $V_{\text{fe}}(t)$ waveforms on the 100-ohm transmission           |   |

| line connected to IBM transistor model ( straight line), RBF model ( 'o' ) and static                                 |   |

| characteristic model ('+')                                                                                            | 6 |

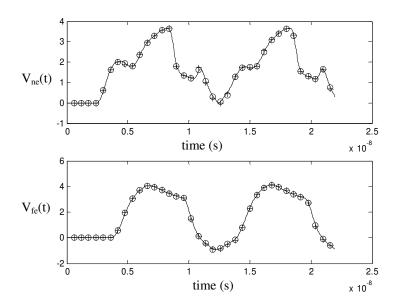

| Figure 2.9 Near-end $V_{\text{ne}}(t)$ and far-end $V_{\text{fe}}(t)$ waveforms on the 75-ohm transmission line       | e |

| connected to IBM transistor model ( straight line), RBF model ( 'o' ) and static                                      |   |

| characteristic model ('+')                                                                                            | 7 |

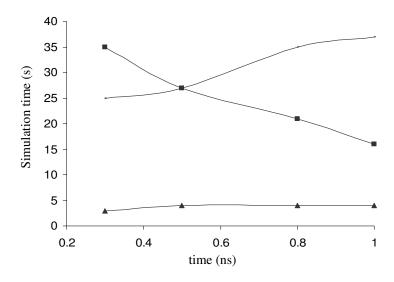

| Figure 2.10 Time taken for simulation for different rise-times a) IBM model (straight                                 |   |

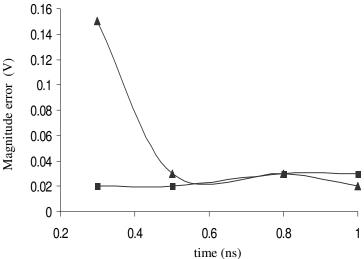

| line), b) RBF model (■), and c) static characteristic model (▲)                                                       | 8 |

| Figure 2.11 Magnitude accuracy of the models for different rise-times a) RBF model ( $\blacksquare$                   | ) |

| and b) static characteristic model (▲).                                                                               | 8 |

| Figure 2.12 PWL voltage source connected at the output of driver for input HIGH and                                   |   |

| the corresponding output current from transistor-level driver circuit (straight line)                                 |   |

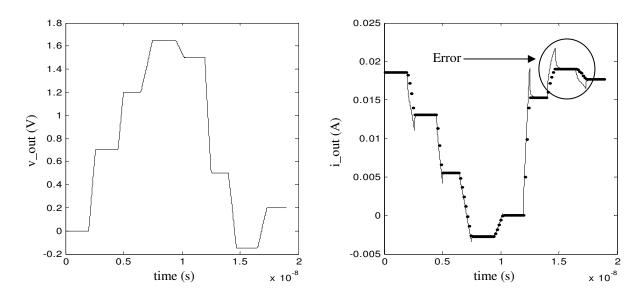

| and static characteristic model (dotted line).                                                                        | 9 |

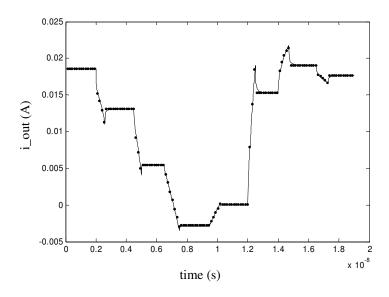

| Figure 2.13 Output current from an IBM transistor-level model (straight line) and from                                |   |

| SFWFTD model (dotted line)                                                                                            | 1 |

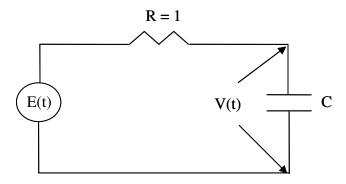

| Figure 2.14 Circuit representation of dynamic characteristics                                                         | 2 |

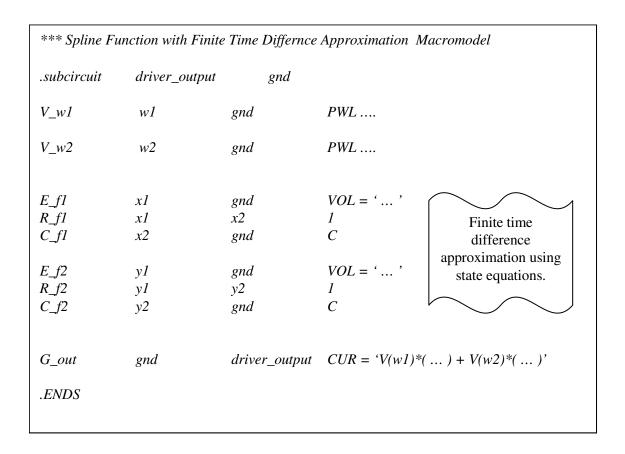

| Figure 2.15 Spice netlist representation for SFWFTD approximation model 4                                             | 3 |

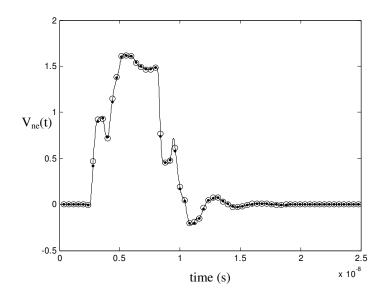

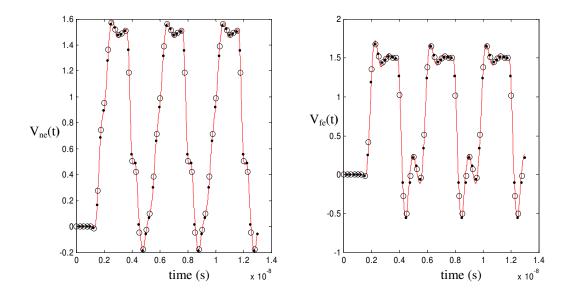

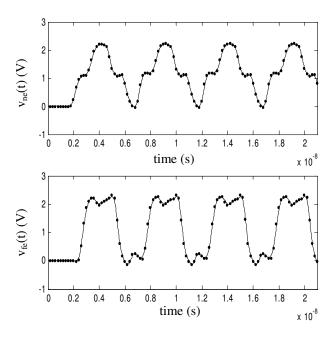

| Figure 2.16 Near end $V_{ne}(t)$ voltage waveform for IBM driver (straight line), SFWFTD                              |   |

| model (dotted line) and RBF model (0)                                                                                 | 5 |

| Figure 2.17 Near-end $V_{ne}(t)$ and far-end $V_{fe}(t)$ voltage waveforms for IBM driver                             |   |

| (straight line), SFWFTD model (dotted line) and RBF model (0)4                                                        | 6 |

| Figure 2.18 Schematic of Recurrent Neural Network (RNN) model                                                         | 7 |

| Figure 2.19 Near end ( $V_{\text{ne}}(t)$ ) and far end ( $V_{\text{fe}}(t)$ ) voltage waveforms on transmission line | e |

| for IBM transistor-level driver model (straight line), RBF model (dashed line) and                                    |   |

| SFWFTD model (dotted line)                                                                                            | 1 |

| Figure 2.20 Near end ( $V_{\text{ne}}(t)$ ) and far end ( $V_{\text{fe}}(t)$ ) voltage waveforms on transmission line | e |

| for IBM transistor-level driver model (straight line) and RNN model (dotted line). 5                                  | 1 |

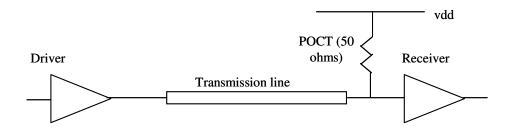

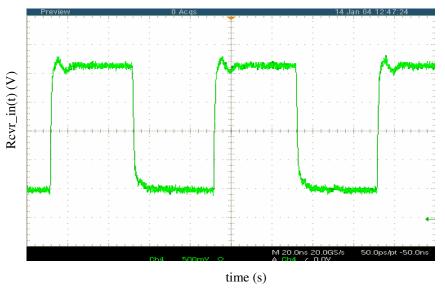

| Figure 2.21 CTT parallel on-chip termination setup scheme                                                         |

|-------------------------------------------------------------------------------------------------------------------|

| Figure 2.22 CTT parallel on-chip termination measurement result                                                   |

| Figure 2.23 Voltage waveform at receiver input for CTT parallel on-chip termination a)                            |

| transistor-level circuit Hspice simulation result (straight line) and b) RNN                                      |

| macromodel result (dotted line).                                                                                  |

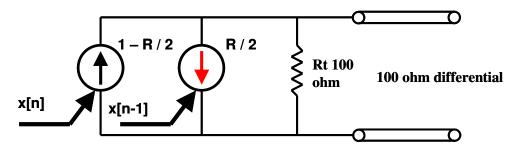

| Figure 2.24 A two-tap FIR driver pre-compensation scheme                                                          |

| Figure 2.25 Input and output voltage waveforms for a two-tap FIR pre-compensation                                 |

| driver57                                                                                                          |

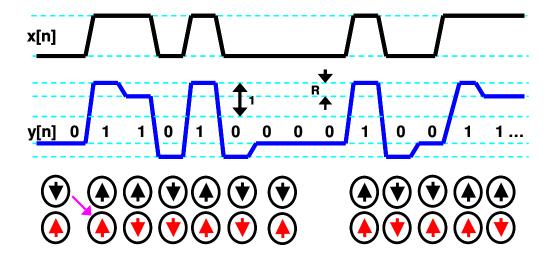

| Figure 2.26 Weighting function $w_1$ and $w_2$ for IBM pre-emphasis driver                                        |

| Figure 2.27 Voltage waveform at the near-end $(V_{\text{ne}}(t))$ and far-end $(V_{\text{fe}}(t))$ of the         |

| transmission line from IBM transistor-level driver (straight line) and SFWFTD                                     |

| model (dotted line)                                                                                               |

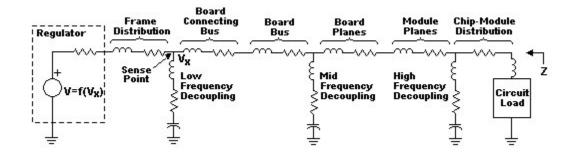

| Figure 3.1 Power distribution network (PDN) for the typical high-speed digital system.                            |

| 63                                                                                                                |

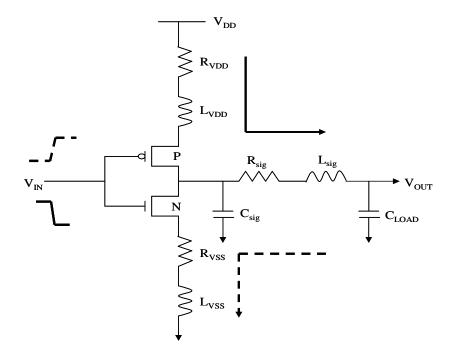

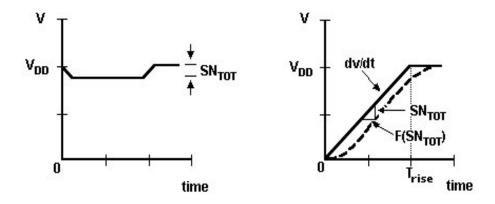

| Figure 3.2 Switching of a CMOS inverter.                                                                          |

| Figure 3.3 Graphical derivation of signal delay due to switching noise [C2]                                       |

| Figure 3.4 A driver with a non-ideal power supply $v_{dd}$ is connected to a transmission line                    |

| 66                                                                                                                |

| Figure 3.5 PWL voltage sources connected at the driver output and the power supply                                |

| node to calculate the dynamic characteristics of SFWFTD approach                                                  |

| Figure 3.6 Weighting functions $w_{1dd}$ , $w_{2dd}$ , and $w_{3dd}$ that help sub-models $f_{1dd}$ and $f_{2dd}$ |

| transition from one state to another                                                                              |

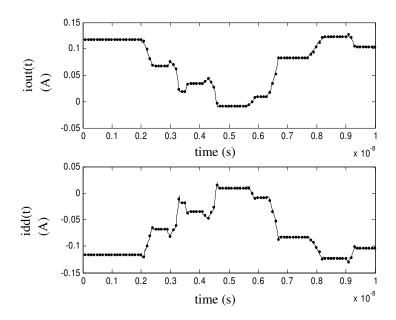

| Figure 3.7 Driver output current and power supply current from transistor level driver                            |

| (straight line) and SFWFTD model (dotted line) when the driver input is HIGH 70                                   |

| Figure 3.8 PWL voltage sources connected at driver output, driver power supply, and                               |

| driver ground ports73                                                                                             |

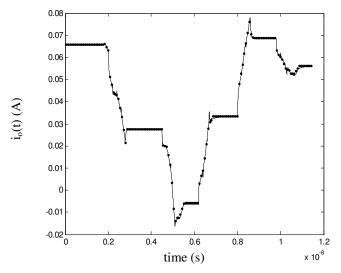

| Figure 3.9 Driver ground current $i_o$ when the driver input is held HIGH from IBM DDR2                           |

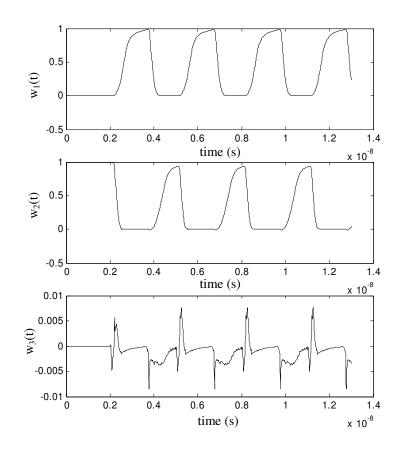

| driver (straight line) and RNN model (dotted line)                                                                |

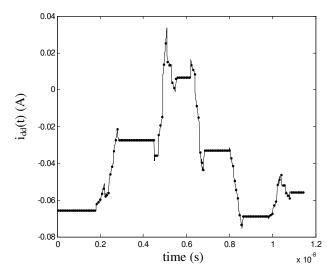

| Figure 3.10 Driver ground current $i_{dd}$ when the driver input is held HIGH from IBM                            |

| DDR2 driver (straight line) and RNN model (dotted line)                                                           |

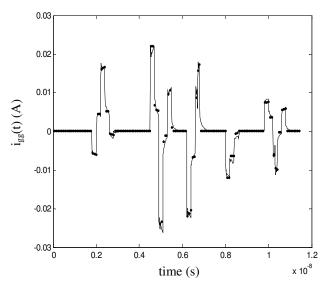

| Figure 3.11 Driver ground current $i_{gg}$ when the driver input is held HIGH from IBM                           |     |

|------------------------------------------------------------------------------------------------------------------|-----|

| DDR2 driver (straight line) and RNN model (dotted line).                                                         | 76  |

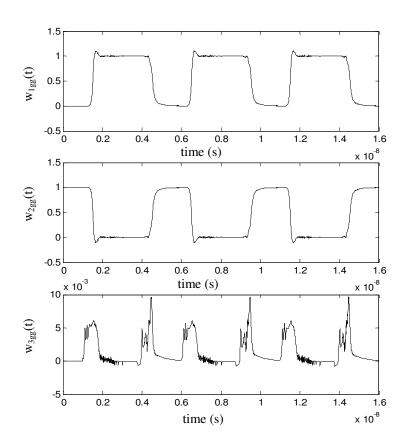

| Figure 3.12 Weighting functions $w_{1gg}$ , $w_{2gg}$ , and $w_{3gg}$ for IBM DDR2 driver                        | 77  |

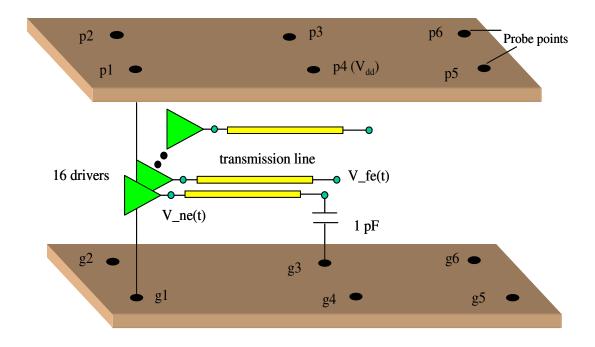

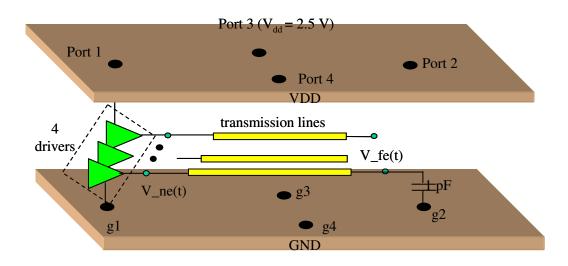

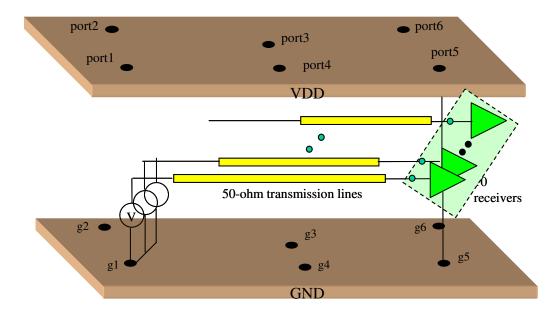

| Figure 3.13 Plane pair model generated using cavity resonator method. Both planes have                           | ve  |

| six ports each                                                                                                   | 79  |

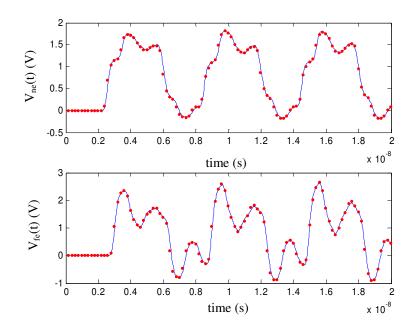

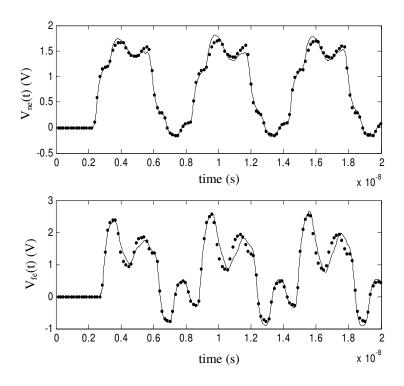

| Figure 3.14 Near-end ( $V_{ne}(t)$ ) and far-end ( $V_{fe}(t)$ ) voltage waveforms on transmission               |     |

| line # 1 for actual transistor level driver model (straight line) and SFWFTD model                               |     |

| (dotted line).                                                                                                   | 79  |

| Figure 3.15 Simultaneous Switching Noise (SSN) at ports p1, p3, and p5 when 16                                   |     |

| identical drivers are switching together. SSN from actual transistor level driver                                |     |

| model (straight line) and SFWFTD model (dotted line)                                                             | 80  |

| Figure 3.16 Near-end ( $V_{\text{ne}}(t)$ ) and far-end ( $V_{\text{fe}}(t)$ ) voltage waveforms on transmission |     |

| line # 1 for SFWFTD model with SSN (straight line) and SFWFTD model with ide                                     | eal |

| v <sub>dd</sub> (dotted line).                                                                                   | 81  |

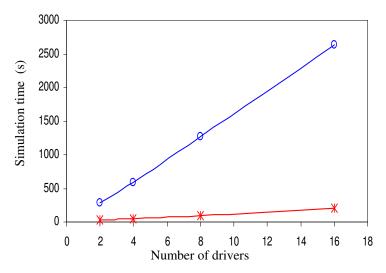

| Figure 3.17 Simulation time Vs. number of drivers switching for transistor level driver                          |     |

| (0) and SFWFTD model (*)                                                                                         | 82  |

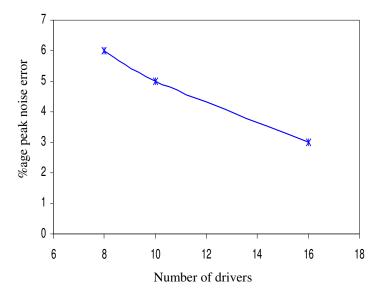

| Figure 3.18 Percentage peak noise error Vs. number of drivers switching for SFWFTD                               |     |

| model                                                                                                            | 82  |

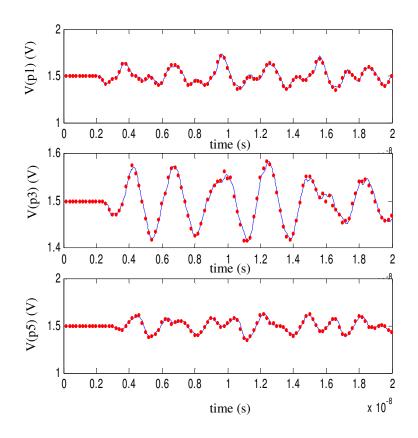

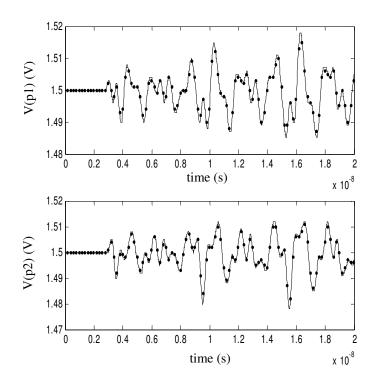

| Figure 3.19 Plane pair model generated using cavity resonator method. Both planes have                           | ve  |

| four ports each                                                                                                  | 84  |

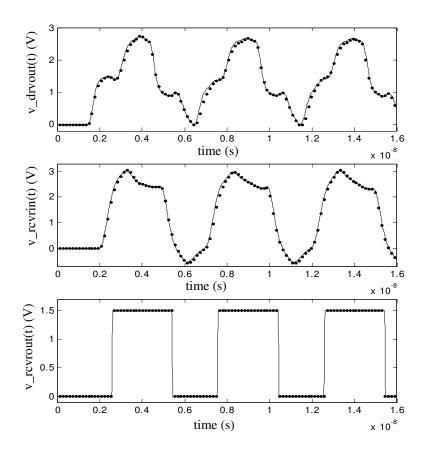

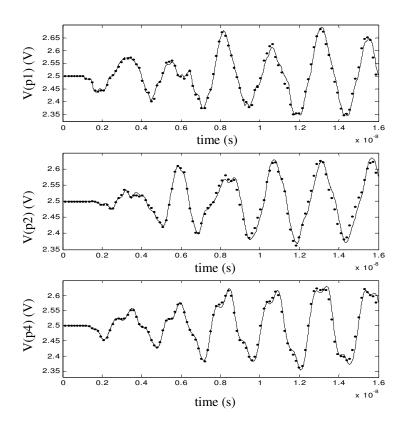

| Figure 3.20 Simultaneous Switching Noise (SSN) at ports p1, p2, and p4 when four                                 |     |

| identical drivers are switching together. SSN from actual transistor level driver                                |     |

| model (straight line) and RNN model (dotted line)                                                                | 84  |

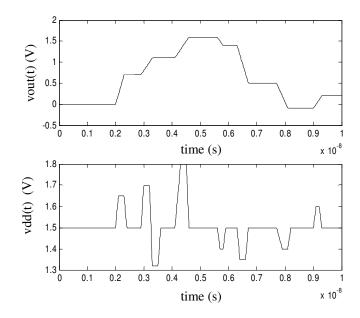

| Figure 3.21 Voltage waveforms at near-end of the transmission line, far-end of the                               |     |

| transmission line, and local ground from IBM DDR2 driver circuit (straight line)                                 |     |

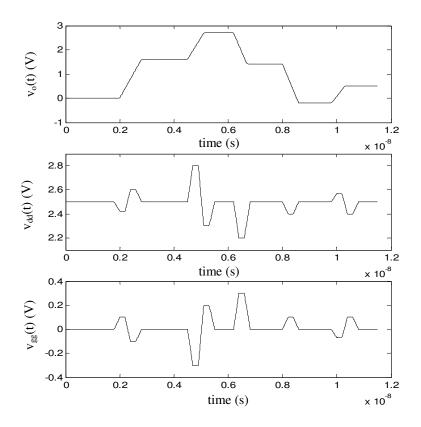

| and RNN model (dotted line)                                                                                      | 85  |

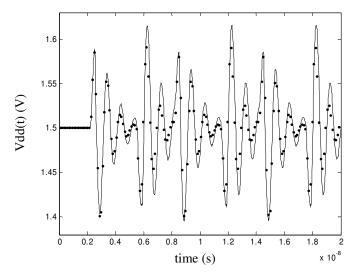

| Figure 3.22 Voltage waveforms at near-end of the transmission line, power supply nod                             | e,  |

| and local ground from IBM DDR2 driver circuit (straight line) and RNN model                                      |     |

| (dotted line)                                                                                                    | 87  |

| Figure 4.1 Black-box model of a differential driver.                                                             | 90  |

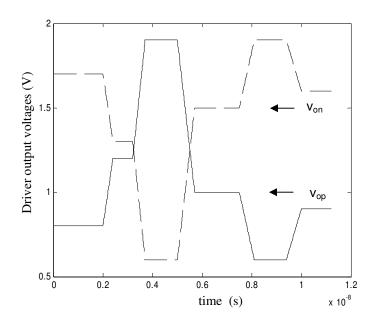

| Figure 4.2 PWL voltage sources at the driver outputs.                                                            | 94  |

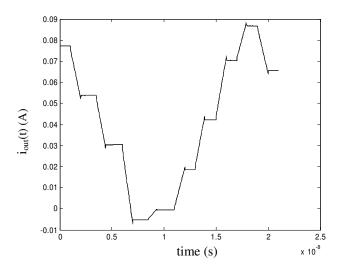

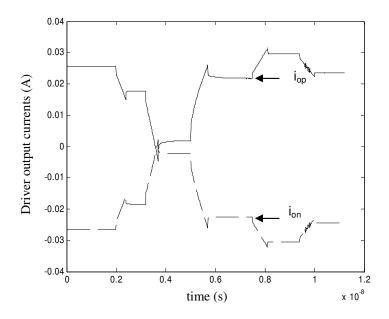

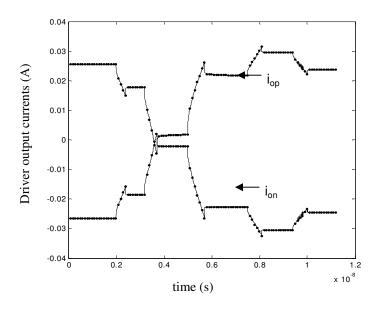

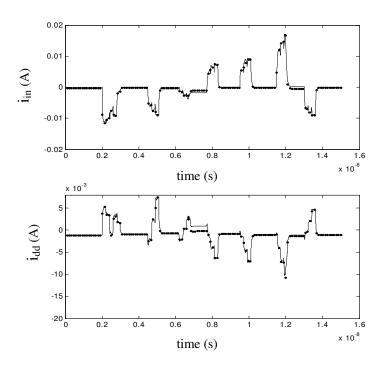

| Figure 4.3 Resultant output current waveforms from PWL voltage sources                   | 15 |

|------------------------------------------------------------------------------------------|----|

| Figure 4.4 Differential driver output current waveforms (straight lines) from PWL        |    |

| voltage sources and from sub-models $f_{Ip}$ and $f_{In}$ (dotted lines)                 | 16 |

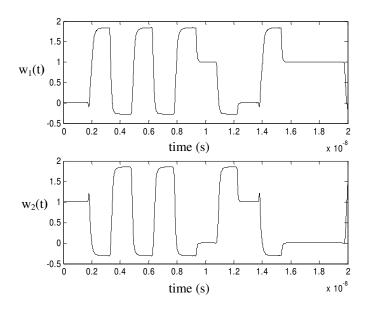

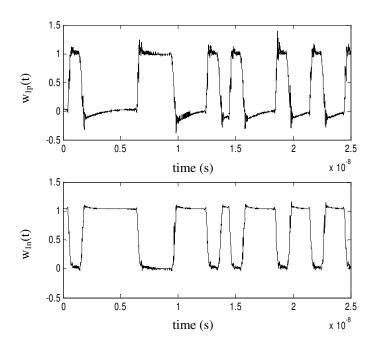

| Figure 4.5 Weighting functions $w_{Ip}$ and $w_{2p}$ for IBM driver                      | 17 |

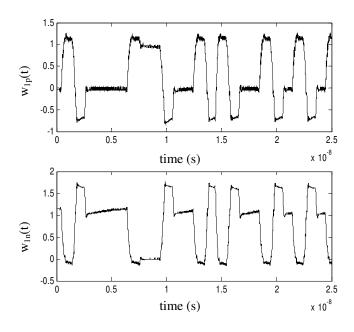

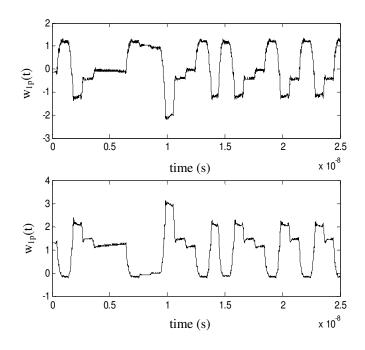

| Figure 4.6 Weighting functions $w_{Ip}$ and $w_{2p}$ for a two-bit pre-emphasis          | 19 |

| Figure 4.7 Weighting functions $w_{Ip}$ and $w_{2p}$ for a three-bit pre-emphasis        | 0  |

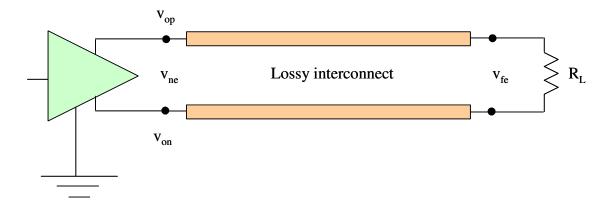

| Figure 4.8 Test set-up for IBM differential driver. 10                                   | 1  |

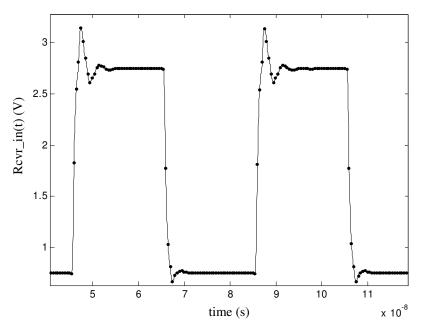

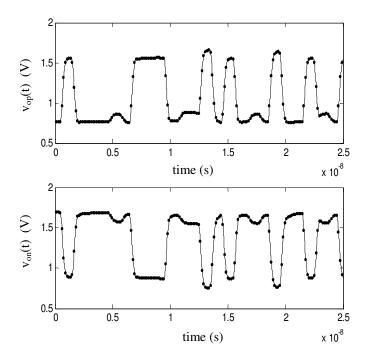

| Figure 4.9 Voltage waveforms at the near-end of the transmission line for IBM            |    |

| transistor-level driver (straight line) and RNN macromodel (dotted line)                 | 12 |

| Figure 4.10 Voltage waveforms at the near-end of the transmission line for IBM           |    |

| transistor-level driver (straight line) and RNN macromodel (dotted line)                 | 13 |

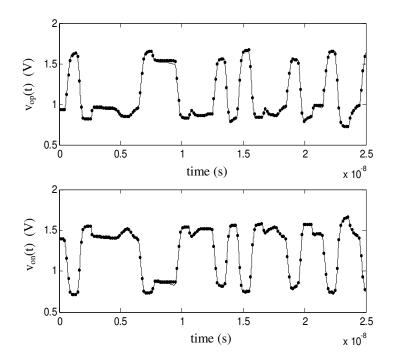

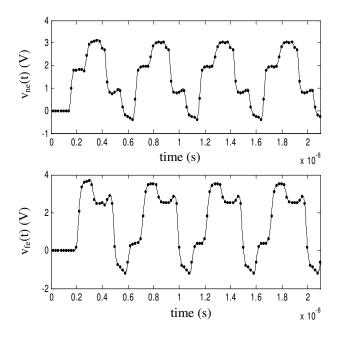

| Figure 4.11 Voltage waveforms at the near-end and far-end of the transmission line for   |    |

| IBM transistor-level driver (straight line) and RNN macromodel (dotted line) 10          | )4 |

| Figure 5.1 Black-box models of driver and receiver circuits                              | )7 |

| Figure 5.2 IBIS receiver model schematic                                                 | 19 |

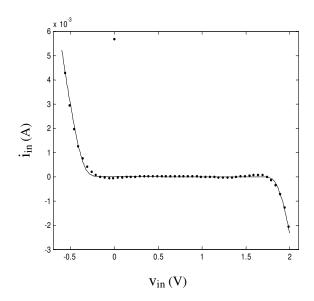

| Figure 5.3 Receiver DC input current Vs. input voltage                                   | 3  |

| Figure 5.4 A PWL voltage sources connected at the receiver input to calculate the        |    |

| dynamic characteristics                                                                  | 4  |

| Figure 5.5 IBM ('AGPV3V2') receiver input current from a PWL voltage source              |    |

| connected at receiver input (straight line) and SFWFTD model (dashed line) 11            | 5  |

| Figure 5.6 IBM DDR2 receiver input current from a PWL voltage source connected at        |    |

| receiver input (straight line) and RNN model (dotted line)                               | 7  |

| Figure 5.7 Receiver static characteristics for IBM ('DDR2') receiver (straight line) and |    |

| neural model (dotted line)                                                               | 8  |

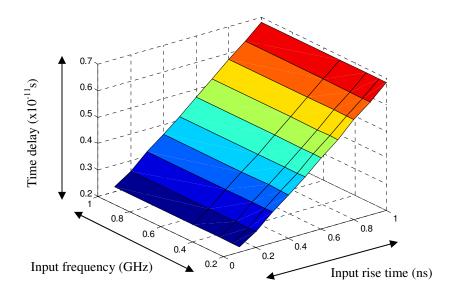

| Figure 5.8 Surface plot between slew rate, frequency and time delay for IBM DDR2         |    |

| receiver                                                                                 | 9  |

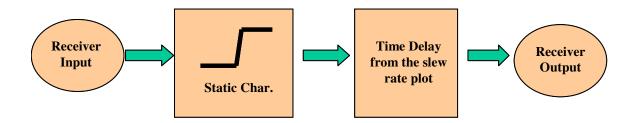

| Figure 5.9 Procedure to model the output characteristics of a receiver circuit           | 9  |

| Figure 5.10 Schematic of a receiver circuit with non-ideal power supply node 12          | 20 |

| Figure 5.11 PWL voltage source connected at receiver input and receiver power supply.    |    |

| 12                                                                                       | 2  |

| Figure 5.12 | IBM DDR2 receiver input current from a PWL voltage source connected at          |

|-------------|---------------------------------------------------------------------------------|

| receive     | er input and receiver power supply (straight line) and RNN model receiver       |

| input a     | nd power supply (dotted line)                                                   |

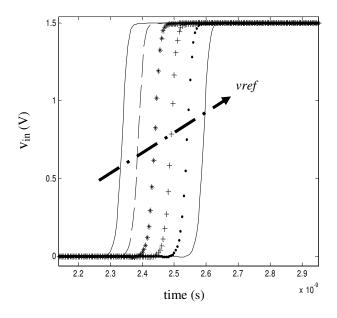

| Figure 5.13 | Effect of <i>vref</i> on the time delay through the receiver circuit            |

| Figure 5.14 | Procedure to model the output characteristics of a receiver circuit taking vref |

| and vd      | d effect into account                                                           |

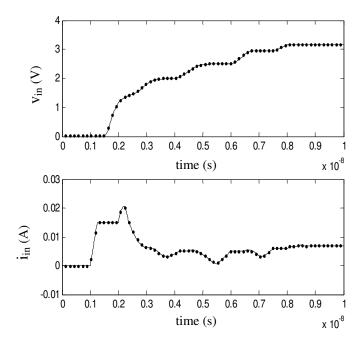

| Figure 5.15 | Voltage at receiver input and current at receiver input for IBM DDR2            |

| (straigh    | nt line) and RNN receiver macromodel input (dotted line)                        |

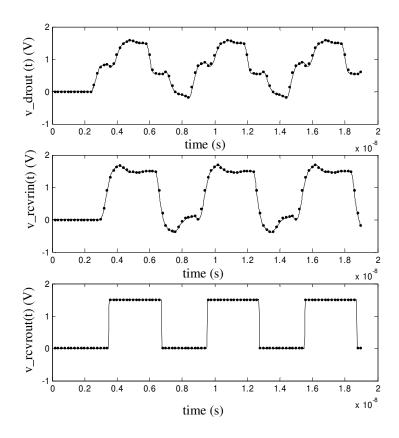

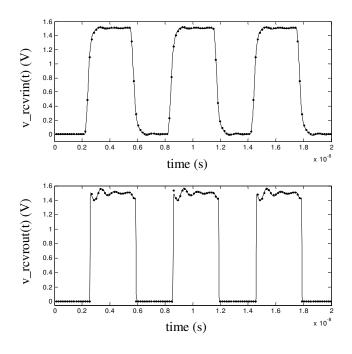

| Figure 5.16 | Driver output voltage, receiver input voltage, and receiver output voltage for  |

| IBM A       | GPV3V2 (straight line) and SFWFTD macromodel output voltage (dotted             |

| line)       |                                                                                 |

| Figure 5.17 | Driver output voltage, receiver input voltage, and receiver output voltage for  |

| IBM A       | GPV3V2 (straight line) and RNN macromodel output voltage (dotted line).         |

|             |                                                                                 |

| Figure 5.18 | Plane pair model generated using cavity resonator method. Both planes have      |

| six por     | ts each                                                                         |

| Figure 5.19 | SSN at port five, port six, and port four when 10 IBM AGPV3V2 receiver          |

| circuits    | are switching (straight line) and 10 RNN receiver macromodels are               |

| switchi     | ng (dotted line), respectively                                                  |

| Figure 5.20 | SSN at port one and port two when 10 IBM AGPV3V2 receiver circuits are          |

| switchi     | ng (straight line) and 10 RNN receiver macromodels are switching (dotted        |

| line), re   | espectively131                                                                  |

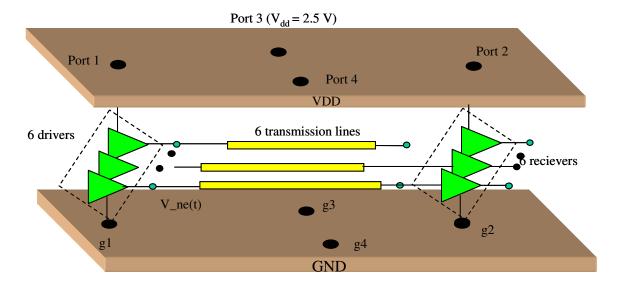

| Figure 5.21 | Plane pair model generated using cavity resonator method. Both planes have      |

| four po     | orts each                                                                       |

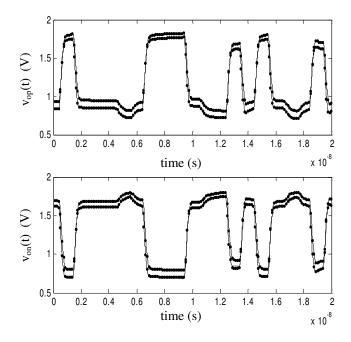

| Figure 5.22 | Driver output voltage, receiver input voltage, and receiver output for IBM      |

| DDR2        | (straight line) and RNN driver macromodel output voltage (dotted line),         |

| respect     | ively                                                                           |

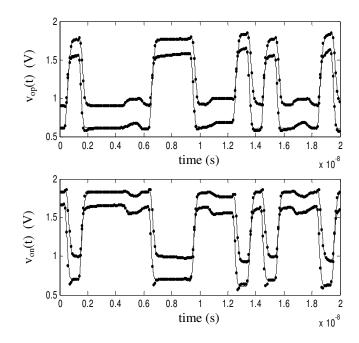

|             | SSN at port one, port two, and port four when six IBM DDR2 driver and           |

| receive     | er circuits are switching (straight line) and six RNN driver and receiver       |

| macror      | models are switching (dotted line), respectively                                |

| Figure 5.24 SSN when 16 IBM APV3V2 receiver circuits are switching (straight line)       |            |

|------------------------------------------------------------------------------------------|------------|

| and 16 RNN receiver macromodels are switching (dotted line)                              | 35         |

| Figure 5.25 Receiver input voltage and receiver output voltage for IBM AGPV3V2           |            |

| (straight line) and RNN receiver macromodel input voltage (dotted line),                 |            |

| respectively                                                                             | 35         |

| Figure 6.1 Statistical variations of signal integrity in digital systems                 | 39         |

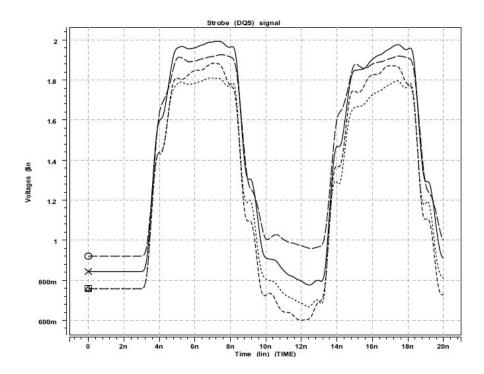

| Figure 6.2 Voltage waveforms at the near-end of the transmission line for IBM transistor | r-         |

| level driver when temperature is varying from 0 to 100° C                                | 10         |

| Figure 6.3 Voltage waveforms at the near-end of the transmission line for IBM            |            |

| transistor-level driver (straight line) and RNN macromodel (dotted line) when drive      | r          |

| temperatures are 27° and 75° C                                                           | 15         |

| Figure 6.4 Voltage waveforms at the near-end of the transmission line for IBM            |            |

| transistor-level driver (straight line) and RNN macromodel (dotted line) when drive      | r          |

| temperatures are -25° and 125° C                                                         | ŀ6         |

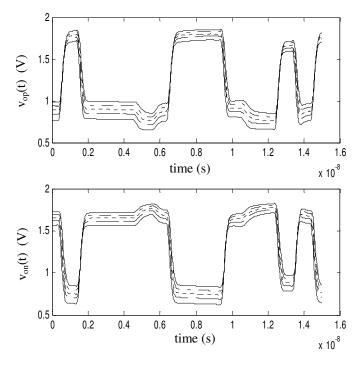

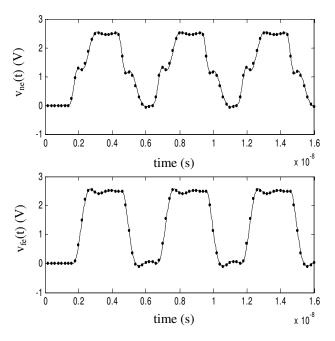

| Figure 6.5 Voltage waveforms at the near-end and far-end of the transmission line for    |            |

| IBM DDR2 transistor-level driver (straight line) and RNN macromodel (dotted line         | ;)         |

| when driver t is $125^{\circ}$ , $\sigma$ is -1.5 and $v_{dd}$ is 2.2 V                  | <b>ŀ</b> 7 |

| Figure 6.6 Voltage waveforms at the near-end and far-end of the transmission line for    |            |

| IBM DDR2 transistor-level driver (straight line) and RNN macromodel (dotted line         | ;)         |

| when driver t is -25°, $\sigma$ is 1.5 and $v_{dd}$ is 2.8 V                             | 18         |

| Figure 6.7 Voltage waveforms at the near-end and far-end of the transmission line for    |            |

| IBM DDR2 transistor-level driver-receiver circuit (straight line) and RNN                |            |

| macromodel (dotted line) when driver t is 27°, $\sigma$ is 0, and $v_{dd}$ is 2.5 V      | 19         |

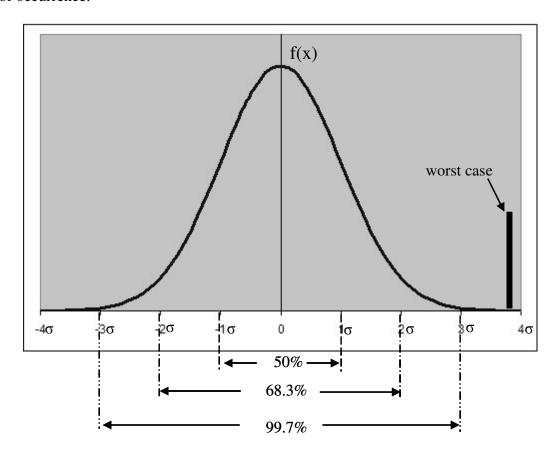

| Figure 6.8 Probability density curve of Normal Distribution                              | 51         |

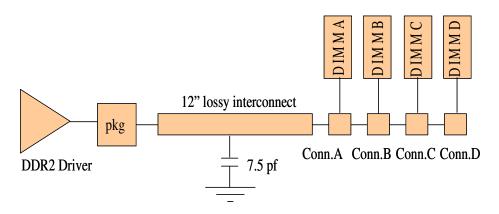

| Figure 6.9 Test set-up for DDR2.                                                         | 53         |

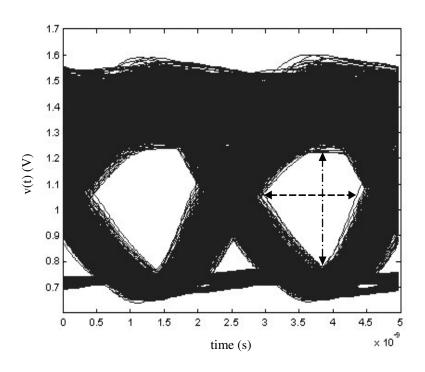

| Figure 6.10 Eye diagram at the end of DIMM D                                             | 53         |

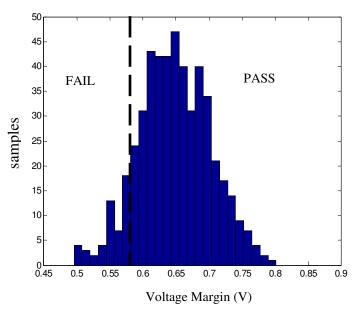

| Figure 6.11 Histogram of the height of the eye opening                                   | 54         |

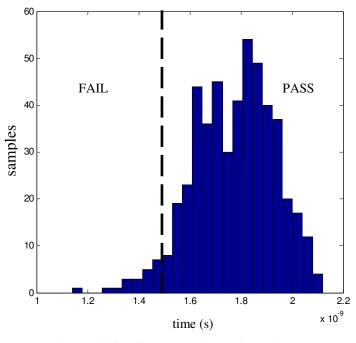

| Figure 6.12 Histogram of the width of the eye opening                                    | 54         |

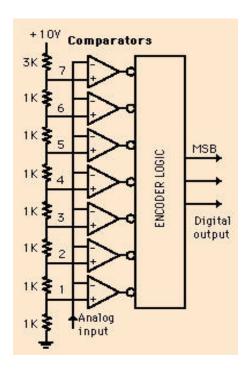

| Figure 7.1. Three-bit flash ADC                                                          | 52         |

#### **SUMMARY**

The signal integrity, power integrity, and timing analysis of today's high-speed digital systems are computationally exhaustive, both in terms of CPU memory required and simulation time consumed. One way to reduce this complexity is to use macromodels of the sub-circuits comprising these high-speed digital systems. Since digital driver/receiver circuits have a major share in this computational load, modeling digital driver/receiver circuits accurately to capture their nonlinearity becomes a big challenge. The contribution of this thesis is to generate black-box macromodels of driver/receiver circuits that result in huge computational speed-up compared to actual transistor-level driver/receiver circuits and at the same time maintain high accuracy. It is always useful to have a black-box modeling approach as the modeling technique is independent of the knowledge of the internal logic of the circuit being modeled. This would make the modeling approach more robust and more applicable to a wide variety of circuits. Driver/receiver macromodels have been extended to multiple ports to take into account the effect of non-ideal power and ground nodes in this thesis.

## **CHAPTER I**

## INTRODUCTION

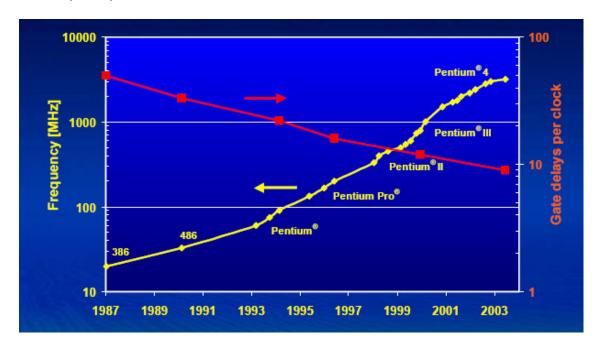

The rapid advance in semiconductor technology is pushing high-performance electronic systems toward higher operating frequency, higher power dissipation, and lower supply voltage, which pose tremendous challenges for designers. It can be seen from Figure 1.1 that the operating frequency for Intel microprocessors has been doubling almost every two years (Moore's Law).

Figure 1.1 Operating frequency trends in Intel microprocessors.

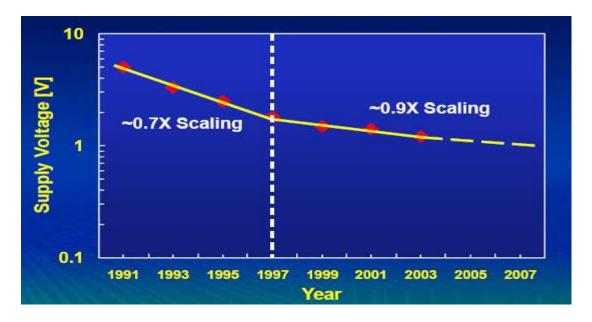

With the operating frequency increasing, parasitic effects that were previously ignored cannot be overlooked anymore for accurate system level analysis. Figure 1.2 shows how the power supply voltage for microprocessors has been decreasing with each

generation of processors. The decrease in power supply voltage and increase in operating frequency and power consumption has left little room for error in modeling today's high-speed systems.

**Figure 1.2** Power supply voltage trends in microprocessors.

The number of failures caused by signal and power integrity problems is on the rise because existing design tools and modeling methodologies cannot address these issues efficiently. Signal integrity, power integrity, and timing analysis of high-speed digital systems are becoming more and more complex, both in terms of CPU memory requirement and simulation time consumed. Analyzing signal and power integrity problems is important for meeting the design specifications. One way to reduce the complexity of the problem is by using macromodels of the sub-circuits comprising these high-speed digital systems. Since digital driver/receiver circuits play an important role in the signal integrity analysis of these high-speed digital systems, modeling digital driver/receiver circuits to capture their nonlinearity accurately is a big challenge. The

focus of this thesis is on the nonlinear macromodeling of driver and receiver circuits for efficient signal and power integrity analysis.

### 1.1 Macromodeling

Macromodeling of a circuit involves producing a reduced order model or behavioral model with the original circuit's input and output ports such that the macromodel runs faster than the original circuit while accurately modeling the actual circuit. Macromodeling can be broadly classified into (1) passive or linear macromodeling and (2) active or nonlinear macromodeling. There has been an increasing demand for integrating the electromagnetic behavior of passive structures into conventional computer-aided design (CAD) tools so that designers can take into account the electromagnetic effects during the design and analysis of multi-GHz electronic systems. In the past, a lot of work was done on the model order reduction of integrated chip (IC) interconnects and modeling passive circuits [A1]-[A2]. The macromodel can be constructed using two methods. One method is to construct the macromodel from the moments that are the characteristics of the circuit. In [A3]-[A6], explicit or implicit moment-matching techniques have been used to construct the macromodel by generating and matching the moments using Padé approximation. The other method is to capture the frequency-dependent data using a macromodel after extracting the port behavior of the circuit either from an electromagnetic simulator or from measurements. In [A7]-[A11], the macromodel has been constructed by capturing measured or simulated frequency data using least squares approximation and vector-fitting.

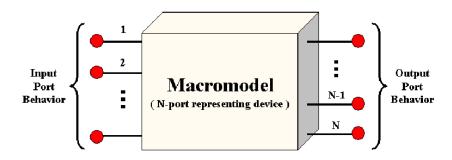

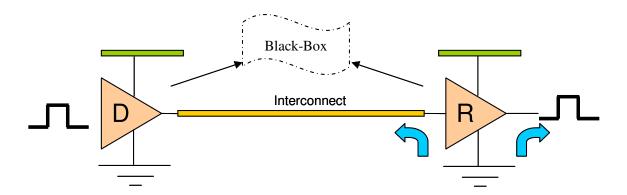

Compared to work done on model order reduction for linear time invariant (LTI) resistance-inductance-capacitance networks, the problem of nonlinear macromodeling is less explored [A12]-[A15]. It is always useful to have modeling techniques that are black-box in nature, in which a circuit can be modeled independently of the knowledge of its internal logic [A16]. This would make the modeling approach more robust and more applicable to a wide variety of circuits. Figure 1.3 shows a black-box representation of an N-port device.

Figure 1.3 Black-box macromodel of an N-port device.

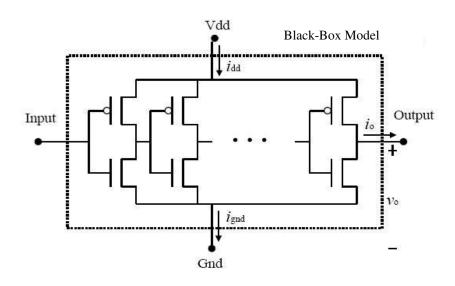

Nonlinear macromodeling is a new field of research. In the past, work has been done on modeling weakly nonlinear analog and RF circuits using Volterra series [A17]-[A18]. More recently, there has been some work on macromodeling digital aggressors for power and ground supply noise prediction. In [A19], independent ideal current sources have been utilized in predicting the simultaneous switching noise (SSN) effects and capacitor controlled ideal switches have been utilized to imitate the switching behavior of a digital cell in [A20]-[A21]. These methods result in an approximate prediction of the SSN. In [A22], linear time-varying (LTV) abstractions have been used to capture the aspects of digital switching nonlinearity. All the above mentioned modeling techniques model a

digital cell block in a mixed signal environment to capture the power and ground noise effects. The effect of power and ground noise on the driver output and receiver input signal and vice-versa is not taken into account. Scalability and extension of the above modeling approaches to multiple ports is a complicated procedure. The focus of this thesis is on the macromodeling of digital driver and receiver circuits for the generation of black-box models, as shown in Figure 1.4, for both efficient signal and power integrity analysis.

Figure 1.4 Black-box macromodel of a nonlinear circuit.

## 1.2 Rationale for Nonlinear Driver/Receiver Macromodeling

According to the International Technology Roadmap for Semiconductors (ITRS) 2004, the power supply voltage of ICs in year 2005 is 0.9 V [A23]. The power supply voltage will steadily reduce to 0.8 V by 2007 and 0.6 V by 2013. Both the on-chip clock frequency and chip-chip (off-chip) frequencies will increase in years to come. The on-chip and off-chip frequencies for 2005 are 5.2 and 3.1 GHz, 9.2 and 4.8 GHz in year

2007, and 22 and 14.9 GHz in 2013, respectively. With the complexity of interconnects and packages increasing and the rise and fall time of the signals decreasing, the previously neglected electromagnetic effects cannot be ignored anymore. With the decrease in the margin of error, accurate analysis of power and signal integrity issues is becoming important [A24].

Signal integrity refers to a broad set of interconnect design issues such as signal reflections, impedance mismatch, and crosstalk coupling. On the other hand, power integrity refers to a set of power supply design issues such as resonance, IR voltage drop, and SSN.

Digital driver circuits drive electronic signals through lossy interconnects in high-speed digital systems. These electronic signals get deformed as they propagate through transmission lines because of crosstalk, attenuation, and impedance mismatch. Receiver circuits receive the distorted signal from interconnects and feed it to the processors. Digital driver and receiver circuits play an important role in high-speed digital systems. Since digital driver/receiver circuits are complex nonlinear dynamic systems containing a very complex functional part and a high number of pins (several hundreds for modern microprocessors), accurate macromodeling of digital I/O drivers is a significant challenge.

In order to perform efficient signal integrity and power integrity analysis on today's high-speed systems, nonlinear driver and receiver macromodels should have all of the below mentioned characteristics.

1. Nonlinear macromodels protect the intellectual property (IP) information of transistor-level driver/receiver circuits and minimize reverse engineering.

- 2. Driver and receiver macromodels consume less simulation time and CPU memory compared to transistor-level circuits without losing accuracy.

- 3. Sensitive issues like SSN and crosstalk can be accurately captured using these macromodels.

- 4. Macromodels are extendable to multiple ports for including power supply and ground node effects.

- 5. Macromodels are scalable to include temperature and process variations.

- 6. Macromodels can be developed in a generic SPICE like format that is universally acceptable independent of the platform being used.

Since the existing nonlinear macromodels do not meet all the above mentioned requirements, there is always a need for accurate nonlinear macromodels that satisfy all the above requirements. The accuracy of signal integrity and electromagnetic compatibility (EMC) simulations depends on the accuracy of the available macromodels of circuit elements. Having accurate macromodels is of paramount importance in the design of fast circuits. These models also capture sensitive effects like waveform distortion, crosstalk, overshoots, and radiation.

## 1.3 Existing Driver and Receiver Macromodels

Input/output buffer information specification (IBIS) is the present industry standard for driver and receiver modeling [A25]. In this section, a description of IBIS driver and receiver models, their accuracy, and their limitations are discussed.

#### **1.3.1** IBIS Driver Models

IBIS is the input/output buffer information specification from the electronics industry alliance (EIA). It is a modeling technique that provides a simple table-based buffer model for semiconductor devices [A26]-[A29]. IBIS models can be used to characterize current/voltage (I/V) output curves, rising/falling transition waveforms, and package parasitic information of the device. It is important to note that an IBIS model is also intended to provide nonproprietary information about driver/receiver circuits. Furthermore, there are many different SPICE formats in the industry today, and not all are compatible with one another [A30]. This process of converting one transistor-level SPICE netlist compatible with another SPICE format is time consuming. IBIS models are compatible with all SPICE formats, saving a lot of time and labor. An IBIS model can be generated either by measurement, which requires having a well-controlled environment and measurement devices, or by using a SPICE generated netlist and running multiple SPICE simulations to get the necessary current voltage tables and voltage transition tables [A31].

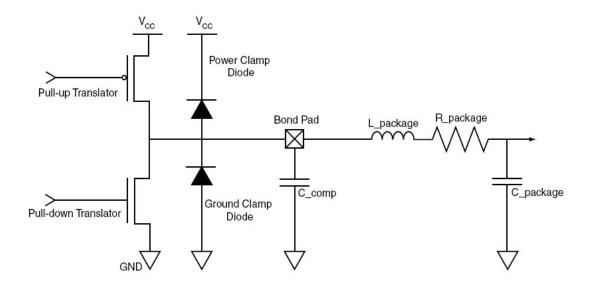

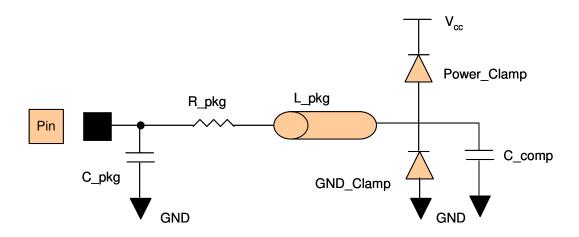

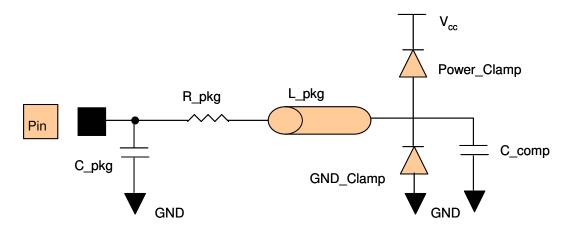

IBIS behavioral models are based on DC current vs. voltage curves along with a set of rise and fall times of the driver output voltage and packaging parasitic information of the I/O buffer. A typical IBIS behavioral model representation is shown in Figure 1.5.

An IBIS model consists of pull-up and pull-down transistors, power and ground clamp diodes, input and output die capacitance (C\_comp), and package characteristics (the values of the lead inductance (L\_package), resistance (R\_package), and capacitance (C\_package)) [A32]-[A33]. IBIS modeling takes into account 1) DC steady-state I/V

characteristics of the pull-up and pull-down transistors, 2) I/V characteristics of the power and ground clamps, and 3) IBIS transition waveforms.

Figure 1.5 IBIS driver model schematic.

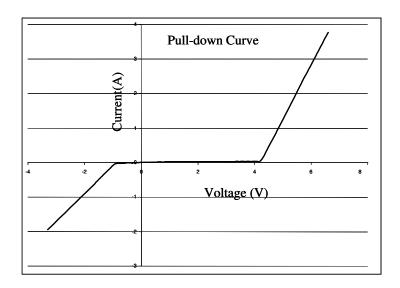

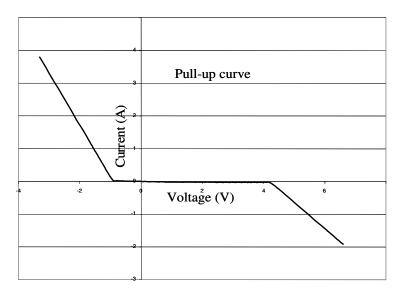

To generate pull-up and pull-down curves, voltage sources are connected at both driver input and output. The output voltage source tries to drive high (for the pull-up curve) or low (for the pull-down curve). The output voltage is swept from (Vgnd - Vcc) to 2Vcc, and the output current at each output voltage is recorded. If the driver has an enable input, the sweep is performed a second time with the driver disabled. This gives the performance of the clamping structure that may be present. The pull-down curve is a result of subtracting the ground clamp I/V curve from the logic LOW I/V curve, since this is where the pull-down transistor is active, as shown in Figure 1.6. Similarly, the pull-up curve is generated by subtracting the power clamp I/V curve from the logic-HIGH I/V curve, as shown in Figure 1.7. Again, the full range is from  $-V_{cc}$  to  $2V_{cc}$ .

Figure 1.6 IBIS driver pull-down curve.

Figure 1.7 IBIS driver pull-up curve.

The ground clamp curve is derived from the ground relative data gathered while the buffer is in a high-impedance state and illustrates the region where the ground clamp diode is active. A voltage source is attached to the associated pin and the output voltage is swept from  $(Vgnd-V_{cc})$  to  $(Vgnd+V_{cc})$ . The power clamp curve is derived from the

$V_{cc}$  relative data gathered while the buffer is in a high impedance state (the driver is disabled) and shows the region where the power clamp diode is active. This measurement ranges from  $V_{cc}$  to  $2V_{cc}$  [A33].

The pull-up and power clamp curves are  $V_{cc}$  relative, i.e., the voltage values are referenced to the  $V_{cc}$  pin. The output current of a pull-up or power clamp configuration depends on the voltage between the output and  $V_{cc}$  pin and not the voltages between the output and the ground pins. The voltages in IBIS tables are derived as shown:

$$Vtable = Vcc - Voutput$$

(1.1)

$$Vtable = Voutput$$

(1.2)

Equation (1.1) represents voltages for pull-up and for power clamp devices and equation (1.2) represents voltages for pull-down and ground clamp devices.

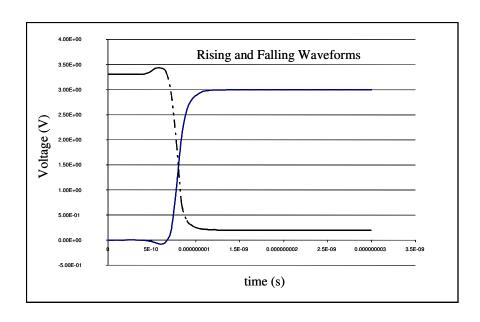

An IBIS model can also provide rising and falling v-t waveforms, which illustrates the transitions from GND to  $V_{cc}$  and from  $V_{cc}$  to GND. These curves can be taken from SPICE simulations when the buffer output is terminated appropriately for the appropriate stimulus at buffer input. The ramp rates are taken when the output voltage varies from 20% to 80%  $V_{cc}$  for the rising waveform and from 80% to 20%  $V_{cc}$  for the falling waveform. In calculating the ramp rates, the effect of parasitics is ignored. These ramp rates are much faster than slew rates in which the package parasitics are taken into account. A typical rising and falling waveform plot for an IBIS driver model is shown in Figure 1.8.

**Figure 1.8** IBIS driver rising and falling waveforms.

#### 1.3.2 IBIS Driver Modeling Limitations

IBIS driver modeling is popular and widely used as it is commercially available, has large sets of libraries, and IBIS models run faster than actual transistor-level driver models. However, IBIS models have limitations. One of the limitations is that the physical effects to be considered are decided a-priori when the equivalent circuit is defined, leaving little or no possibility for including the effects inherent to the device. IBIS models also fail to accurately capture the dynamic characteristics of the driver as the modeling technique relies heavily on static characteristics. The extension of IBIS driver models to multiple ports only results in less accurate models [A35]. IBIS models cannot accurately model sensitive effects like SNN and crosstalk accurately [A36].

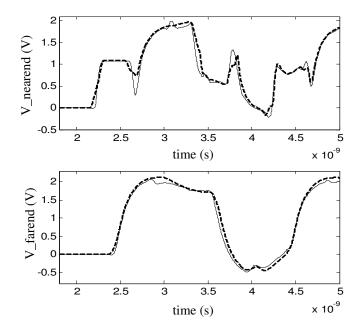

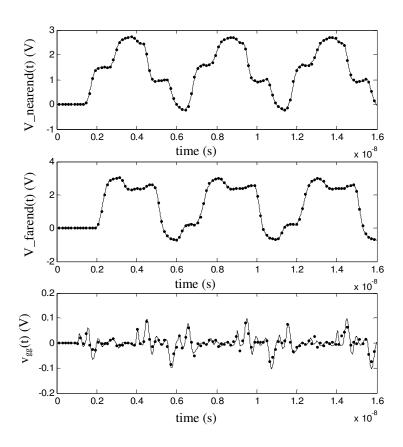

Figure 1.9 compares the accuracy of an IBIS driver model with a transistor-level driver circuit. A test case has been generated where a driver circuit was connected to an ideal 25-ohm ideal transmission line that got terminated at the far end with a 1 pF

capacitance. The transmission line had a delay of 0.2 ns. The driver circuit was generated by cascading seven inverters in series, making the driver circuit weakly nonlinear. The driver was operated at 1 GHz. The near-end and the far-end voltage waveforms of the transmission line were measured for the transistor-level driver circuit and the IBIS driver model. It can be clearly seen that the IBIS model cannot accurately capture the magnitude and timing information even for a weakly nonlinear driver circuit.

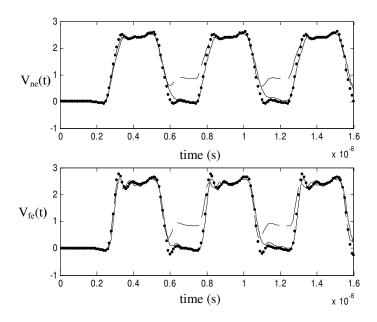

**Figure 1.9** Voltage waveforms at the near-end and the far-end of the transmission line for transistor-level driver circuit (straight line) and IBIS model (dashed line).

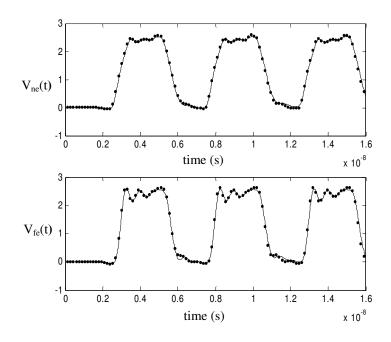

The same driver circuit was modeled using spline function with finite time difference (SFWFTD) modeling approach. A detailed explanation of SFWFTD modeling approach is given in Chapter 2. It can be seen from Figure 1.10 that the near-end and far-end voltage waveforms using SFWFTD macromodel accurately matches with the actual driver circuit voltage waveforms.

**Figure 1.10** Voltage waveforms at the near-end and the far-end of the transmission line for transistor-level driver circuit (straight line) and spline function with finite time difference model (dashed line).

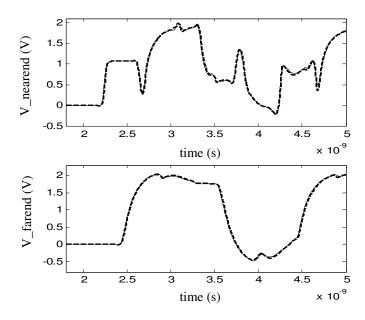

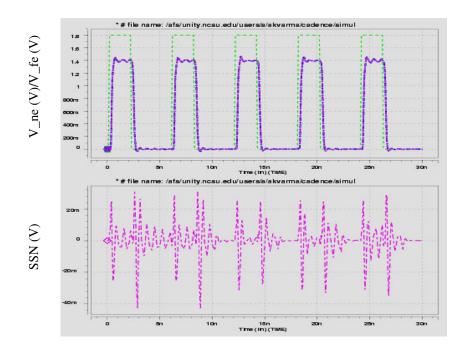

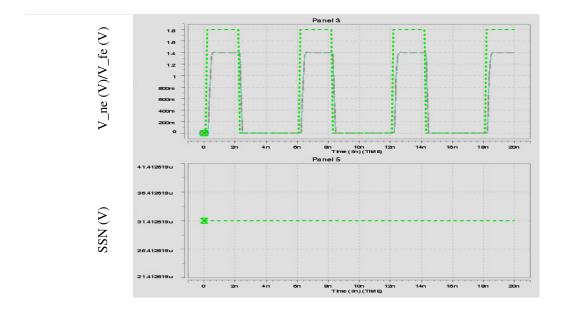

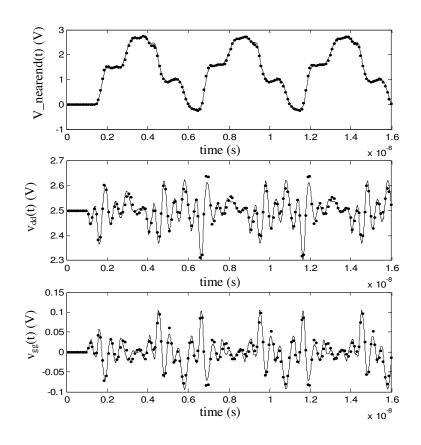

Another test case was generated where 10 identical weakly nonlinear drivers were each connected to a 25-ohm ideal transmission line that was in turn terminated by a 25-ohm matched resistor. Figure 1.11 shows the voltage at the near-end and far-end of the transmission line along with the SSN when all the 10 drivers switch simultaneously. Figure 1.12 shows the voltage waveforms at the near-end and the far-end of the transmission line along with SSN when 10 IBIS driver models switch simultaneously. It can be seen from Figure 1.12 that IBIS models fail to capture sensitive effects like SSN accurately. This is another limitation of IBIS driver models. IBIS driver models cannot be extended to multiple ports without losing accuracy.

**Figure 1.11** Voltage waveforms at the near-end and the far-end of the transmission line for a transistor-level driver circuit and SSN when multiple drivers are switching.

**Figure 1.12** Voltage waveforms at the near-end and the far-end of the transmission line for an IBIS driver model and SSN when multiple IBIS driver models are switching.

#### 1.3.3 IBIS Receiver Models

Receiver modeling also plays an important role in analyzing signal integrity issues for today's high-speed digital systems. IBIS receiver models are current industry standard.

In IBIS, a typical receiver circuit contains a ground (GND) clamp and a power clamp, as shown in Figure 1.13. The power and GND clamps represent the electrostatic discharge (ESD) structure. The IBIS receiver circuit also requires a logic voltage high threshold ( $v_{ih}$ ) and a voltage low logic threshold ( $v_{il}$ ) for the input. The IBIS simulator uses these logic threshold values to compute signal integrity issues such as overshoot/undershoot and noise margins [A37].

Figure 1.13 IBIS receiver model schematic.

The input model also includes the package parasitics and the input die capacitance, C\_comp. The C\_comp parameter is connected to the input, usually with reference to ground when the IBIS file is used in the simulator. It is the capacitance seen when looking from the pad back into the buffer. C\_comp is a key parameter, especially for

receiver inputs. In IBIS receiver modeling, the power and the GND clamp data are generated following the same procedure used for an IBIS driver model. The sweep voltage range will be –Vcc to Vcc for the GND clamp and Vcc to 2Vcc for the power clamp curve because the power clamp data is relative to Vcc as shown in equation (1.1).

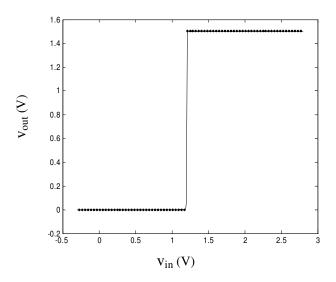

IBIS receiver models are highly based on the static characteristics of the receiver. A combination of clamping diodes does not accurately model the loading characteristics of the receiver circuit. The output characteristics of the receiver circuit cannot be modeled accurately by taking only the threshold voltages into account, as the delay information through the receiver is lost.

## 1.4 Proposed Research and Dissertation Outline

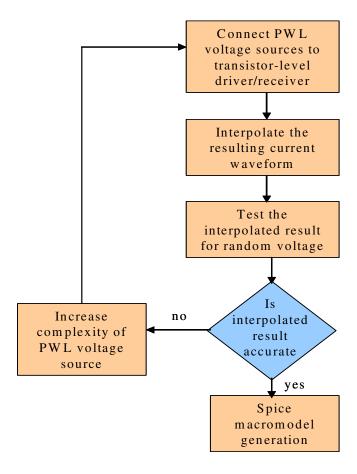

The key contribution of this work has been to develop different macromodels for different types of driver and receiver circuits that result in huge computational speed-up compared to actual transistor-level driver/receiver circuits and at the same time preserve accuracy. Both driver and receiver modeling approaches are black-box in nature. These macromodeling approaches can be extended to multiple ports to take into account the effect of power and ground nodes. Additionally, this work also focuses on macromodeling differential driver circuits and modeling driver circuits with pre-emphasis or pre-compensation effect. It is envisioned that the proposed research work will contribute toward generating macromodels for all classes of driver and receiver circuits. Figure 1.14 shows the flow chart of the general procedure involved in modeling driver and receiver circuits. It can bee seen that coming up with PWL voltage sources (identification signals) is ad hoc and it takes few hours to generate the macromodels of

driver and receiver circuits. But the time involved in modeling them is off-set by the fact that once driver or receiver circuits are modeled they become part of a library and can be used over and over again for numerous system level simulations.

Figure 1.14 Procedure for driver/receiver modeling

The following items are discussed in various sections of the dissertation.

Modeling driver circuits using the radial basis function (RBF) modeling approach. In

this approach, a nonlinear relation is drawn between the driver output current and

output voltage using summation of Gaussian functions. This represents previous work

done by the University of Torino, Italy [A38]. The advantages and limitations of this

method are discussed and validated on various test cases.

- 2. Modeling driver circuits based on their complexity:

- a) Weakly Nonlinear Driver Circuits: Driver circuits where the static characteristics dominate the dynamic characteristics of the driver. A modeling methodology based on static characteristics has been proposed to model these driver circuits. Static characteristic macromodels are accurate and (10 – 100)X faster than actual weakly nonlinear transistor-level driver circuits

- b) Moderately Nonlinear Driver Circuits: Spline function with finite time difference (SFWFTD) approach has been proposed to model moderately nonlinear driver circuits. This methodology takes into account both the static and the dynamic characteristics of the driver circuit. SFWFTD macromodels are (10 40)X faster than transistor-level driver circuits, depending on the driver being modeled

- c) Highly Nonlinear Driver Circuits: A modeling methodology based on recurrent neural networks (RNN) has been proposed to model highly nonlinear driver circuits. RNN network is a powerful nonlinear interpolation tool that can model highly nonlinear feedback memory systems. RNN models also provide (10 40) X speed-up over transistor-level driver circuits, depending on the kind of driver being modeled.

- d) Pre-compensation and pre-emphasis driver circuits are becoming popular in transmitting signal though lossy interconnects. Pre-emphasis driver circuits have been modeled accurately by including the effect of pre-compensation in the weighting functions.

All the above models are weakly sensitive to the external load connected to the driver. All these macromodels can capture sensitive effects like crosstalk and power supply noise accurately. The accuracy and computational speed-up of the above macromodels have been tested on different test cases and results have yielded good correlation with the actual transistor-level circuits.

3. Extension of the above modeling methods to multiple ports.

The developed modeling methodologies have been extended to multiple ports. These macromodels can capture the effect of power supply voltage and driver local ground on the driver output signal. These macromodels can also capture the effect of driver output signal on the power supply voltage and local ground. Capturing these sensitive relations can lead to the accurate modeling of sensitive effects like SSN when multiple drivers are switching. Macromodels generated using the proposed modeling techniques consume less CPU time and CPU memory compared to transistor-level driver circuits.

A full driver level simulation taking power supply node and ground node effects on the driver output has been performed using the above macromodels. Test results show good correlation between the transistor-level driver circuits and macromodels.

4. Modern high-speed digital interfaces have turned to low-voltage differential signaling (LVDS) because of their numerous advantages over single-ended signaling. Differential signals have lower voltage swings than single-ended signals. Differential signals have a reduced electromagnetic interference (EMI) effect and crosstalk coupling. A modeling methodology based on an RNN network has been proposed to macromodel differential drivers with and without the pre-emphasis/pre-compensation effect. The macromodels based on RNN networks are 10X faster and consume 10X less CPU memory compared to transistor-level driver circuits.

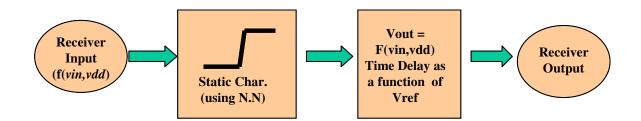

- 5. A modeling methodology for macromodeling receiver circuits has been proposed.

Receiver circuits are difficult to model, as the input to the receiver is analog in nature and the output is digital. Receiver modeling can be divided into macromodeling receiver input characteristics (where the receiver acts like a capacitive load) and receiver output characteristics (that forms input to logic circuits).

- a) Input characteristics of the receiver have been modeled by expressing receiver input current as a function of receiver input voltage using RNN function or SFWFTD approach.

- b) Output characteristics of the receiver have been captured by using a combination of voltage transfer characteristics of the receiver and a finite time delay element. The voltage transfer characteristics of the receiver can create the output voltage signature of the receiver accurately. The time delay of the signal through the receiver circuit has been accurately captured by the finite time delay element.

- c) The receiver circuit modeling technique has been extended to multiple-ports to include the effect of power supply voltage on both the receiver input and the receiver output characteristics.

The accuracy and simulation speed-up of the receiver macromodels has been compared to transistor-level receiver circuits for various test cases.

6. A scalable macromodeling approach for driver circuits has been proposed. The output voltage and current of a driver circuit are dependent on the power supply voltage, temperature, and process variation of the driver circuit. Variations in the above parameters affect the output voltage and the output current of driver circuits. Scalable driver macromodels that take into account the effect of temperature, power supply

voltage, and process variations help in efficiently analyzing signal integrity issues efficiently at an early stage of a design process. The scalability of the RNN modeling approach for both differential and single-ended driver circuits has been shown for some test cases.

The remainder of this thesis is organized as follows. In Chapter 2, the RBF modeling approach to model driver circuits is discussed along with its limitations. Chapter 2 also presents different macromodeling techniques for different classes of drivers. Depending on the complexity of the driver being modeled, a different nonlinear macromodeling method is required. Extension of the driver modeling approach to multiple ports has been discussed in Chapter 3. The accuracy of the modeling approach has been tested on various test cases. Modeling receiver circuits is described in Chapter 4. Receiver circuits also play an important role in signal integrity and power integrity analysis. In this chapter, modeling receiver input and output characteristics are explained in detail. Chapter 5 discusses the modeling of differential driver circuits. Differential signaling reduces EMI effects, crosstalk coupling, and high voltage swings. Macromodeling differential driver circuits with and without pre-emphasis is discussed in this chapter. Chapter 6 discusses the scalability of driver circuits. Chapter 7 concludes the thesis with future work.

## **CHAPTER II**

### MACROMODELING OF DIGITAL DRIVERS

It has been seen from Chapter I that while IBIS models are fast, they cannot accurately model the nonlinear dynamic characteristics of driver circuits. Therefore, IBIS models are more suitable to model driver circuits that are weakly nonlinear in nature.

In this chapter, radial basis function (RBF) modeling approach for modeling driver circuits has been discussed [A38]. This approach is the previous work done by Prof. Canavero's group at University of Torino, Italy [A38]. In this modeling approach, the driver output current is expressed in terms of driver output voltage using a summation of radial basis functions, usually Gaussian functions. RBF functions can accurately model the nonlinearity of driver circuits, but RBF models also have their limitations. In this chapter, the advantages and limitations of this method are discussed and validated on various test cases.

Driver circuits can be broadly classified into three groups depending on their nonlinearity: 1) weakly nonlinear driver circuits, 2) moderately nonlinear driver circuits, and 3) highly nonlinear driver circuits. In weakly nonlinear driver circuits, the static nonlinear characteristics dominate the dynamic nonlinear characteristics. These driver circuits have little or no memory in them. In this chapter, a modeling approach based on static characteristics has been proposed for weakly nonlinear driver circuits. Moderately nonlinear driver circuits have memory in them and therefore, the dynamic characteristics

cannot be ignored. Driver circuits with memory act as a feedback system; the output at time instance't' is dependent on previous time instances of the output. The nonlinearity of a circuit can be gauged based on the number of previous time steps needed to model the output accurately. In case of moderately nonlinear driver circuits, the output value at previous one or two time instances has to be taken into account. For highly nonlinear driver circuits, the output values of previous two or more instances have to be taken into account. Spline function with finite time difference (SFWFTD) modeling has been proposed to model moderately nonlinear driver circuits in this chapter. For highly nonlinear driver circuits, recurrent neural network (RNN) modeling has been proposed. Highly nonlinear circuits have large memory or feedback effect. In a highly nonlinear driver circuit, dynamic characteristics of the driver circuit dominate the static characteristics. RNN is a special branch of artificial neural networks (ANN) that model nonlinear systems with feedback accurately. All the above mentioned macromodels are black-box in nature, faster than transistor-level driver circuits, weakly sensitive to the external load connected, and at the same time maintain high accuracy.

In this chapter, static characteristics modeling technique, SFWFTD modeling technique, and RNN modeling technique are discussed in detail in sections 2.3, 2.4, and 2.5, respectively. Spice netlist generation for all these macromodels has also been described in these sections. Macromodel to hardware measurement correlation has been shown in section 2.6. Pre-emphasis/pre-compensation driver circuits that are used to drive signals through extremely lossy lines have been modeled in section 2.7. The accuracy of these macromodels has been tested on numerous test cases and results show good correlation between the macromodel and the transistor-level circuit waveforms.

## 2.1 Radial Basis Function Based Modeling

RBF modeling technique is a parametric modeling technique in which a nonlinear relation is drawn between the output current and the output voltage of a driver circuit. The output current and output voltage are related using a piece-wise (PW) parametric equation as shown below:

$$i_{\alpha}(k) = w_1(k)f_1(\Theta_1, x(k)) + w_2(k)f_2(\Theta_2, x(k))$$

(2.1)

$$f_n(\Theta_n, x(k)) = \sum_{j=1}^M \theta_{nj} \phi \Big( |x - cnj|, \beta \Big), n = 1, 2$$

(2.2)

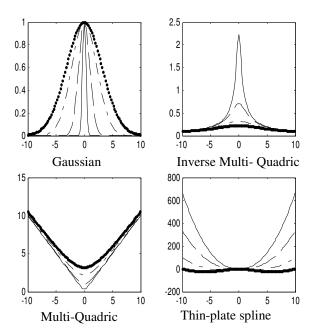

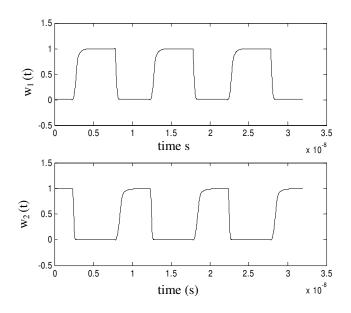

In equation (2.1),  $i_o$  is the driver output current,  $f_I$  and  $f_2$  are the sub-models that relate the driver output current to the output voltage for driver input HIGH and LOW, respectively [B1]. The transition from one logic state to another is done with the help of weighting functions  $w_I$  and  $w_2$ . The time-varying weighting functions act as switches between the sub-models  $f_I$  and  $f_2$ . Sub-models  $f_I$  and  $f_2$  are expressed as a summation of radial basis functions, as shown in equation (2.2), where M is the number of basis functions needed for  $f_I$  or  $f_2$  to accurately model the digital driver. Gaussian, Multi-quadric, and thin-plate spline are some of the radial basis functions as shown in Figure 2.1. In equation (2.2),  $\Phi$  is the asymptotically increasing or decreasing basis function and  $\theta_I$  is the weight of the basis function  $\Phi$ . The centers of the basis functions are defined by  $e_I$  and the width or the spread parameter is defined by  $e_I$  [B2].

The regressor vector x in equation (2.2) collects the past r samples of the driver output voltage ( $v_o$ ) and the driver output current ( $i_o$ ) along with the present sample of the driver output voltage. The parameter r has been called the dynamic order of the model. The

dynamic order for driver changes, depending on the complexity of the driver that is being modeled [B3].

$$x^{T}(k) = \begin{cases} i_{o}(k-1), i_{o}(k-2), \dots, i_{o}(k-r), \\ v_{o}(k), v_{o}(k-1), \dots, v_{o}(k-r) \end{cases}$$

(2.3)

Figure 2.1 Different radial basis functions with varying widths.

This modeling technique can be extended to multiple ports by changing the *regressor* vector x. To include the effect of the power supply  $v_{dd}$ , the *regressor* vector x should be modified as shown:

$$x^{T}(k) = \begin{cases} i_{o}(k-1), i_{o}(k-2), \dots, i_{o}(k-r), \\ v_{o}(k), v_{o}(k-1), \dots, v_{o}(k-r), \\ v_{dd}(k), v_{dd}(k-1), \dots, v_{dd}(k-r) \end{cases}$$

(2.4)

A set of identification signals are used at the output of the driver for driver input HIGH and LOW to estimate  $f_1$  and  $f_2$ , respectively. These identification signals are generated from a piece-wise linear (PWL) voltage source connected at the driver output.

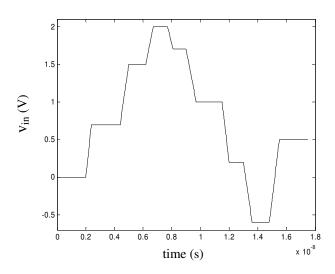

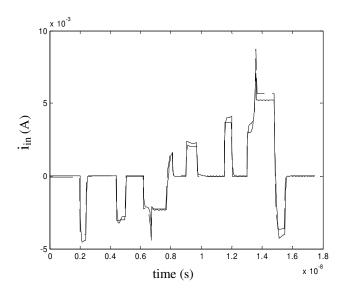

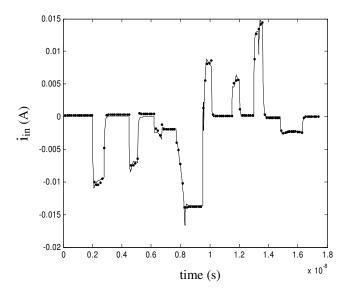

The voltage waveform has different slopes and different rise times to capture all the dynamic and static characteristics of the driver. These identification signals have to be carefully generated to excite all the dynamic characteristics of the driver [A38]. Figure 2.2 shows the voltage identification signal at the output of the IBM driver ('Bt3350') to estimate sub-model  $f_I$  for 1ns rise time. Figure 2.3 shows the corresponding current waveform at the IBM driver output when the input is held HIGH.

**Figure 2.2** Voltage Identification signal at the driver output to estimating  $f_1$  for 1ns rise time.

**Figure 2.3** Current Identification signal at the driver output corresponding to Figure 2.2.

Sub-models  $f_1$  and  $f_2$  are parameterized using the classical Gram-Schmidt (CGS) method in [B4]. Sub-models  $f_{1,2}$  in equation (2.1) can be expressed as:

$$f_n = \Phi\theta \; ; \quad n = 1,2 \tag{2.5}$$

where,

$$f_n = [f_n(1), f_n(2), \dots, f_n(N)]^T$$

, (2.6)

$$\Phi = \left[\Phi_1, \Phi_2, \dots, \Phi_M\right],\tag{2.7}$$

and

$$\Phi_i = [\Phi_i(1), \Phi_i(1), \dots, \Phi_i(N)]^T, \quad 1 \le i \le M$$

(2.8)

$$\theta = \left[\theta_1, \theta_2, \dots, \theta_M\right]^T \tag{2.9}$$

where N is the number of data points and M is the number of basis functions needed to estimate sub-models  $f_1$  or  $f_2$ . The regression matrix  $\Phi$  can be decomposed into

$$\Phi = WA \tag{2.10}$$

where A is an M X M triangular matrix with 1's on the diagonal and 0's below the diagonal and W is an N X M matrix with orthogonal columns  $w_i$ .

$$W^T W = D (2.11)$$

where D is a diagonal matrix with elements  $d_i$ .

$$d_{i} = w_{i}^{T} w_{i} = \sum_{t=1}^{N} w_{i}(t) w_{i}(t), \ 1 \le i \le M$$

(2.12)

The CGS method computes one column of A at a time, orthogonalizing  $\Phi_i$  into set of orthogonal basis vector [B5]. At the  $k^{th}$  stage, it makes the  $k^{th}$  column orthogonal to each

of the k-1 previously orthogonalized columns and the operation repeats for  $k = 2,3, \dots$ , M-1, M.

Once sub-models  $f_1$  and  $f_2$  are estimated, the time-varying weighting functions  $w_1$  and  $w_2$  can be calculated by solving equation (2.1) for two different loads. A resistive load is picked as one load and a series connection of a resistor and a battery is picked as another load.

#### 2.1.1 Limitations of RBF Modeling Approach

Even though RBF modeling approach accurately models transistor-level driver circuits, it has some inherent limitations. One of the limitations is that the CGS method that is used to estimate the RBF function parameters is very sensitive to round-off errors. If  $\Phi$  from equation (2.10) is ill-conditioned, then the resulting W would lose its orthogonality and re-orthogonalization would be necessary. Another limitation with RBF modeling approach is that with the decrease in input rise time for a driver circuit, the dynamic characteristics of the driver start dominating the static characteristics, which will lead to an increase in the number of basis functions needed to accurately model the driver circuit, as shown in Table 2.1. Table 2.1 shows that with the decrease in rise time for an IBM driver ('AGP'), there is an increase in the number of basis functions needed to model the driver circuit.

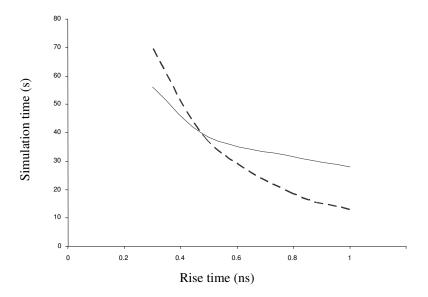

Increase in the number of basis functions results in increase in the complexity of the RBF driver models which in turn results in increase in the simulation time. Figure 2.4 shows how the number of basis functions increase the simulation time for the RBF driver

modeling. From numerous experiments it has been found that increase in basis functions also results in poor numerical convergence with Hspice circuit simulator [B8].

**Table 2.1** Driver input rise time Vs. number of basis functions needed.

| Identification signal rise times | Gaussian function |       |

|----------------------------------|-------------------|-------|

|                                  | $f_1$             | $f_2$ |

| 1ns                              | 6                 | 6     |

| 0.8ns                            | 5                 | 5     |

| 0.5ns                            | 11                | 11    |

| 0.3ns                            | 13                | 17    |

**Figure 2.4** Driver input rise time Vs. simulation time required for transistor-level IBM driver (straight line) and RBF driver model (dashed line).

Also, RBF models cannot accurately model highly nonlinear driver circuits. In highly nonlinear circuits the memory or feedback effect is predominant. A test case has been generated to demonstrate the failure of RBF models in capturing highly nonlinear driver

circuits. A detailed description of the test case is discussed later in section 2.4.2 of this chapter. Finally, RBF modeling approach has some numerical convergence issues with Hspice when the modeling approach is extended to multiple ports in order to capture sensitive effects like simultaneous switching noise (SSN).

### 2.2 Classification of Driver Circuits

Representation of sub-models  $f_1$  and  $f_2$  using RBFs is not the best way to model nonlinear driver circuits. In this chapter, it has been proposed that different representations of sub-models  $f_1$  and  $f_2$  result in efficient modeling of different groups of driver circuits. To model weakly nonlinear driver circuits IBIS and static characteristic models are efficient. RBF and SFWFTD models are efficient in modeling moderately nonlinear driver circuits. RNN models are efficient in modeling highly nonlinear driver circuits.

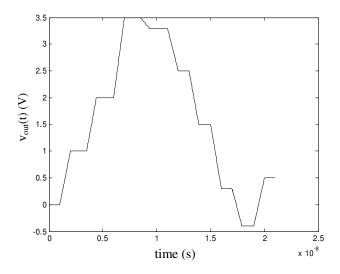

To decide which category the transistor-level driver circuit belongs to, a PWL voltage source is connected at the output of a driver circuit. This PWL voltage source is similar to the one explained in section 2.1 with different rise times and steady state values. If the transition from one steady state to another in the PWL voltage source results in similar transformation of the resulting driver output current signature, then the driver is weakly nonlinear. IBIS and static characteristic models are efficient in modeling these driver circuits. Static characteristic models are better than IBIS models and the former can be extended to multiple ports. Sometimes the resultant driver output current signature has some additional dynamic characteristics every time the PWL voltage source makes a transition from one steady state to another. These dynamic characteristics result in current

spikes at transitions and make the current signature different from the voltage signature. Drivers that belong to this category are termed as moderately nonlinear. RBF and SFWFTD are efficient in modeling these driver circuits. SFWFTD models are simple to generate and do not have convergence issues with Hspice compared to RBF models. If the resultant current signature does not resemble the PWL voltage waveform then the driver is highly nonlinear and it has memory or feedback in it. RNN models are efficient in modeling highly nonlinear driver circuits.

## 2.3 Static Characteristic Modeling

For weakly nonlinear driver circuits, the speed and memory advantages of RBF models are not predominant as explained in section 2.1. For this class of drivers, IBIS models are more suitable as they retain both speed and accuracy. The problem with IBIS models is that these models cannot be extended to multiple ports to capture sensitive effects like SSN. Static characteristic models can be extended to multiple ports without losing accuracy. In driver circuits with little memory, the static characteristics of the driver circuit dominate the dynamic characteristics for normal excitations. Therefore, a static characteristic relation can be used in relating the driver output current to the output voltage [B6]. The driver output current can be expressed as:

$$i_o(v_o(t) = w_1(t)f_1(v_o(t)) + w_2(t)f_2(v_o(t))$$

(2.13)

where  $i_o$  is the driver output current,  $v_o$  is the driver output voltage, and  $w_1$  and  $w_2$  are weighting functions that help sub-models  $f_1$  and  $f_2$  transit from one state to another. Sub-models  $f_1$  and  $f_2$  in equation (2.13) can be represented as:

$$f_n(v_o(t)) = a_{m,n}v_o^m + a_{(m-1),n}v_o^{(m-1)} + \dots + a_{o,n}; n = 1,2$$

(2.14)

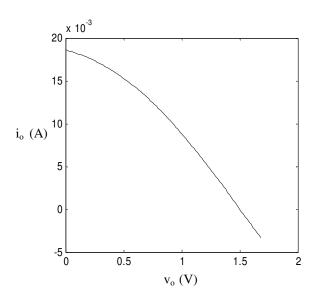

In equation (2.14), a's are constants that depend on the kind of driver being modeled and the value of m is of the order 1 to 5. For an IBM driver ('BagpV3V2'), the output current vs. output voltage plot when the driver input is held HIGH is shown in Figure 2.5

**Figure 2.5** DC relation between driver output current and output voltage when driver input is HIGH.

It can be seen from Figure 2.5 that the output current can be expressed as a function of output voltage, as shown in equation (2.14). Similarly, the driver output current can be expressed using equation (2.14) when the driver input is held LOW. The whole process of computing sub-models  $f_1$  and  $f_2$  is computationally simple.

Once sub-models  $f_1$  and  $f_2$  are estimated, weighting functions  $w_1$  and  $w_2$  can be estimated by linear inversion of equation (2.13) for two different loads as shown: