## ELECTROMAGNETIC MODELING OF INTERCONNECTIONS IN THREE-DIMENSIONAL INTEGRATION

A Dissertation Presented to The Academic Faculty

By

Ki Jin Han

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in Electrical and Computer Engineering

School of Electrical and Computer Engineering Georgia Institute of Technology August 2009

Copyright  $\bigodot$  2009 by Ki Jin Han

# ELECTROMAGNETIC MODELING OF INTERCONNECTIONS IN THREE-DIMENSIONAL INTEGRATION

Approved by:

Dr. Madhavan Swaminathan, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Andrew E. Peterson School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Emmanouil M. Tentzeris School of Electrical and Computer Engineering Georgia Institute of Technology Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering Georgia Institute of Technology

Dr. Hao-Min Zhou School of Mathematics Georgia Institute of Technology

Date Approved: May 7, 2009

To my family

### ACKNOWLEDGMENTS

I would like to express my gratitude to the people who inspired and encouraged me during four years of my Ph.D. research in Georgia Tech. Without their supports, my dissertation would not been completed.

Firstly, I would like to thank my academic advisor, Dr. Madhavan Swaminathan, for giving me an invaluable opportunity to work in *EPSILON* Group. By his insight based on theoretical and industrial background, my research could be guided in the right way. Also, his enthusiasm for research became my role model as an engineering researcher. I would like to express my gratitude to Dr. Andrew E. Peterson, Dr. Emmanouil M. Tentzeris, Dr. Saibal Mukhopadhyay, and Dr. Hao-Min Zhou, for their important advices and comments for my dissertation as committee members.

I give my thanks to all of current colleagues in *EPSILON* Group. Dr. Daehyun Chung and Dr. Sunghwan Min have been excellent mentors to me during the last year of my Ph.D. work. It would be another good experience to discuss with Dr. Larry Carastro. I feel happy to have been working with *EPSILON* colleagues: Nevin Altunyurt, Tapobrata Bandyopadhyay, Nithya Sankaran, Abhilash Goyal, Bernie J. Yang, Jae Young Choi, Myunghyun Ha, Narayanan T. V., Rishiraj A. Bheda, Seunghyun E. Hwang, Suzanne L. Huh, and Jianyong Xie, and other colleagues: Mohit Pathak, Vishwanath Natarajan, Hyun Choi, Sehun Kook, and Deuk Kyu Lee. I remember all the supports of these brilliant young people, and hope they will finish their Ph.D. work successfully.

I would like to acknowledge former researchers and alumni of *EPSILON* Group. Dr. Ege Engin had supported my research for three years with his strong background in modeling research. Dr. Andy Seo helped important software work for me. I give my thank to Mr. Hayato Takeuchi in Sony Corporation, for guiding me to the high-speed digital design area during the passive equalization project. I could obtain countless insights and ideas through the discussions with Dr. Krishna Bharath, Dr. Krishna Srinivasan, Dr. Subramanian N. Lalgudi, Dr. Tae Hong Kim, Dr. Wansuk Yun, Dr. Souvik Mukherjee, Ms. Aswani Kurra, Mr. Sukruth G. Pattanagiri, Mr. Ranjeeth Doppalapudi, Mr. Vishal Laddha, Ms. Janani Chandrasekhar, Ms. Marie-Solange Milleron, and Mr. Abdemanaf Tambawala. Valuable achievements of Dr. Prathap Muthana, Dr. Amit Bavisi, Dr. Rohan Mandrekar, Dr. Jinwoo Choi, and all of other alumni were the basis of my research. I hope all *EPSILON* alumni will score a big success in their careers.

Finally, I would like to give my sincere thank to my family. All of my accomplishments through my life have been realized by endless loves and supports of my father, late Mr. Choon Woo Han, and my mother, Ms. Hoon Yong Eom. My parents showed me their positive attitude to life and encouraged me whenever I was in difficult time. I deeply appreciate all the gifts from my parents. I also would like to thank my father-in-law and mother-in-law for their careful concern from Korea. Supports of my sisters and brothers-in-law have been a big help from my childhood to now for finishing my Ph.D. work. My nephews and nieces, Ji Won, Jae Yun, Jun Hyuk, and Yun Seo, always have brought joy and delight to me. Lastly, but not the least, I would like to give my special thank to my dear wife, Ms. Yu Min Joo, for her love and encouragement. For over one year, she supported and inspired my life and work everyday, with enduring my overnight work habit. Her love and friendship are great gifts in my life. I wish all my family health and happiness.

## TABLE OF CONTENTS

| ACKNO  | OWLEDGMENTS                                                       | iv |

|--------|-------------------------------------------------------------------|----|

| LIST O | F TABLES                                                          | ix |

| LIST O | F FIGURES                                                         | x  |

| SUMM   | ARY                                                               | xv |

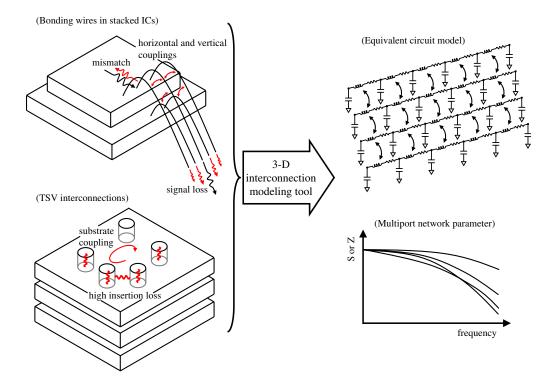

| CHAPT  | TER 1 INTRODUCTION                                                | 1  |

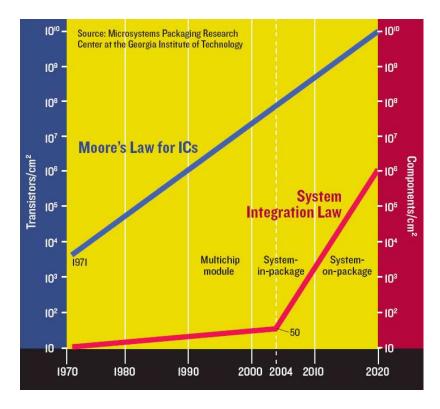

| 1.1    | Need for 3-D Technology in System Integration                     | 2  |

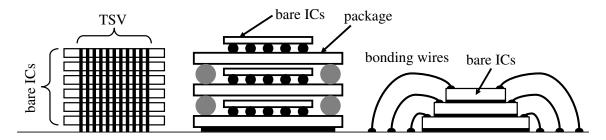

| 1.2    | Interconnection Elements in 3-D Integration                       | 4  |

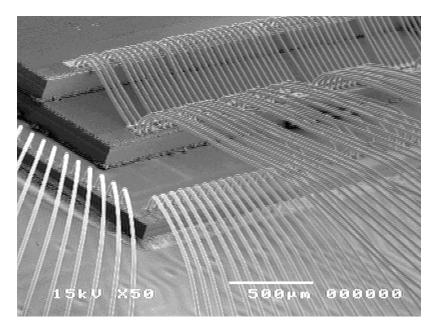

|        | 1.2.1 Bonding Wire Interconnections                               | 4  |

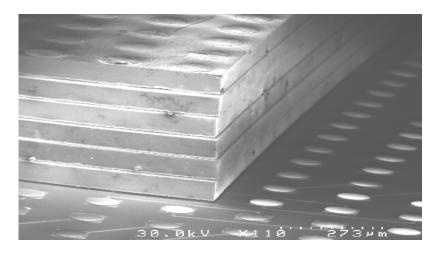

|        | 1.2.2 Through-Silicon Via (TSV) Interconnections                  | 6  |

| 1.3    | Electrical Modeling Issues in 3-D Interconnection Design          | 7  |

| 1.4    | Previous Research on Modeling 3-D Interconnections                | 8  |

|        | 1.4.1 Measurement-based and Analytic Modeling Methods             | 10 |

|        | 1.4.2 EM Simulation Methods for 3-D Electrical Interconnections . | 13 |

| 1.5    | Completed Research                                                | 21 |

| 1.6    | Dissertation Outline                                              | 23 |

| CHAPT  | TER 2 INDUCTANCE AND RESISTANCE EXTRACTIONS                       | 3  |

|        | OF CYLINDRICAL INTERCONNECTIONS                                   | 25 |

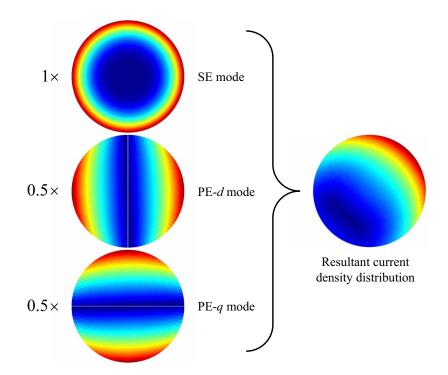

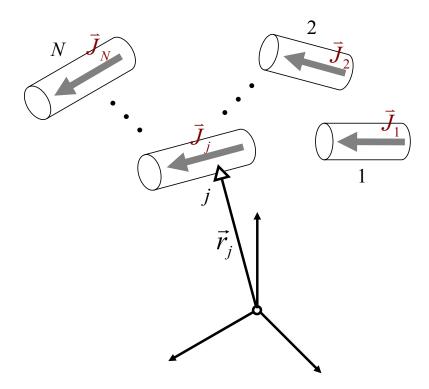

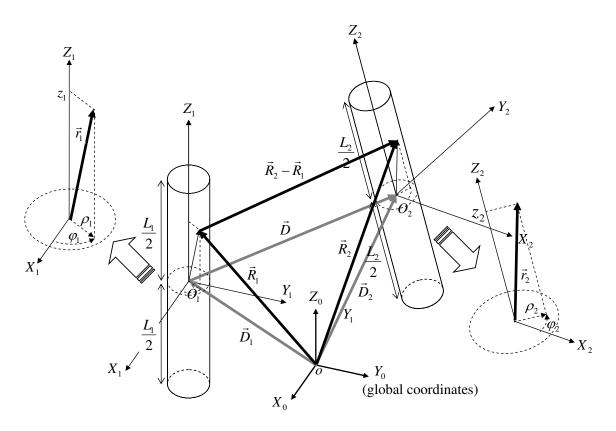

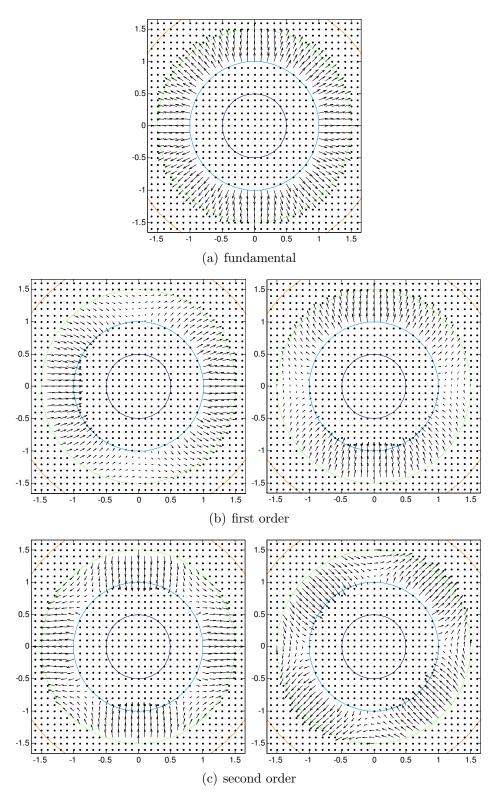

| 2.1    | Formulation of EFIE with Cylindrical CMBFs                        | 26 |

|        | 2.1.1 Cylindrical CMBF                                            | 26 |

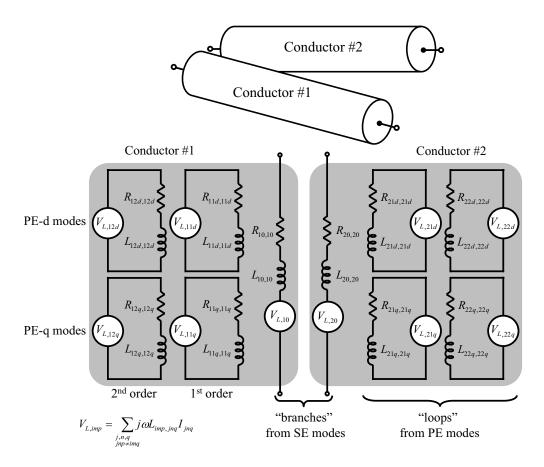

|        | 2.1.2 EFIE Formulation                                            | 29 |

| 2.2    | Efficiency Enhancements and Implementation                        | 38 |

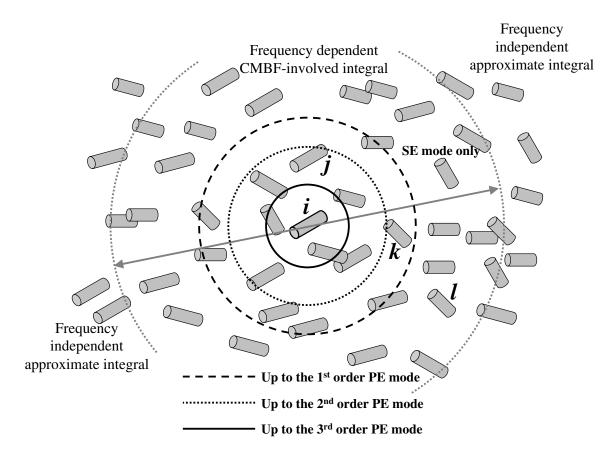

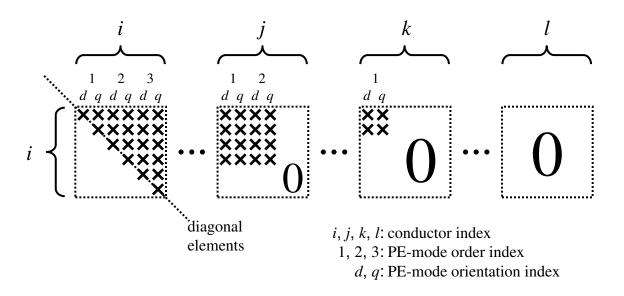

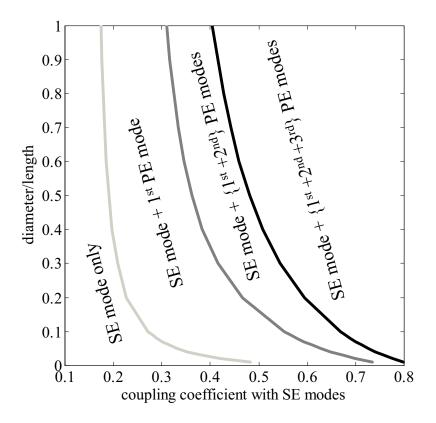

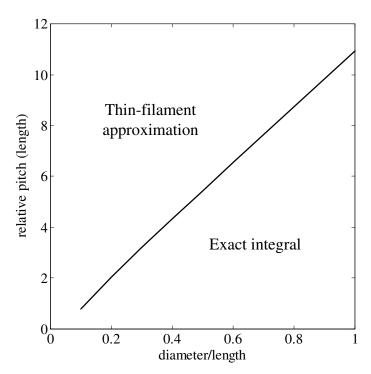

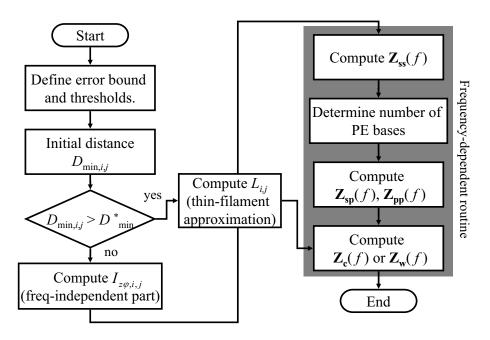

|        | 2.2.1 Controlling the Number of PE-Mode Basis Functions           | 39 |

|        | 2.2.2 Multi-Function Method (MFM)                                 | 42 |

|        | 2.2.3 Implementation of Modeling Tool                             | 44 |

| 2.3    | Validation                                                        | 45 |

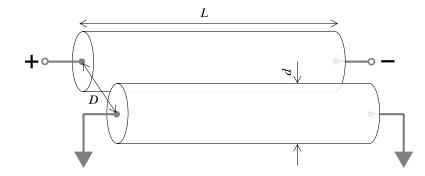

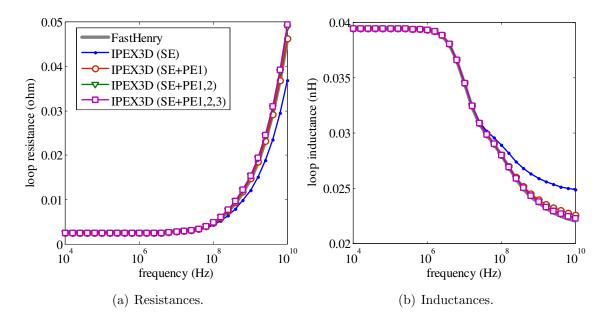

|        | 2.3.1 Convergence Study with Two Parallel Cylindrical Conductors  | 45 |

|        | 2.3.2 Accuracy Validation with Three Cylindrical Conductors       | 46 |

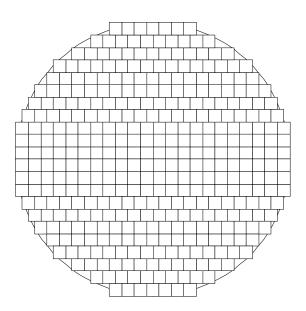

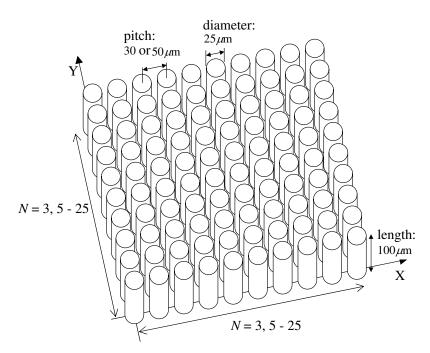

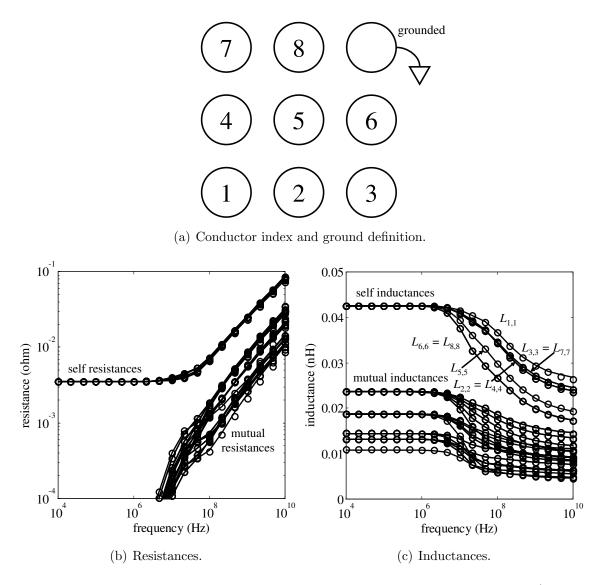

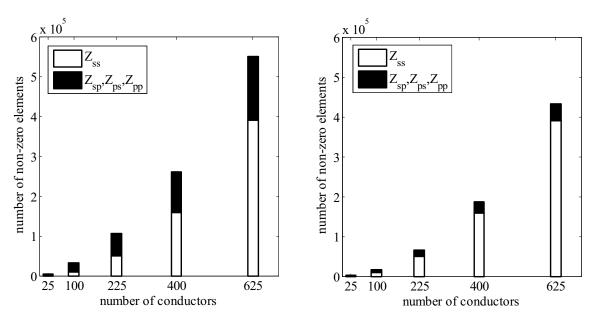

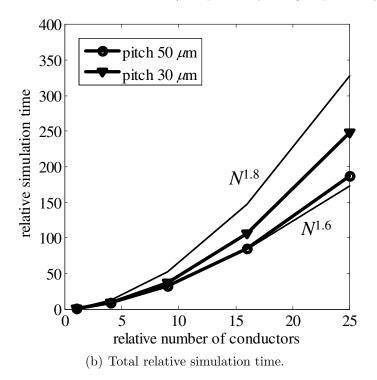

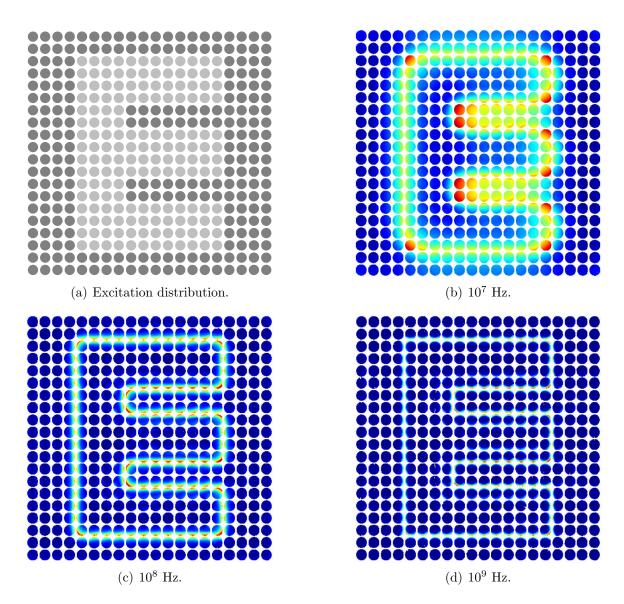

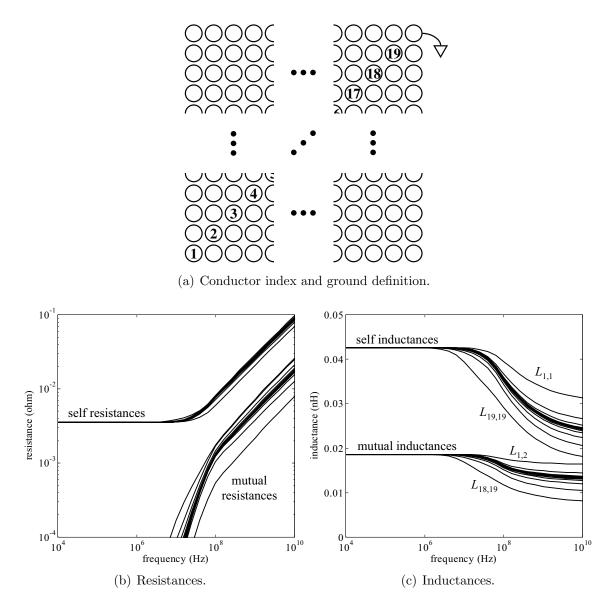

|        | 2.3.3 Scalability Analysis with THV Array                         | 50 |

| 2.4    | Summary                                                           | 54 |

| CHAPT  | TER 3 CAPACITANCE AND CONDUCTANCE EXTRAC-                         |    |

|        | TION OF CYLINDRICAL INTERCONNECTIONS                              |    |

|        | FOR BROADBAND MODELING                                            | 57 |

| 3.1    | Cylindrical AMBF                                                  | 58 |

| 3.2    | SPIE Formulation in Free Space                                    | 60 |

| 3.3    | Consideration of Homogeneous Media                                | 62 |

|        | 3.3.1 Vector and Scalar Potentials                                | 62 |

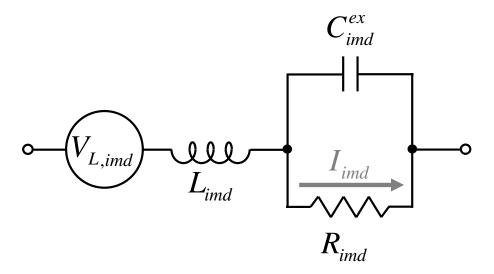

|                                                              | 3.3.2 Eq                                                                                                                                                                                                                                                                                                                                                                                 | uivalent Circuit Model of Conductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 64                                                                                                                       |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

|                                                              | 3.3.3 Co                                                                                                                                                                                                                                                                                                                                                                                 | nsideration of Dispersive Media                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66                                                                                                                       |

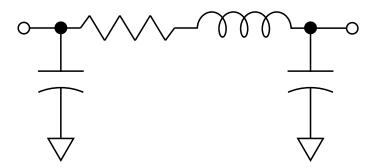

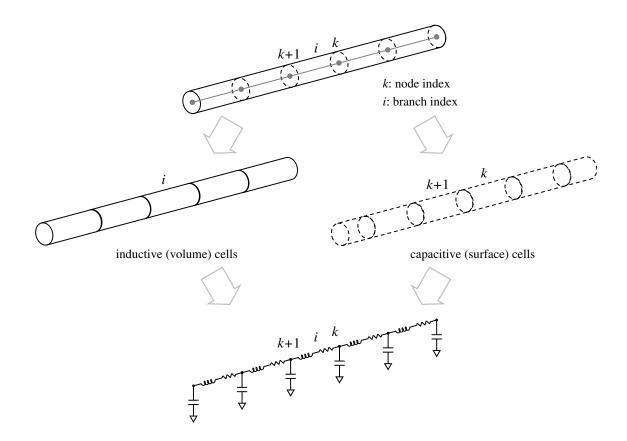

| 3.4                                                          | Broadband                                                                                                                                                                                                                                                                                                                                                                                | d Equivalent Circuit ( <i>RLC</i> Network)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66                                                                                                                       |

| 3.5                                                          | Capacitan                                                                                                                                                                                                                                                                                                                                                                                | ce Computation Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70                                                                                                                       |

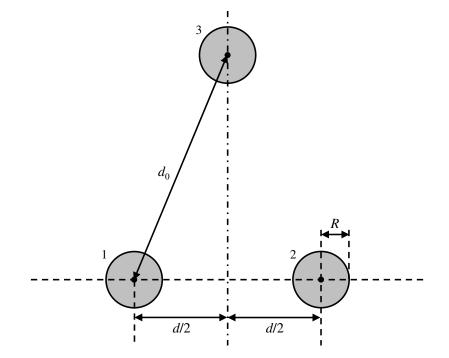

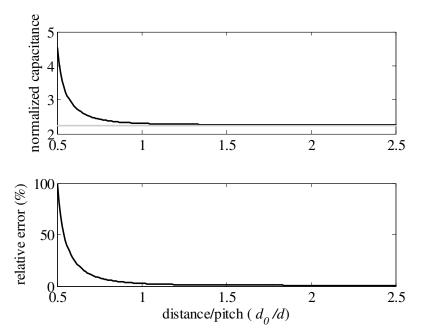

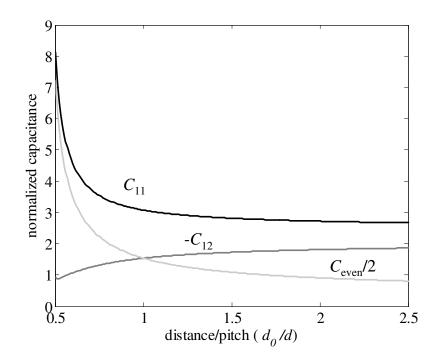

|                                                              | 3.5.1 Eve                                                                                                                                                                                                                                                                                                                                                                                | en- and Odd-Mode Capacitances of a Triplex Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70                                                                                                                       |

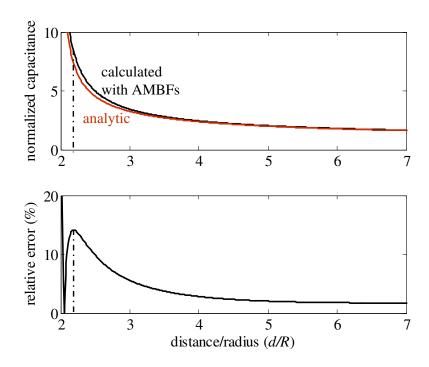

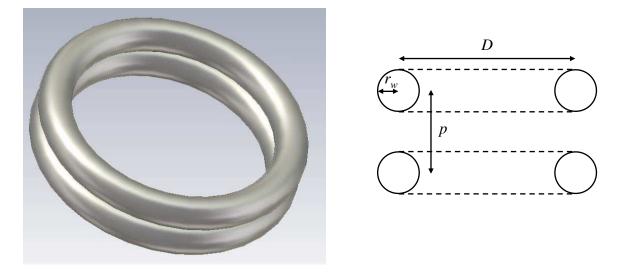

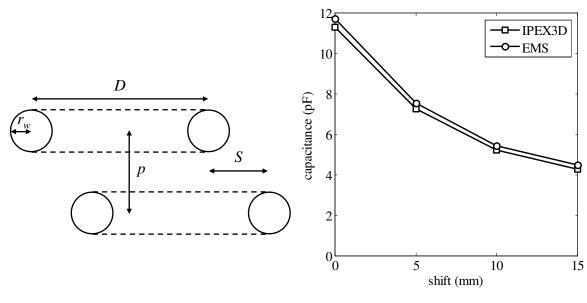

|                                                              | 3.5.2 Str                                                                                                                                                                                                                                                                                                                                                                                | ay Capacitance of a Two-Turn Solenoidal Inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                                                                                                                       |

| 3.6                                                          | Summary                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76                                                                                                                       |

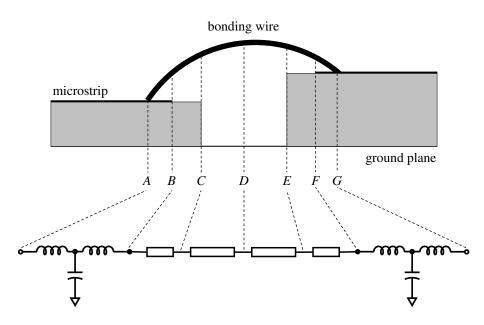

| CHAPT                                                        |                                                                                                                                                                                                                                                                                                                                                                                          | MODELING OF BONDING WIRE INTERCONNEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                                                        |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                          | FIONS IN STACKED ICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 77                                                                                                                       |

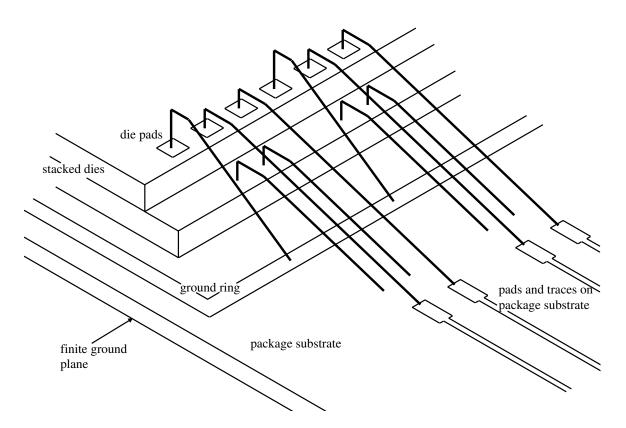

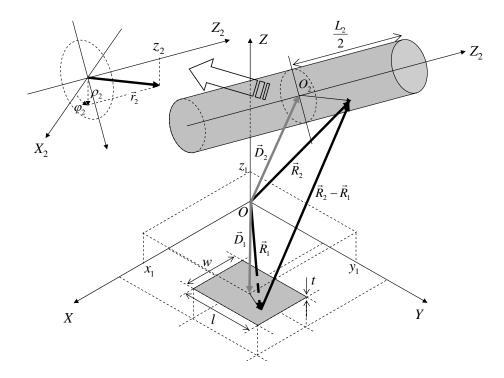

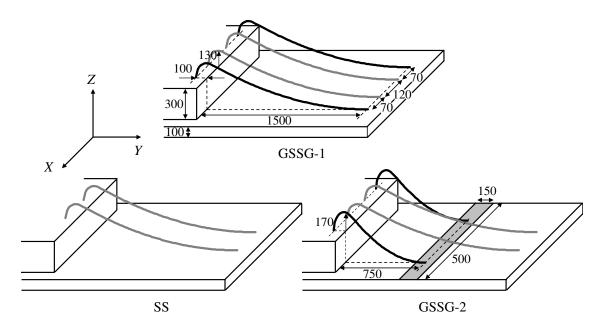

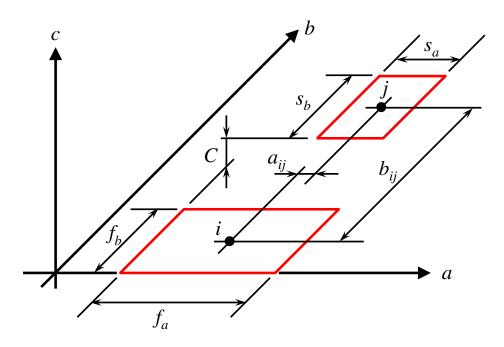

| 4.1                                                          | • •                                                                                                                                                                                                                                                                                                                                                                                      | onding Wire Configuration in Stacked ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 78                                                                                                                       |

| 4.2                                                          |                                                                                                                                                                                                                                                                                                                                                                                          | from Planar Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 79                                                                                                                       |

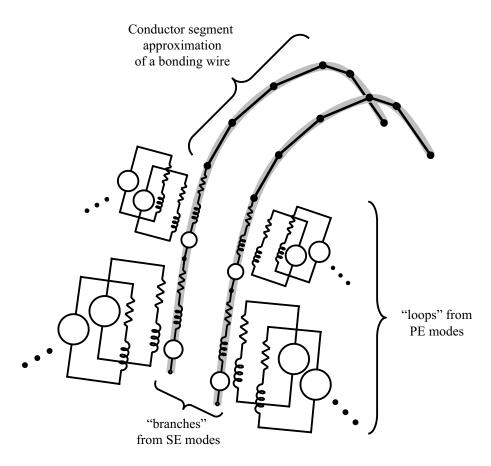

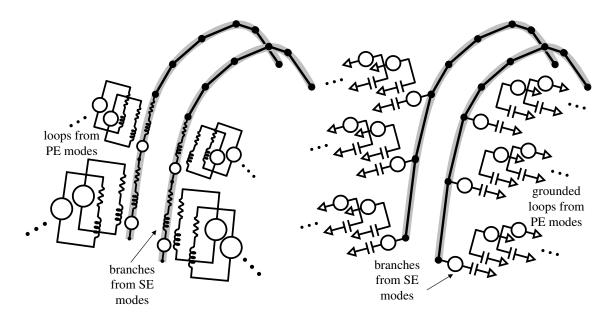

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                          | mbination with Conventional PEEC Method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80                                                                                                                       |

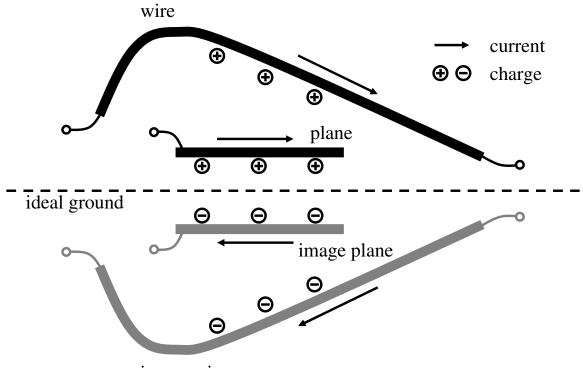

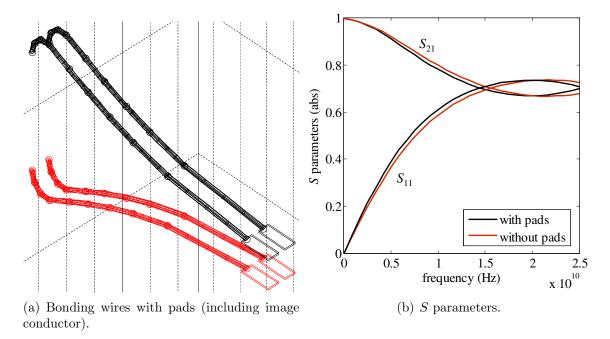

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                          | age Method for Modeling Infinite Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83                                                                                                                       |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                          | lidation: Single Cylinder on Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 84                                                                                                                       |

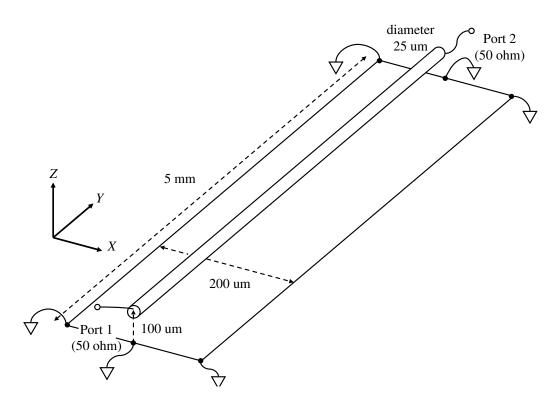

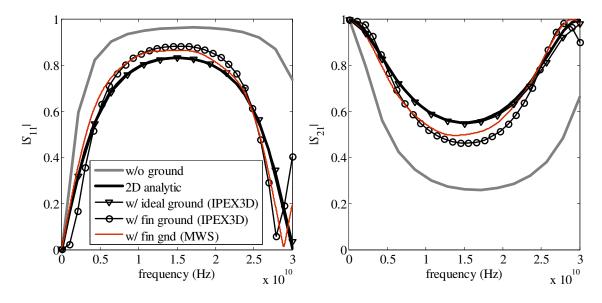

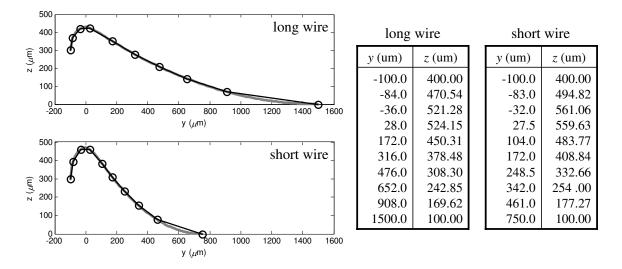

| 4.3                                                          |                                                                                                                                                                                                                                                                                                                                                                                          | Vire Modeling Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87                                                                                                                       |

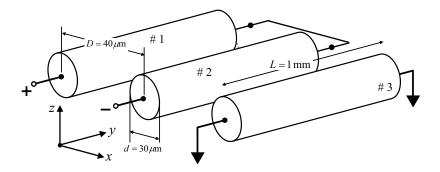

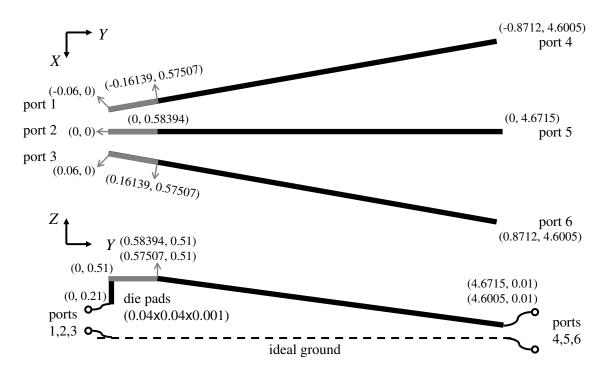

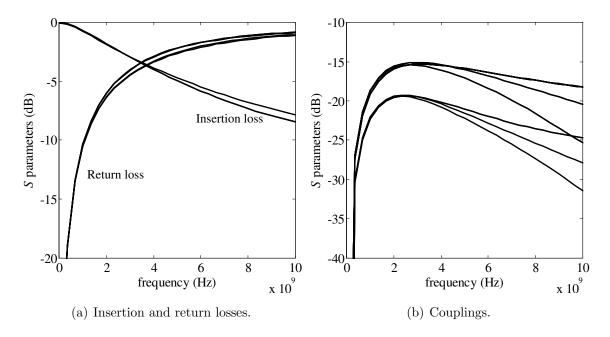

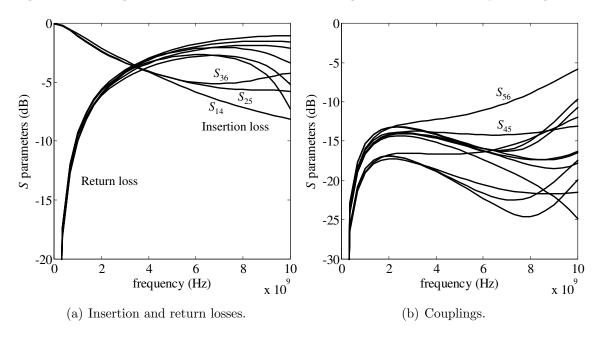

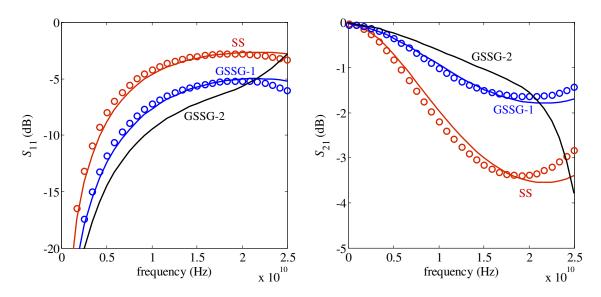

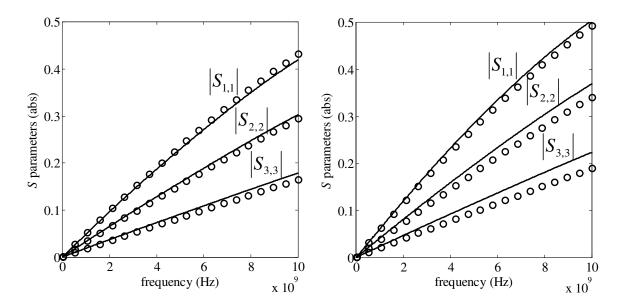

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                          | ree JEDEC4 Type Bonding Wires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87                                                                                                                       |

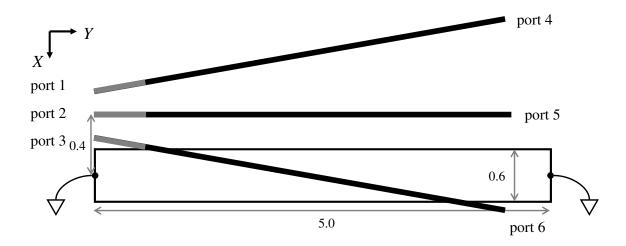

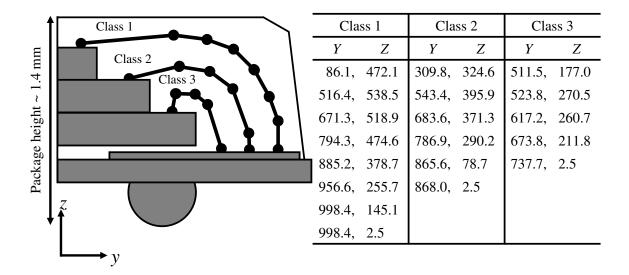

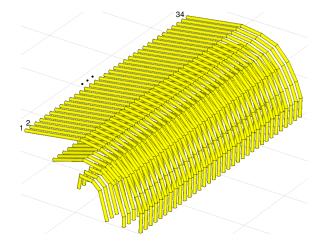

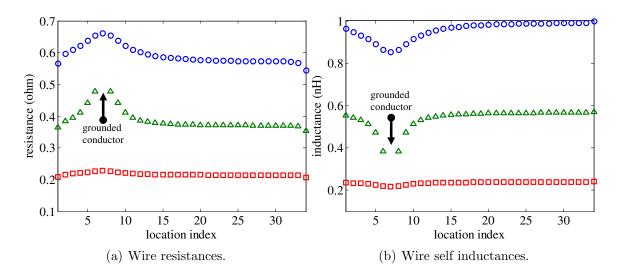

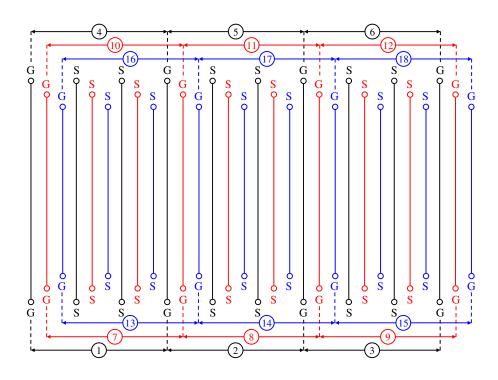

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                          | nding Wires in a Plastic Ball Grid Array (PBGA) Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 88                                                                                                                       |

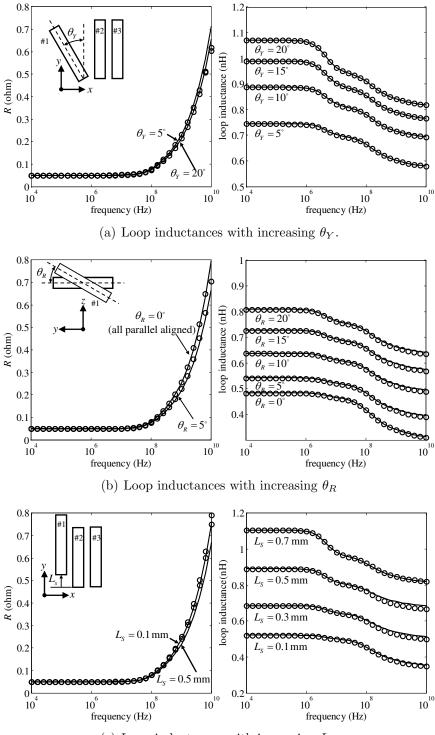

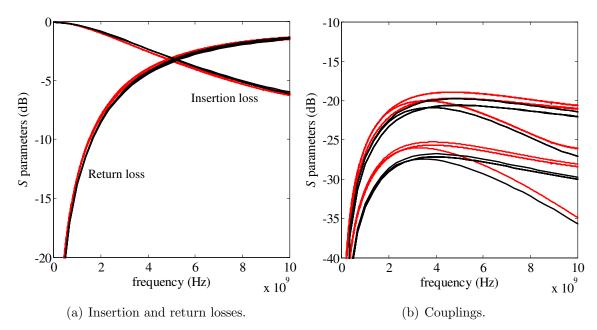

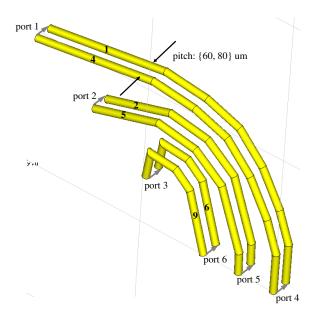

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                          | nding Wires in Three Stacked ICs: The Effect of Vertical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                          |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                          | upling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93                                                                                                                       |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                          | mparison of Simulation Time with a Full-Wave EM Simulato                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                          |

| A                                                            | Summon                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100                                                                                                                      |

| 4.4                                                          | Summary                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100                                                                                                                      |

| 4.4<br>CHAP                                                  | v                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                          |

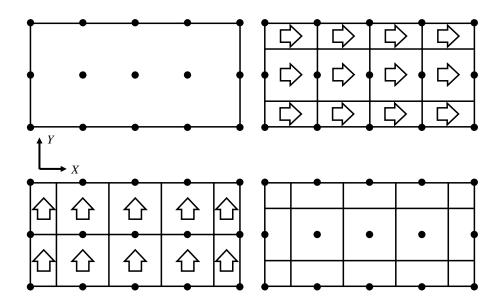

|                                                              | TER 5 N                                                                                                                                                                                                                                                                                                                                                                                  | MODELING OF THROUGH SILICON VIA (TSV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                          |

|                                                              | TER 5 N<br>I                                                                                                                                                                                                                                                                                                                                                                             | MODELING OF THROUGH SILICON VIA (TSV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | )                                                                                                                        |

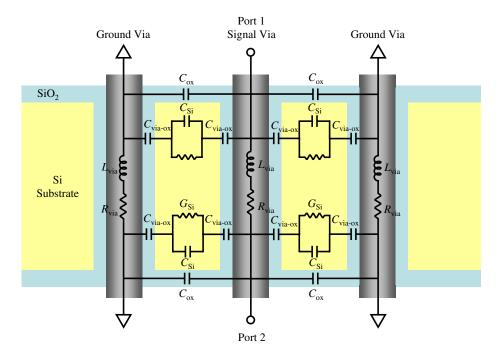

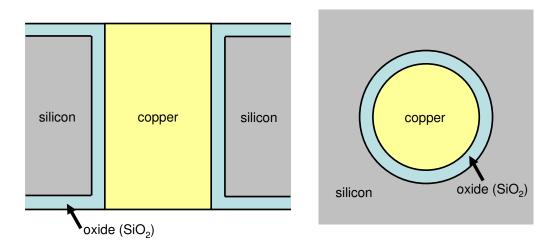

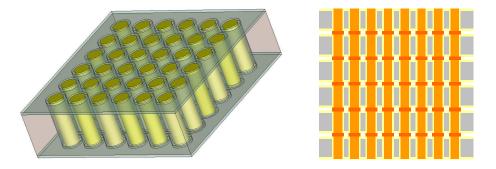

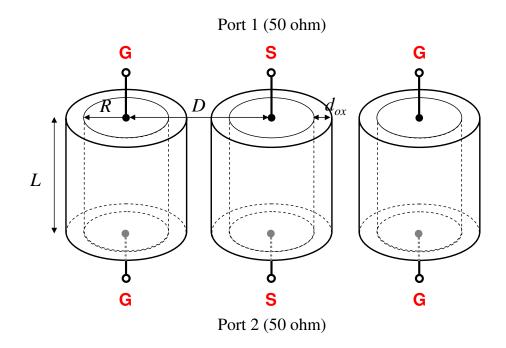

| CHAPT                                                        | FER 5 N<br>I<br>Structure                                                                                                                                                                                                                                                                                                                                                                | MODELING OF THROUGH SILICON VIA (TSV)<br>NTERCONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )<br>101                                                                                                                 |

| <b>CHAP</b><br>5.1                                           | FER 5 M<br>I<br>Structure I<br>Silicon Per                                                                                                                                                                                                                                                                                                                                               | MODELING OF THROUGH SILICON VIA (TSV)<br>NTERCONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )<br>101<br>102                                                                                                          |

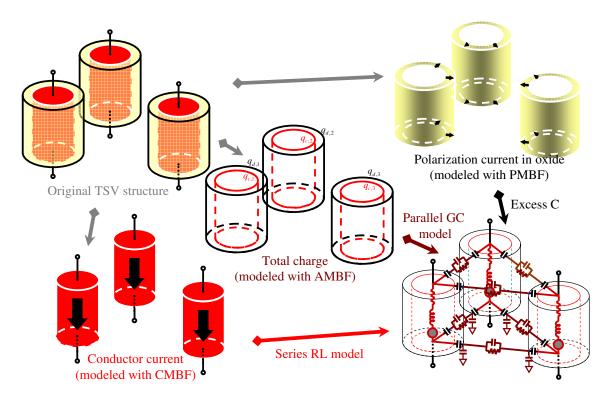

| 5.1<br>5.2                                                   | FER 5 M<br>I<br>Structure<br>Silicon Per<br>TSV Mode                                                                                                                                                                                                                                                                                                                                     | MODELING OF THROUGH SILICON VIA (TSV)<br>NTERCONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )<br>101<br>102<br>104                                                                                                   |

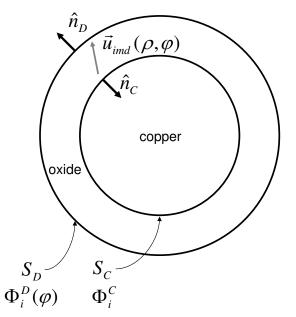

| 5.1<br>5.2                                                   | FER 5 M<br>I<br>Structure<br>Silicon Per<br>TSV Mode<br>5.3.1 EF                                                                                                                                                                                                                                                                                                                         | MODELING OF THROUGH SILICON VIA (TSV)<br>NTERCONNECTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )<br>101<br>102<br>104<br>105                                                                                            |

| 5.1<br>5.2                                                   | FER 5 M<br>I<br>Structure<br>Silicon Per<br>TSV Mode<br>5.3.1 EF<br>5.3.2 SP                                                                                                                                                                                                                                                                                                             | MODELING OF THROUGH SILICON VIA (TSV)         NTERCONNECTIONS         Description         Immittivity Model and Operation Modes         Immittivity Model And Operation Modes | )<br>101<br>102<br>104<br>105<br>106                                                                                     |

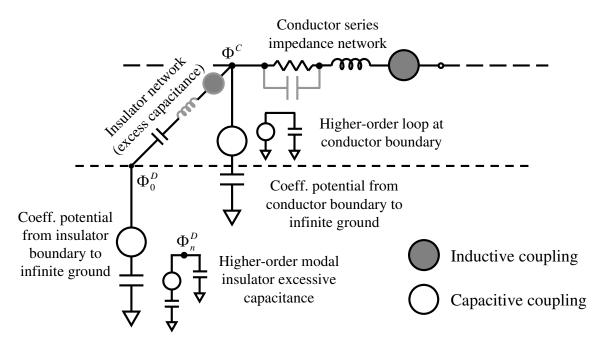

| 5.1<br>5.2                                                   | <b>FER 5 N</b><br>I<br>Structure<br>Silicon Per<br>TSV Mode<br>5.3.1 EF<br>5.3.2 SP<br>5.3.3 Eq                                                                                                                                                                                                                                                                                          | MODELING OF THROUGH SILICON VIA (TSV)         NTERCONNECTIONS         Description         Tmittivity Model and Operation Modes         eling with Cylindrical Modal Basis Functions         TE Formulation in Oxide Region and Cylindrical PMBF         IE Formulation on Conductor and Insulator Surfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | )<br>101<br>102<br>104<br>105<br>106<br>113                                                                              |

| 5.1<br>5.2                                                   | <b>FER 5 N</b><br>I<br>Structure<br>Silicon Per<br>TSV Mode<br>5.3.1 EF<br>5.3.2 SP<br>5.3.3 Eq                                                                                                                                                                                                                                                                                          | MODELING OF THROUGH SILICON VIA (TSV)         NTERCONNECTIONS         Description         rmittivity Model and Operation Modes         eling with Cylindrical Modal Basis Functions         TE Formulation in Oxide Region and Cylindrical PMBF         IE Formulation on Conductor and Insulator Surfaces         uivalent Circuit and Matrix Formulation         neralized Excess Modal Capacitances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )<br>101<br>102<br>104<br>105<br>106<br>113<br>113                                                                       |

| 5.1<br>5.2<br>5.3                                            | <b>FER 5 M</b><br>Structure<br>Silicon Per<br>TSV Mode<br>5.3.1 EF<br>5.3.2 SP<br>5.3.3 Eq<br>5.3.4 Ge<br>Validation                                                                                                                                                                                                                                                                     | MODELING OF THROUGH SILICON VIA (TSV)         NTERCONNECTIONS         Description         Immittivity Model and Operation Modes         rmittivity Model and Operation Modes         eling with Cylindrical Modal Basis Functions         IE Formulation in Oxide Region and Cylindrical PMBF         IE Formulation on Conductor and Insulator Surfaces         uivalent Circuit and Matrix Formulation         neralized Excess Modal Capacitances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | )<br>101<br>102<br>104<br>105<br>106<br>113<br>113<br>116                                                                |

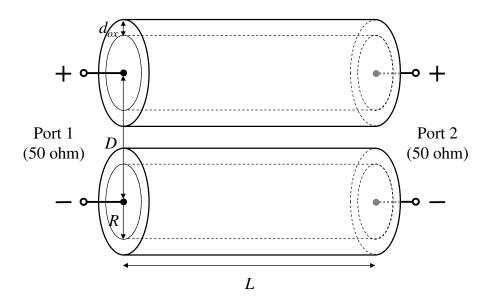

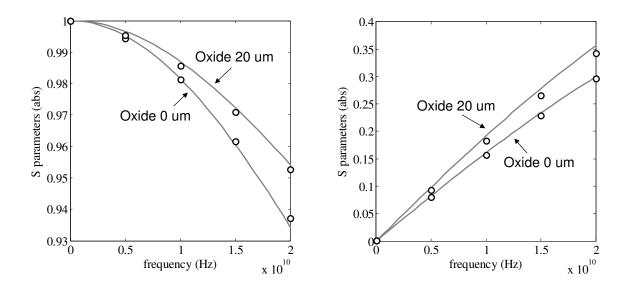

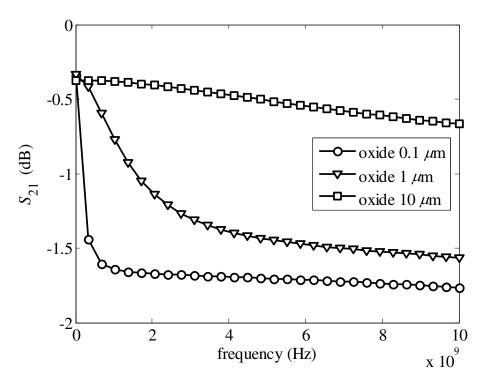

| 5.1<br>5.2<br>5.3                                            | <b>FER 5 M</b><br><b>I</b><br>Structure <b>E</b><br>Silicon Per<br>TSV Mode<br>5.3.1 EF<br>5.3.2 SP<br>5.3.3 Eq<br>5.3.3 Eq<br>5.3.4 Gez<br>Validation<br>5.4.1 Eff                                                                                                                                                                                                                      | MODELING OF THROUGH SILICON VIA (TSV)         NTERCONNECTIONS         Description         rmittivity Model and Operation Modes         reling with Cylindrical Modal Basis Functions         PIE Formulation in Oxide Region and Cylindrical PMBF         IE Formulation on Conductor and Insulator Surfaces         uivalent Circuit and Matrix Formulation         neralized Excess Modal Capacitances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | )<br>101<br>102<br>104<br>105<br>106<br>113<br>113<br>116<br>118                                                         |

| 5.1<br>5.2<br>5.3                                            | <b>FER 5 N</b><br>Structure Silicon Per<br>TSV Mode<br>5.3.1 EF<br>5.3.2 SP<br>5.3.3 Eq<br>5.3.4 Ge<br>Validation<br>5.4.1 Eff<br>5.4.2 Th                                                                                                                                                                                                                                               | MODELING OF THROUGH SILICON VIA (TSV)         NTERCONNECTIONS         Description         rmittivity Model and Operation Modes         eling with Cylindrical Modal Basis Functions         Pile Formulation in Oxide Region and Cylindrical PMBF         IE Formulation on Conductor and Insulator Surfaces         uivalent Circuit and Matrix Formulation         neralized Excess Modal Capacitances         Ect of Oxide Coating without Silicon Substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | )<br>101<br>102<br>104<br>105<br>106<br>113<br>113<br>116<br>118<br>118                                                  |

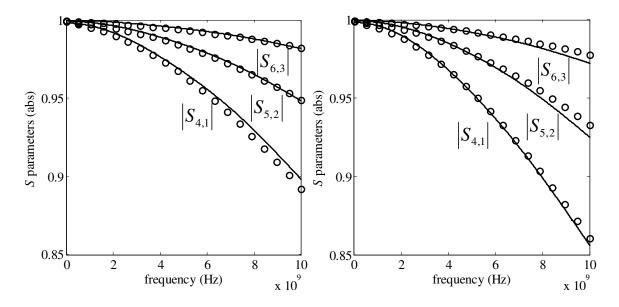

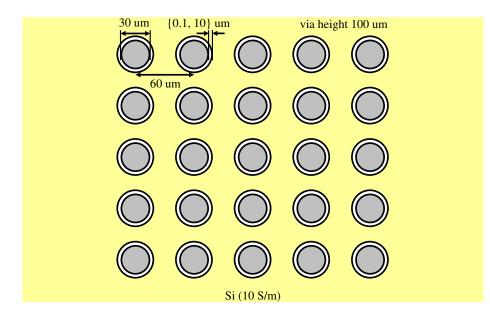

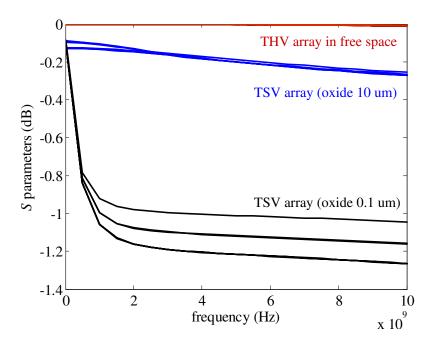

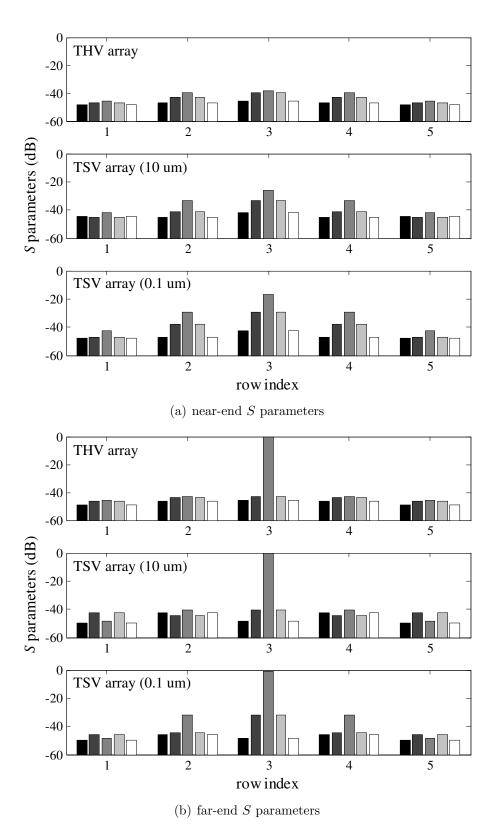

| 5.1<br>5.2<br>5.3                                            | FER 5         M           Structure 1           Silicon Per           TSV Mode           5.3.1         EF           5.3.2         SP           5.3.3         Eq           5.3.4         Ge           Validation         5.4.1           5.4.2         Th           5.4.3         Co                                                                                                      | MODELING OF THROUGH SILICON VIA (TSV)         NTERCONNECTIONS         Description         rmittivity Model and Operation Modes         eling with Cylindrical Modal Basis Functions         Pile Formulation in Oxide Region and Cylindrical PMBF         IE Formulation on Conductor and Insulator Surfaces         uivalent Circuit and Matrix Formulation         neralized Excess Modal Capacitances         ect of Oxide Coating without Silicon Substrate         ree TSV Interconnections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | )<br>101<br>102<br>104<br>105<br>106<br>113<br>113<br>116<br>118<br>118<br>119                                           |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                              | <b>FER 5 N</b><br>Structure Silicon Per<br>TSV Mode<br>5.3.1 EF<br>5.3.2 SP<br>5.3.3 Eq<br>5.3.4 Ge<br>Validation<br>5.4.1 Eff<br>5.4.2 Th<br>5.4.3 Co<br>Summary                                                                                                                                                                                                                        | MODELING OF THROUGH SILICON VIA (TSV)         NTERCONNECTIONS         Description         rmittivity Model and Operation Modes         eling with Cylindrical Modal Basis Functions         eling with Cylindrical Modal Basis Functions         TE Formulation in Oxide Region and Cylindrical PMBF         IE Formulation on Conductor and Insulator Surfaces         uivalent Circuit and Matrix Formulation         neralized Excess Modal Capacitances         Cect of Oxide Coating without Silicon Substrate         upling Characteristics of TSV Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | )<br>101<br>102<br>104<br>105<br>106<br>113<br>113<br>116<br>118<br>118<br>119<br>122<br>124                             |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br><b>CHAP</b>               | <b>FER 5M</b> IIStructure ISilicon PerTSV Mode5.3.1EF5.3.2SPI5.3.3Eq5.3.4GetValidation5.4.1Eff5.4.2Th5.4.3CorSummary <b>TER 6</b>                                                                                                                                                                                                                                                        | MODELING OF THROUGH SILICON VIA (TSV)         NTERCONNECTIONS         Description         rmittivity Model and Operation Modes         eling with Cylindrical Modal Basis Functions         Pierore Formulation in Oxide Region and Cylindrical PMBF         IE Formulation on Conductor and Insulator Surfaces         uivalent Circuit and Matrix Formulation         neralized Excess Modal Capacitances         Conclusions         CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )<br>101<br>102<br>104<br>105<br>106<br>113<br>113<br>116<br>118<br>118<br>119<br>122<br>124<br>126                      |