# Multiscale EM and Circuit Simulation Using the Laguerre-FDTD Scheme for Package-Aware Integrated-Circuit Design

A Thesis

Presented to

The Academic Faculty

by

Krishna Srinivasan

In Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy in the

School of Electrical and Computer Engineering

Georgia Institute of Technology August 2008 Copyright © Krishna Srinivasan 2008

# Multiscale EM and Circuit Simulation Using the Laguerre-FDTD Scheme for Package-Aware Integrated-Circuit Design

#### Approved by:

Prof. Madhavan Swaminathan, Advisor School of ECE Georgia Institute of Technology

Prof. Andrew Peterson School of ECE Georgia Institute of Technology

Prof. Sung Kyu Lim School of ECE Georgia Institute of Technology Prof. George Riley School of ECE Georgia Institute of Technology

Prof. Yogendra Joshi School of Mechanical Engineering Georgia Institute of Technology

Date Approved: 21 April 2008

To Suresh, Shanthi, and Prof. Swaminathan

## Acknowledgements

#### My sincere thanks to

- Prof. Madhavan Swaminathan for providing me with this wonderful opportunity and fulfilling my dream of doing graduate studies. It was great working in the EPSILON lab. His technical advice and feedback made the goal achievable. I greatly appreciate his financial support. With deepest respect and gratitude I dedicate this thesis to him.

- Dr. Ege Engin, post-doctoral researcher, for the valuable technical discussions, feedback, and patiently answering my infinite number of questions.

- Research engineers Hideki san for his guidance when I first started with research work and Takayuki san for mentoring my study.

- The committee members for the time that they have taken to read through this thesis and offer their suggestions to improve this work.

- The students of the EPSILON group for the valuable technical discussions and advice.

- My family and relatives, especially Suresh and Shanthi, without whom this work would not have been possible. I also dedicate this thesis to Suresh and Shanthi.

# Contents

| A              | ckno  | wledgements                                                                | III |

|----------------|-------|----------------------------------------------------------------------------|-----|

| Li             | st of | Tables                                                                     | III |

| Li             | st of | Figures                                                                    | ΙX  |

| $\mathbf{S}$ ι | ımm   | ary                                                                        | 1   |

| 1              | Inti  | roduction                                                                  | 2   |

|                | 1.1   | Development of CAD Tools                                                   | 4   |

|                | 1.2   | Common Signal and Power-Integrity Problems Present in a Chip and a Package | 5   |

|                | 1.3   | Proposed Research                                                          | 8   |

|                | 1.4   | Dissertation Outline                                                       | 11  |

| 2              | Tra   | nsient Simulation Using Laguerre Polynomials                               | 13  |

|                | 2.1   | Introduction                                                               | 13  |

|                | 2.2   | The SLeEC Alogrithm                                                        | 15  |

|                |       | 2.2.1 Transformation from time domain to Laguerre domain                   | 16  |

|                |       | 2.2.2 Companion Models                                                     | 18  |

|                |       | 2.2.3 DC Analysis                                                          | 18  |

|                |       | 2.2.4 Transformation from Laguerre domain to time domain                   | 20  |

|                | 2.3   | Advantages of Laguerre Polynomials                                         | 20  |

|                | 2.4   | Summary                                                                    | 21  |

| 3              | Sim   | ulation For Any Length of Time                                             | 22  |

|                | 3.1   | Introduction                                                               | 22  |

|                | 3.2   | An Example to Demonstrate the Limitation                                   | 22  |

|                | 3.3   | A Solution to Overcome the Limitation                                      | 23  |

|                | 3.4   | Computing the Final Values at the End of an Interval                       | 25  |

|                | 3.5   | Examples of Simulation Using Initial Conditions                            | 25  |

|                | 3 6   | Summary                                                                    | 26  |

| 4 | Cor | mpanion Models for Circuit Simulation                        | 29         |

|---|-----|--------------------------------------------------------------|------------|

|   | 4.1 | Introduction                                                 | 29         |

|   | 4.2 | The Companion Model of an Inductor                           | 29         |

|   | 4.3 | The Companion Model of a Capacitor                           | 32         |

|   | 4.4 | Transient Simulation of Inductor and Capacitor (LC) Circuits | 34         |

|   | 4.5 | The Companion model for Mutual Inductance                    | 36         |

|   | 4.6 | Summary                                                      | 40         |

| 5 | Cor | mpanion Models of the FDTD grid for EM Simulation            | 41         |

|   | 5.1 | Introduction                                                 | 41         |

|   | 5.2 | 1D FDTD                                                      | 42         |

|   | 5.3 | 2D FDTD                                                      | 45         |

|   | 5.4 | 3D FDTD                                                      | 48         |

|   | 5.5 | Boundary Conditions                                          | 50         |

|   |     | 5.5.1 Perfect Electric Conductor (PEC) Boundary              | 52         |

|   |     | 5.5.2 Perfect Magnetic Conductor (PMC) Boundary              | 52         |

|   |     | 5.5.3 Absorbing Boundary Condition (ABC)                     | 53         |

|   | 5.6 | Summary                                                      | 53         |

| 6 | Cho | posing the Correct Number of Laguerre Basis Coefficients     | <b>5</b> 4 |

|   | 6.1 | Introduction                                                 | 54         |

|   | 6.2 | Methodology                                                  | 55         |

|   |     | 6.2.1 Energy analysis to find $q_{knee}$ (Step 1)            | 58         |

|   |     | 6.2.2 Finding the right value for $q$ (Step 2)               | 59         |

|   | 6.3 | Improved Methods to Calculate Energy                         | 59         |

|   | 6.4 | Summary                                                      | 63         |

| 7 | 3D  | EM Simulation Results                                        | 64         |

|   | 7.1 | Introduction                                                 | 64         |

|   | 7.2 | Node-Numbering Schemes                                       | 64         |

|   | 73  | EM Tost cases                                                | 65         |

|   | 7.4  | A Split Power-Ground Plane                                              |

|---|------|-------------------------------------------------------------------------|

|   | 7.5  | An EBG Structure                                                        |

|   | 7.6  | On-chip Coupled Lines                                                   |

|   | 7.7  | A Chip-Package Structure                                                |

|   | 7.8  | Summary                                                                 |

| 8 | Tim  | ne-domain to Frequency-domain Transformation 82                         |

|   | 8.1  | Introduction                                                            |

|   | 8.2  | A Test Case to Illustrate the Transformation                            |

|   | 8.3  | Summary                                                                 |

| 9 | Effi | cient Use of Full-Wave Solvers For Chip-Package Cosimulation 89         |

|   | 9.1  | Introduction                                                            |

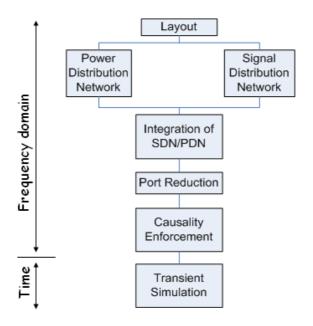

|   | 9.2  | SDN-PDN Cosimulation                                                    |

|   | 9.3  | Frequency-Domain Parameters of PDN and SDN                              |

|   | 9.4  | Integration of PDN and SDN                                              |

|   |      | 9.4.1 Microstrip Configuration                                          |

|   |      | 9.4.2 Coplanar-Waveguide Configuration                                  |

|   |      | 9.4.3 A test structure to verify the coplanar-waveguide model 10        |

|   | 9.5  | Port Reduction                                                          |

|   | 9.6  | Causality Enforcement Through Delay Extraction                          |

|   | 9.7  | Transient Simulation                                                    |

|   |      | 9.7.1 Transient Simulation Using Signal-Flow Graphs                     |

|   |      | 9.7.2 Transient Simulation Using S-Parameters in MNA Framework 10       |

|   | 9.8  | Results                                                                 |

|   |      | 9.8.1 Transmission Line Simulation                                      |

|   |      | 9.8.2 Step Response of an Interconnect With Causality Enforcement 11    |

|   |      | 9.8.3 Sixty-Four Bit Bus Referenced to a Nonideal Power-Ground Plane 11 |

|   | 9.9  | Speed And Memory Optimization                                           |

|   |      | 9.9.1 Methodology                                                       |

|   |      | 9.9.2 Enhancement of Power Integrity Using Embedded Capacitors 11       |

|           | 9.10 Summary                                                       | 121        |

|-----------|--------------------------------------------------------------------|------------|

| 10        | Future Work: Alternate Schemes for DC Analysis of the FDTD Lattice | <b>123</b> |

|           | 10.1 Introduction                                                  | 123        |

|           | 10.2 1D Grid                                                       | 124        |

|           | 10.3 2D Grid                                                       | 125        |

|           | 10.4 3D Grid                                                       | 128        |

|           | 10.5 Summary                                                       | 128        |

| 11        | Conclusions                                                        | 130        |

| <b>12</b> | Appendix A: Derivation of the Courant Condition                    | 131        |

| 13        | Publications                                                       | 133        |

|           | 13.1 Journals and Conference Papers                                | 133        |

|           | 13.2 Invention Disclosures                                         | 135        |

| Re        | eferences                                                          | 136        |

# List of Tables

| 1 | The probe locations of the electric and magnetic fields for the three test cases. | 68 |

|---|-----------------------------------------------------------------------------------|----|

| 2 | The memory and simulation time comparison for Test case 1                         | 69 |

| 3 | The memory and simulation time comparison for Test case 2                         | 71 |

| 4 | The memory and simulation time comparison for Test case 3                         | 7: |

# List of Figures

| 1  | A generic Intel PC system                                                         | 3  |

|----|-----------------------------------------------------------------------------------|----|

| 2  | A multichip module                                                                | 3  |

| 3  | The Intel processor family and CAD tools                                          | 4  |

| 4  | Traditional sequential design flow [3]                                            | 6  |

| 5  | Package-aware design flow. [3]                                                    | 6  |

| 6  | Common signal and power-integrity problems present in a package                   | 7  |

| 7  | Simultaneous switching noise (SSN)                                                | 8  |

| 8  | A microstrip and a conductor-backed coplanar-waveguide configuration              | 11 |

| 9  | Multiscale features in a chip-package structure                                   | 14 |

| 10 | The flowchart of the SLeEC methodology                                            | 15 |

| 11 | Weighted Laguerre polynomials for orders $p=0$ to $p=4$                           | 17 |

| 12 | The original (dots) and reconstructed (solid) triangular waveform using La-       |    |

|    | guerre basis functions                                                            | 19 |

| 13 | The coefficients of basis functions for the triangular waveform in Figure $12.$ . | 19 |

| 14 | The companion model for a unit cell in a 1D FDTD grid                             | 20 |

| 15 | A 2D box with PEC boundary                                                        | 23 |

| 16 | The transient simulation response from $15ns$ to $20ns$ . Solid: the Laguerre-    |    |

|    | FDTD scheme and Dots: FDTD                                                        | 24 |

| 17 | The total simulation time is divided into different intervals                     | 24 |

| 18 | The circuit for transient simulation with initial conditions                      | 25 |

| 19 | The voltage across the capacitor $V(t)$ with initial conditions (200 basis coef-  |    |

|    | ficients). Dots: WinSpice and Solid: SLeEC                                        | 27 |

| 20 | The voltage across the capacitor $V(t)$ with initial conditions (400 basis coef-  |    |

|    | ficients). Dots: WinSpice and Solid: SLeEC                                        | 27 |

| 21 | The simulation results from 0ns to 5ns. Solid: SLeEC and Dots: FDTD               | 28 |

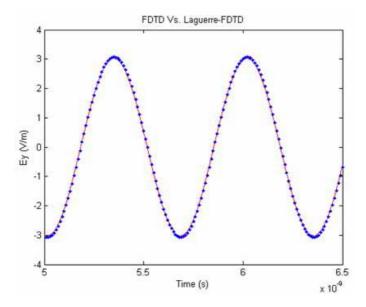

| 22 | The simulation results from 5ns to 6.5ns using new interval length and time-      |    |

|    | scale factor. Solid: SLeEC and Dots: FDTD                                         | 28 |

| 23 | The Thevenin and Norton forms of the companion model for an inductor or              |    |

|----|--------------------------------------------------------------------------------------|----|

|    | a capacitor                                                                          | 29 |

| 24 | A series LC circuit                                                                  | 34 |

| 25 | The companion model for the circuit in Figure 24                                     | 34 |

| 26 | Voltage $V^C$ in the circuit shown in Figure 24 using 200 basis coefficients.        |    |

|    | Solid: SLeEC and Dots: WinSpice                                                      | 35 |

| 27 | Voltage $V^C$ in the circuit shown in Figure 24 using 400 basis coefficients.        |    |

|    | Solid: SLeEC and Dots: WinSpice                                                      | 35 |

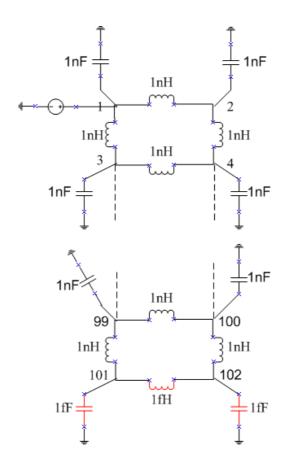

| 28 | An LC network                                                                        | 37 |

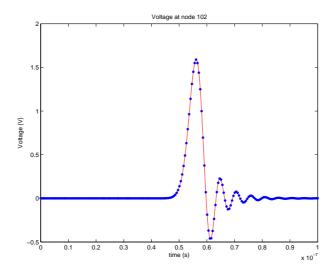

| 29 | The transient voltage waveform at Node 102 in Figure 28. Solid: SLeEC and            |    |

|    | Dots: WinSpice                                                                       | 37 |

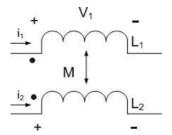

| 30 | Two inductors with mutual coupling                                                   | 38 |

| 31 | The companion model for mutual inductance in the Thevenin form                       | 38 |

| 32 | The companion model for mutual inductance in the Norton form                         | 39 |

| 33 | The companion model for a unit cell in an FDTD grid                                  | 43 |

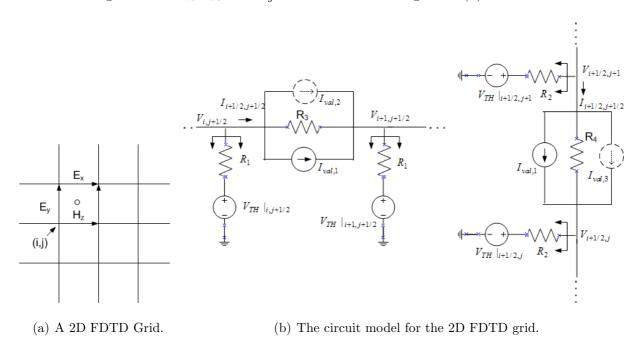

| 34 | The companion model for the 2D FDTD grid                                             | 45 |

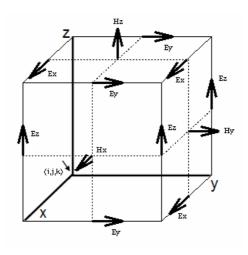

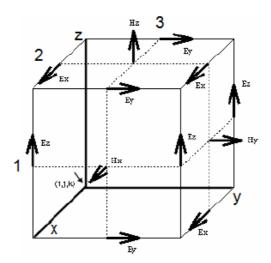

| 35 | The standard Yee cell                                                                | 48 |

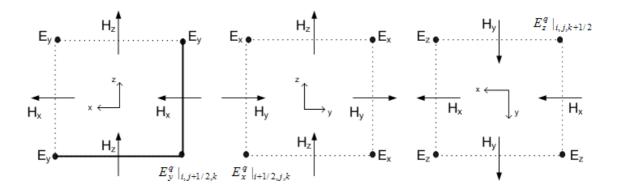

| 36 | The ×Sections of the Yee cell, which are marked by the dotted lines in Figure        |    |

|    | 35, parallel to the $xz$ , $yz$ and $xy$ planes, respectively. The dots indicate the |    |

|    | direction of the fields pointing out of the page                                     | 51 |

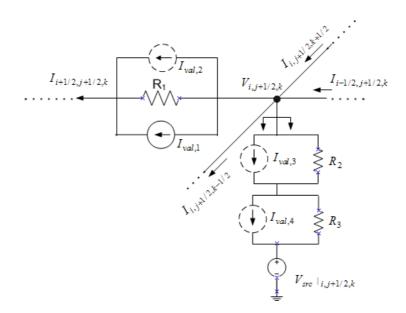

| 37 | The companion model of the 3D FDTD grid in the Laguerre domain                       | 51 |

| 38 | The PEC boundary condition                                                           | 52 |

| 39 | The PMC boundary condition                                                           | 53 |

| 40 | The absorbing boundary condition                                                     | 53 |

| 41 | A 2D power-ground plane structure                                                    | 54 |

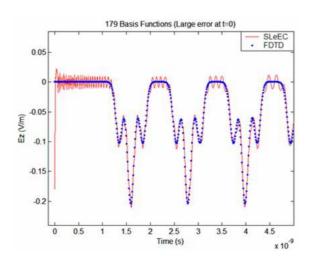

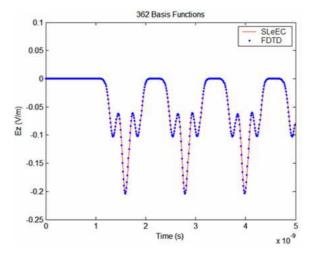

| 42 | The time-domain waveform generated using 179 basis functions                         | 56 |

| 43 | The time-domain waveform generated using 362 basis functions                         | 56 |

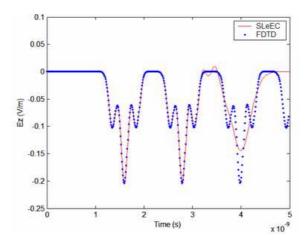

| 44 | If a small value for $q$ is chosen, then the time-domain waveform does not have      |    |

|    | sufficient energy content                                                            | 57 |

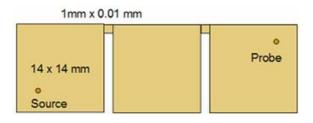

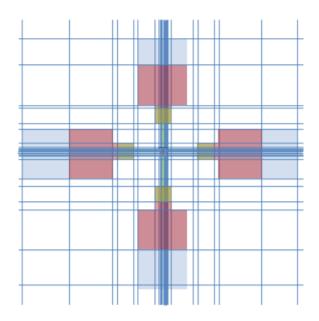

| 45 | A planar structure with multiscale dimensions                                        | 57 |

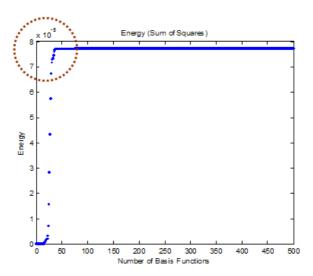

| 46 | Energy as a function of the number of basis coefficients using Scheme 1                | 58 |

|----|----------------------------------------------------------------------------------------|----|

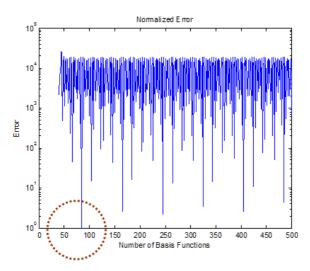

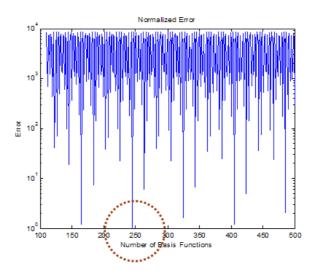

| 47 | The normalized error at time $t=0$ as a function of the number of basis                |    |

|    | coefficients using Scheme 1                                                            | 60 |

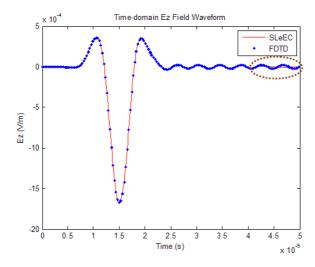

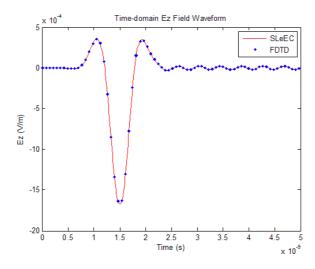

| 48 | The time-domain $E_z$ field obtained using Scheme 1                                    | 60 |

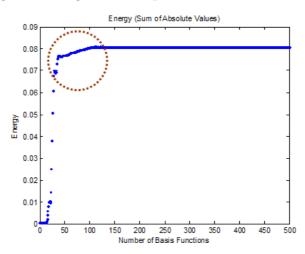

| 49 | The energy profile as a function of the number of basis coefficients using             |    |

|    | Scheme 2                                                                               | 61 |

| 50 | The normalized error as a function of the number of basis coefficients using           |    |

|    | Scheme 2                                                                               | 62 |

| 51 | The time-domain $E_z$ field obtained using Scheme 2                                    | 62 |

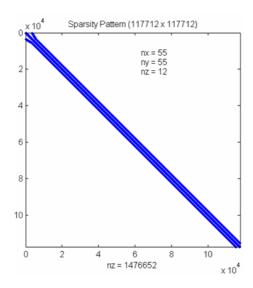

| 52 | Planes 1, 2, and 3 in the inefficient node numbering scheme                            | 65 |

| 53 | The sparsity pattern of the A matrix from an inefficient node-numbering                |    |

|    | scheme.                                                                                | 65 |

| 54 | The sparsity pattern of the A matrix that is suitable for LU decomposition             | 66 |

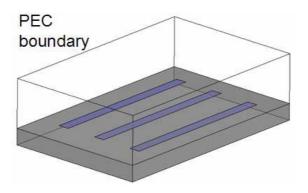

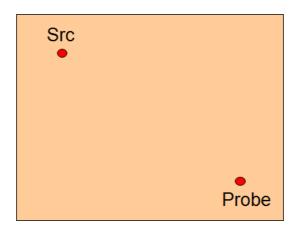

| 55 | The bird's eye view of an EM test case that is enclosed within a PEC box               | 67 |

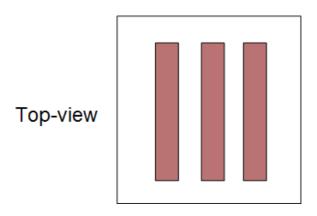

| 56 | The top view of an EM test case                                                        | 67 |

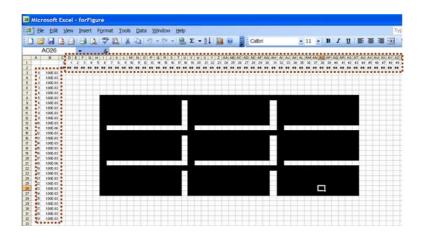

| 57 | Microsoft Excel® is used as a GUI for the layout of the test cases                     | 67 |

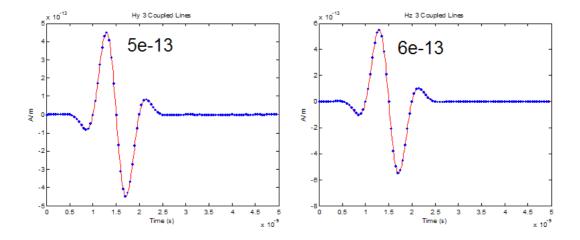

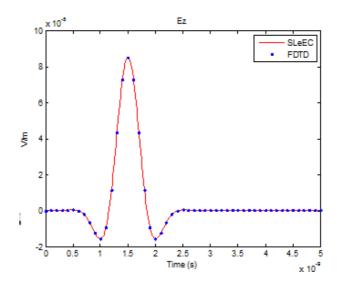

| 58 | A split power-ground plane                                                             | 68 |

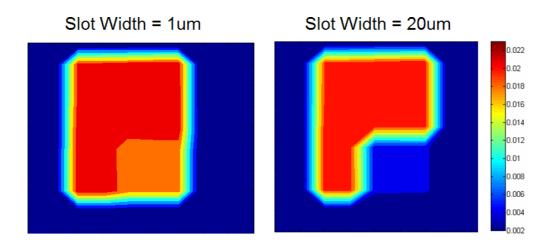

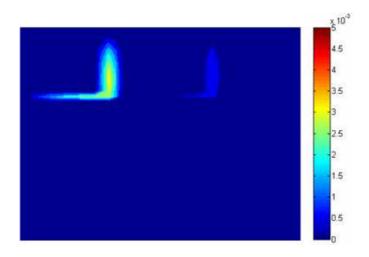

| 59 | The contour maps of the split-plane test case                                          | 69 |

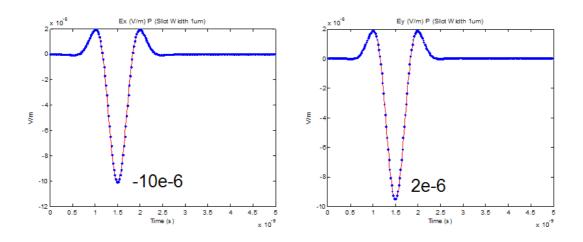

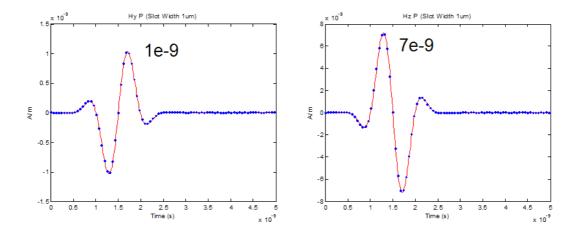

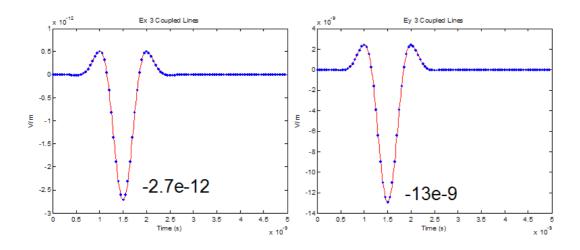

| 60 | $E_x$ (126 basis coefficients) and $E_y$ (208 basis coefficients) fields in the split- |    |

|    | plane test case. Solid: SLeEC and Dots: FDTD                                           | 69 |

| 61 | $E_z$ (490 basis coefficients) and $H_x$ (226 basis coefficients) fields in the split- |    |

|    | plane test case. Solid: SLeEC and Dots: FDTD                                           | 70 |

| 62 | $H_y$ (259 basis coefficients) and $H_z$ (398 basis coefficients) fields in the split- |    |

|    | plane test case. Solid: SLeEC and Dots: FDTD                                           | 70 |

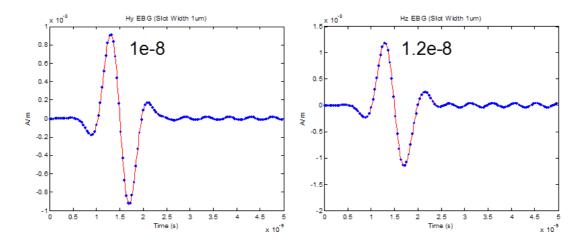

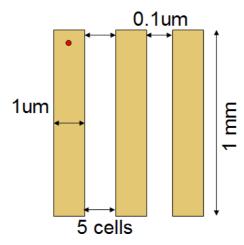

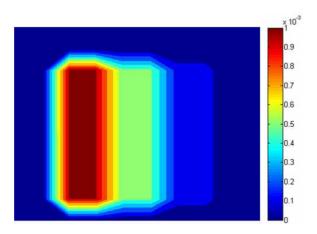

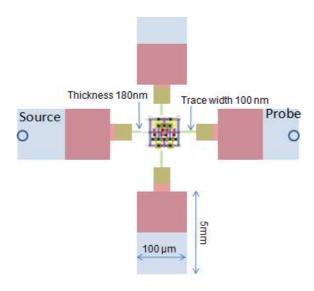

| 63 | A 2D EBG test case                                                                     | 71 |

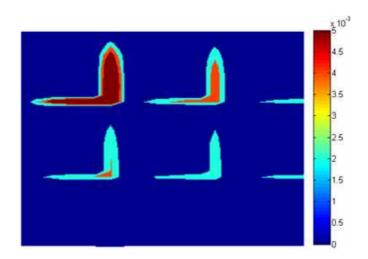

| 64 | The 2D EBG contour map of the $ (E_x, E_y) $ field after 950ps                         | 72 |

| 65 | The 2D EBG contour map of the $ (E_x, E_y) $ field after 1200ps                        | 72 |

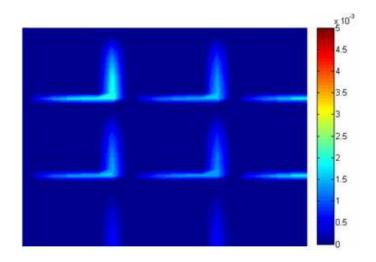

| 66 | The 2D EBG contour map of the $ (E_x, E_y) $ field after 1300ps                        | 73 |

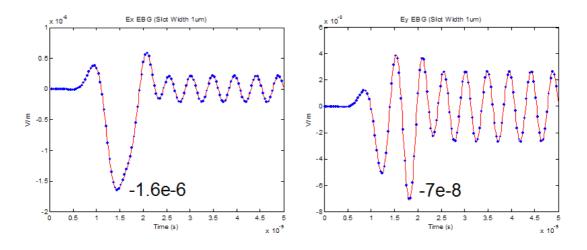

| 67 | $E_x$ (413 basis coefficients) and $E_y$ (413 basis coefficients) fields in the EBG    |    |

|    | test case. Solid: SLeEC and Dots: FDTD                                                 | 73 |

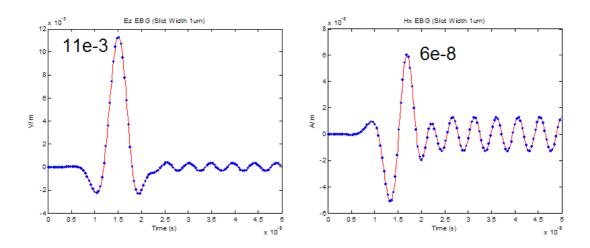

| 68 | $E_z$ (413 basis coefficients) and $H_x$ (141 basis coefficients) fields in the EBG          |    |

|----|----------------------------------------------------------------------------------------------|----|

|    | test case. Solid: SLeEC and Dots: FDTD                                                       | 74 |

| 69 | $H_y$ (171 basis coefficients) and $H_z$ (141 basis coefficients) fields in the EBG          |    |

|    | test case. Solid: SLeEC and Dots: FDTD                                                       | 74 |

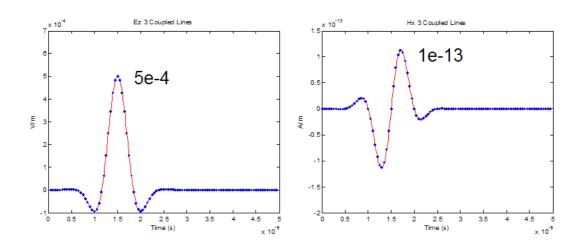

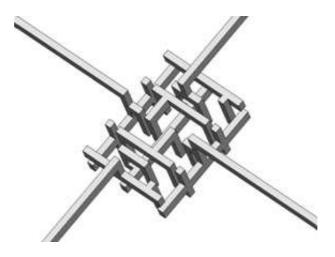

| 70 | Three on-chip coupled transmission lines                                                     | 75 |

| 71 | The contour map of the $E_z$ field                                                           | 76 |

| 72 | $E_x$ (49 basis coefficients) and $E_y$ (446 basis coefficients) fields of the transmission  | -  |

|    | lines test case. Solid: SLeEC and Dots: FDTD                                                 | 76 |

| 73 | $E_z$ (409 basis coefficients) and $H_x$ (188 basis coefficients) fields of the transmission | n- |

|    | lines test case. Solid: SLeEC and Dots: FDTD                                                 | 77 |

| 74 | $H_y$ (437 basis coefficients) and $H_z$ (411 basis coefficients) fields of the transmission | n- |

|    | lines test case. Solid: SLeEC and Dots: FDTD                                                 | 77 |

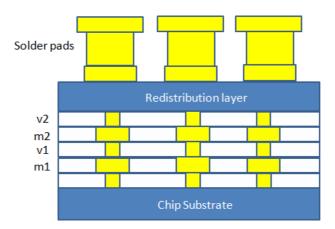

| 75 | A chip-package structure with multiscale features                                            | 78 |

| 76 | Non-uniform mesh dimensions simulated using SLeEC                                            | 79 |

| 77 | The cross section of the different metal layers                                              | 79 |

| 78 | The 3D Layout of the chip-package structure                                                  | 80 |

| 79 | SLeEC and FDTD results of the chip-package structure                                         | 80 |

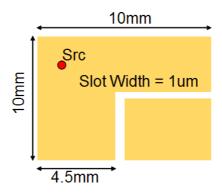

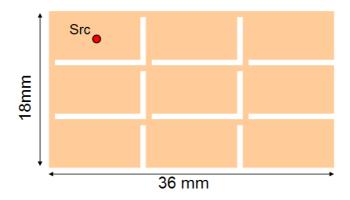

| 80 | A power-ground plane test case                                                               | 82 |

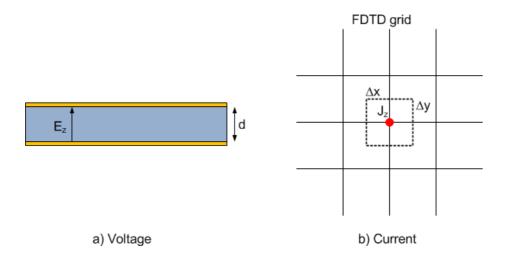

| 81 | Voltage and current definitions                                                              | 84 |

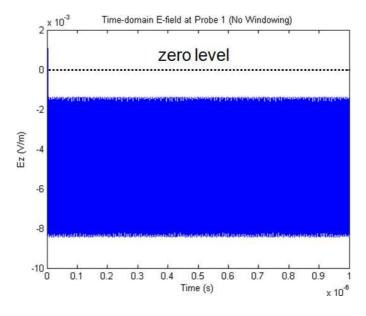

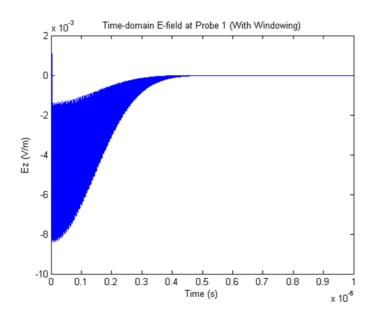

| 82 | The time domain $E_z$ waveform between $0 - 1\mu s$ at the location marked $Src$             |    |

|    | in Figure 80                                                                                 | 84 |

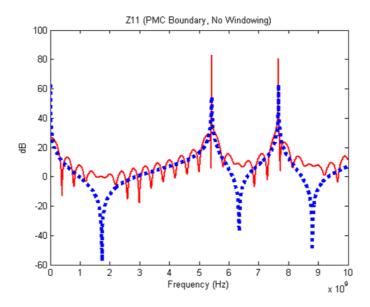

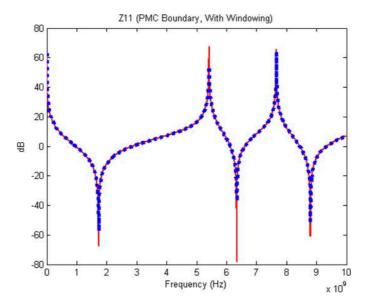

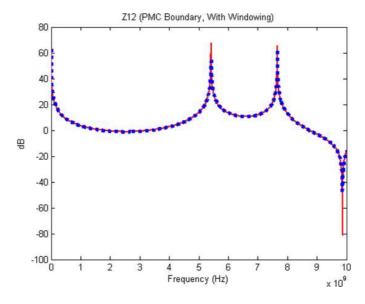

| 83 | $Z_{11}$ , 0-10GHz, without windowing and the PMC boundary condition has been                |    |

|    | used to terminate the mesh. Dots: MFDM [18] and Solid: FDTD                                  | 85 |

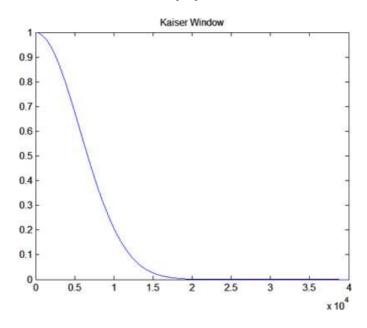

| 84 | The second half of the time-domain Kaiser windowing function                                 | 85 |

| 85 | The time domain $E_z$ waveform in Figure 82 with windowing                                   | 86 |

| 86 | $Z_{11}$ , 0-10GHz, with windowing and the PMC boundary condition has been                   |    |

|    | used to terminate the mesh. Dots: MFDM [18] and Solid: FDTD $\ \ldots \ \ldots$              | 86 |

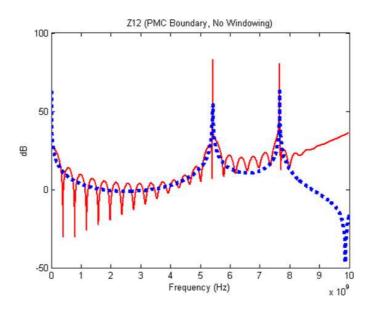

| 87 | $Z_{12}$ , 0-10GHz, without windowing and the PMC boundary condition has been                |    |

|    | used to terminate the mesh. Dots: MFDM [18] and Solid: FDTD                                  | 87 |

| 88  | $Z_{12}$ , 0-10GHz, with windowing and the PMC boundary condition has been    |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | used to terminate the mesh. Dots: MFDM [18] and Solid: FDTD                   | 87  |

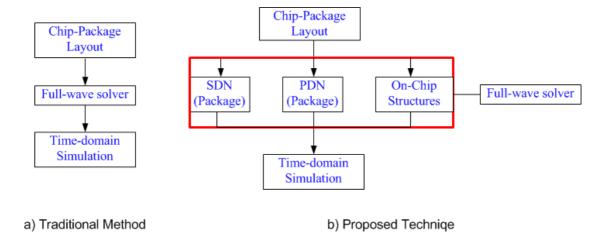

| 89  | The traditional and proposed methodologies for chip-package cosimulation      | 90  |

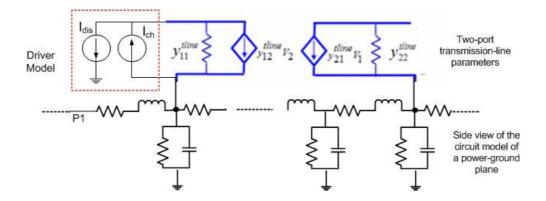

| 90  | The SDN-PDN cosimulation methodology                                          | 91  |

| 91  | A power-ground plane                                                          | 92  |

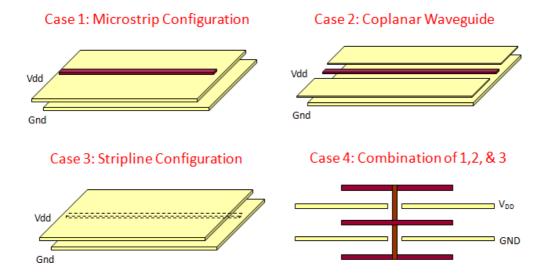

| 92  | The common types of interconnect configurations in a package                  | 93  |

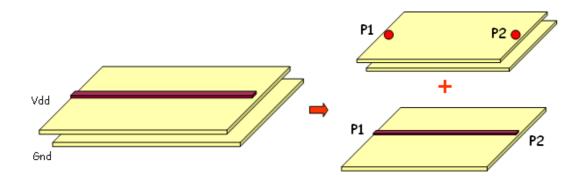

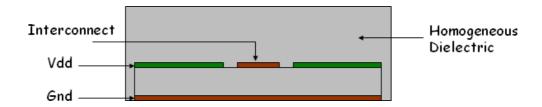

| 93  | A microstrip line over a power-ground plane                                   | 93  |

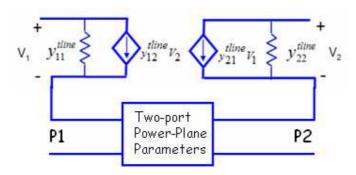

| 94  | The circuit model for a microstrip line referenced to a power-ground plane    | 95  |

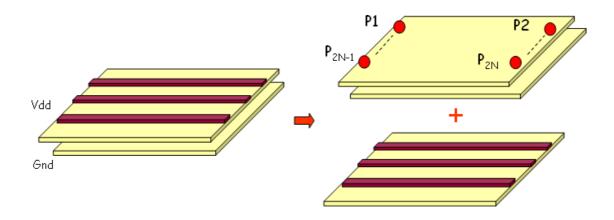

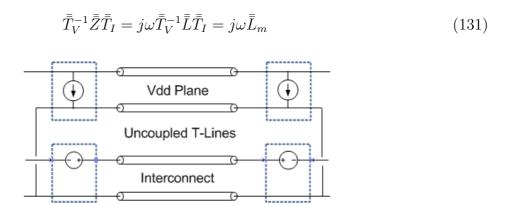

| 95  | N coupled lines referenced to a power-ground plane                            | 95  |

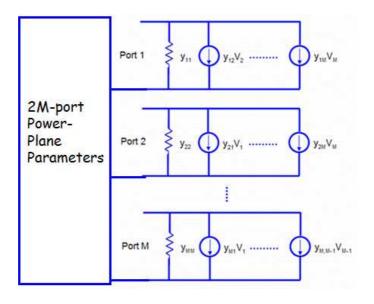

| 96  | The Y-parameter model for an M-port network referenced to a power-ground      |     |

|     | plane                                                                         | 96  |

| 97  | The cross section of a coplanar-waveguide structure                           | 97  |

| 98  | The coupling between the transmission lines is captured using controlled      |     |

|     | sources                                                                       | 97  |

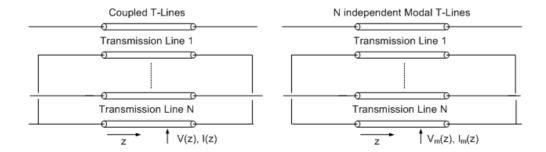

| 99  | N coupled transmission lines and modal transmission lines                     | 98  |

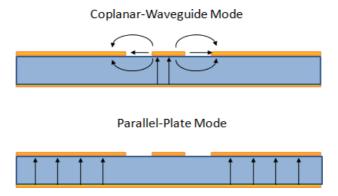

| 100 | The E-field patterns for the coplanar-waveguide mode and the parallel-plate   |     |

|     | mode                                                                          | 99  |

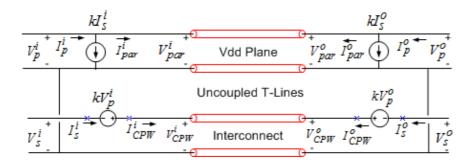

| 101 | The circuit model for a coplanar-waveguide structure                          | 100 |

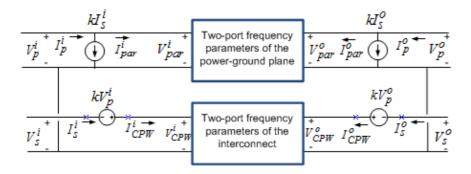

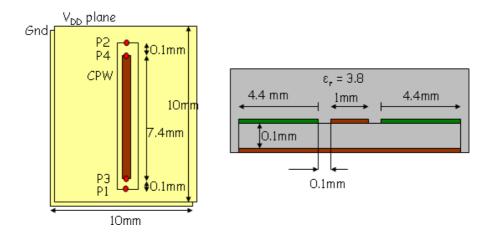

| 102 | The modal transmission lines replaced with two-port frequency parameters      | 101 |

| 103 | A test structure to verify the CPW model                                      | 102 |

| 104 | $S_{13}$ magnitude of the CPW test structure. Dots: Sonnet and Solid: CPW     |     |

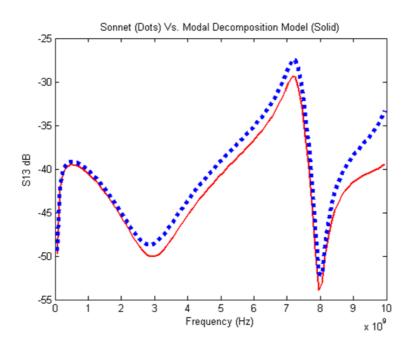

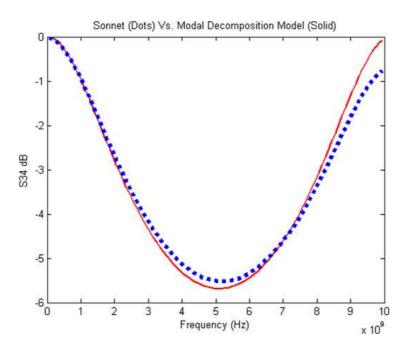

|     | Model                                                                         | 103 |

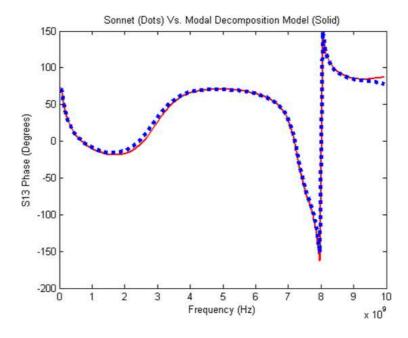

| 105 | $S_{13}$ phase of the CPW test structure. Dots: Sonnet and Solid: CPW Model . | 103 |

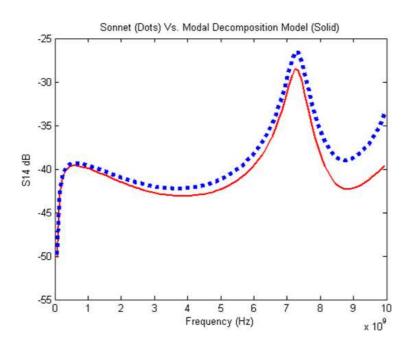

| 106 | $S_{14}$ magnitude of the CPW test structure. Dots: Sonnet and Solid: CPW     |     |

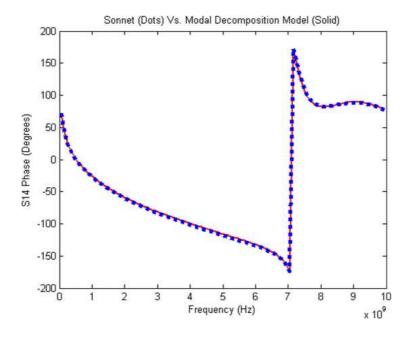

|     | Model                                                                         | 104 |

| 107 | $S_{14}$ phase of the CPW test structure. Dots: Sonnet and Solid: CPW Model . | 104 |

| 108 | $S_{34}$ magnitude of the CPW test structure. Dots: Sonnet and Solid: CPW     |     |

|     | Model                                                                         | 105 |

| 109 | $S_{34}$ phase of the CPW test structure. Dots: Sonnet and Solid: CPW Model . | 105 |

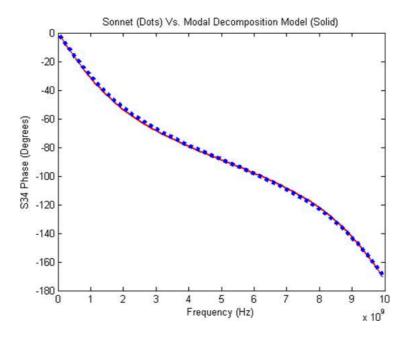

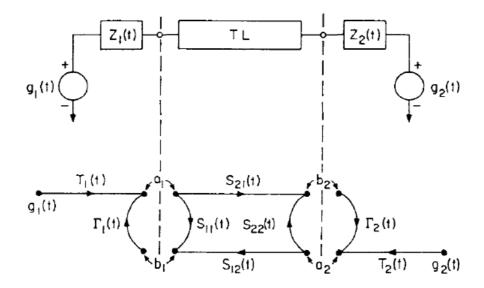

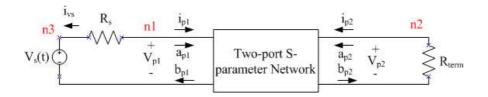

| 110 | A two port signal-flow graph [25].                                            | 108 |

| 111 | A two port S-parameter network with sources and terminations                | 109 |

|-----|-----------------------------------------------------------------------------|-----|

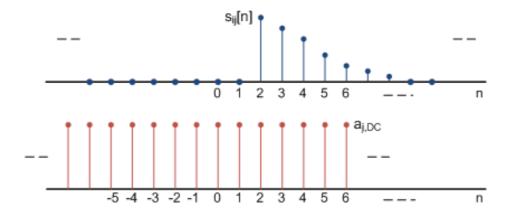

| 112 | The convolution of the impulse response $s_{ij}$ and constant $a_{j,DC}$    | 110 |

| 113 | The values of $a_j[n]$ for $n < 0$                                          | 111 |

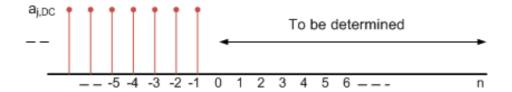

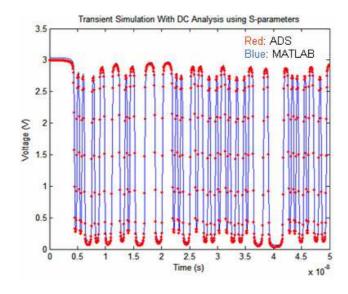

| 114 | Transient simulation of a transmission line with DC analysis using MNA      |     |

|     | formulation                                                                 | 112 |

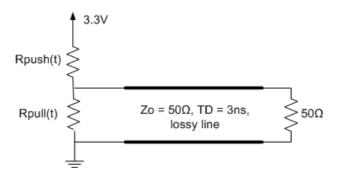

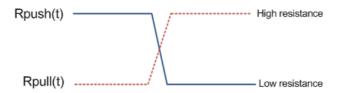

| 115 | A typical time-varying resistor waveform                                    | 113 |

| 116 | Rpush(t) and $Rpull(t)$ have opposite polarities.<br>                       | 113 |

| 117 | The voltage waveform at the far end of the interconnect. Solid: S-Parameter |     |

|     | simulation with DC analysis and Dots: ADS                                   | 113 |

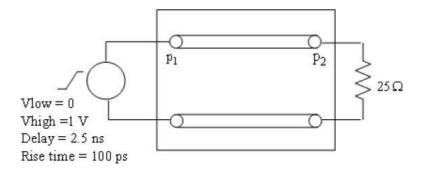

| 118 | The simulation set up for the step response of an interconnect              | 114 |

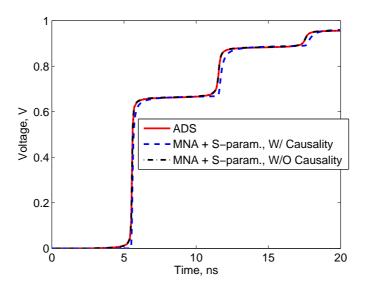

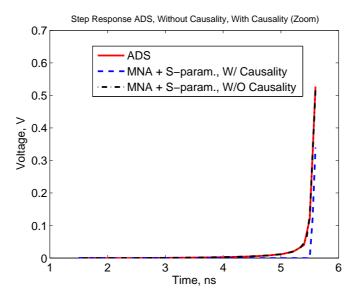

| 119 | The step response of a long interconnect from $0-20ns$                      | 115 |

| 120 | The zoom of Figure 119 from $0-6ns$                                         | 115 |

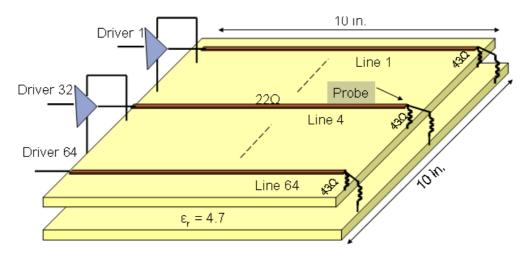

| 121 | The sixty-four bit bus simulation set up                                    | 116 |

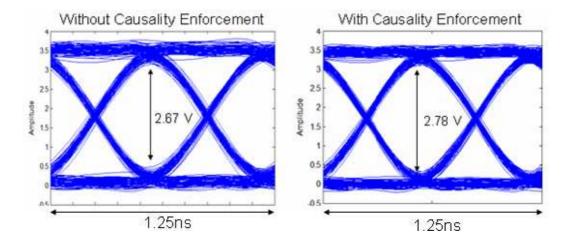

| 122 | The eye-diagram simulation results without and with causality enforcement.  | 116 |

| 123 | A transmission line referenced to a power-ground plane                      | 118 |

| 124 | The charging and discharging currents that model the source have opposite   |     |

|     | polarities                                                                  | 118 |

| 125 | A typical package connected to a PCB                                        | 120 |

| 126 | The simulation set up for SSN simulation                                    | 121 |

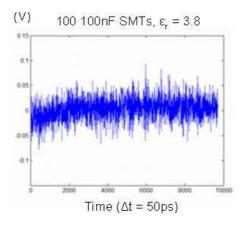

| 127 | Twenty-five 100nF SMTs and power-ground plane substrate $\epsilon_r=3.8.$   | 122 |

| 128 | Hundred 100nF SMTs and power-ground plane substrate $\epsilon_r=3.8.$       | 122 |

| 129 | Twenty-five 1nF embedded discrete capacitors and power-ground plane sub-    |     |

|     | strate $\epsilon_r = 11$                                                    | 122 |

| 130 | The flowchart of the SLeEC methodology                                      | 123 |

| 131 | The Norton companion model for a 1D FDTD grid terminated with PEC           |     |

|     | boundary                                                                    | 124 |

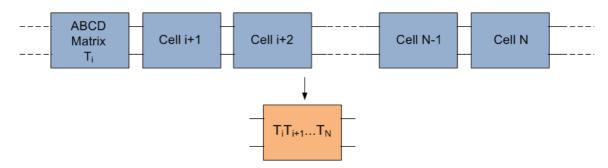

| 132 | A cascade of ABCD matrices reduced to a single block by multiplying the     |     |

|     | parameters of individual blocks                                             | 124 |

| 133 | The reduced FDTD grid network                                               | 125 |

| 134 | All the field coefficients in the entire 1D grid can be calculated using $E_1$ alone |     |

|-----|--------------------------------------------------------------------------------------|-----|

|     | for the given boundary conditions                                                    | 125 |

| 135 | A 2D FDTD grid                                                                       | 126 |

| 136 | The calculation of the fields in the entire grid using the E-field values in         |     |

|     | Column 1 alone                                                                       | 127 |

| 137 | A 2D FDTD grid with metallization                                                    | 127 |

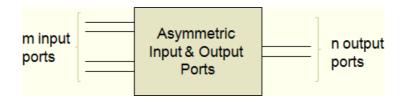

| 138 | A T-parameter matrix with asymmetric input-output ports                              | 127 |

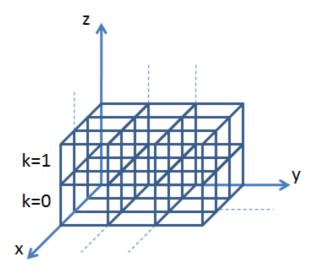

| 139 | FDTD cells in a 3D grid                                                              | 128 |

## Summary

The objective of this research work is to develop an efficient methodology for chip-package cosimulation. In the traditional design flow, the integrated circuit (IC) is first designed followed by the package design. The disadvantage of the conventional sequential design flow is that if there are problems with signal and power integrity after the integration of the IC and the package, it is expensive and time consuming to go back and change the IC layout for a different input/output (IO) pad assignment. To overcome this limitation, a concurrent design flow, where both the IC and the package are designed together, has been recommended by researchers to obtain a fast design closure. The techniques from this research work will enable multiscale cosimulation of the chip and the package making the concurrent design flow paradigm possible.

Traditional time-domain techniques, such as the finite-difference time-domain method, are limited by the Courant condition and are not suitable for chip-package cosimulation. The Courant condition gives an upper bound on the time step that can be used to obtain stable simulation results. The smaller the mesh dimension the smaller is the Courant time step. In the case of chip-package cosimulation the on-chip structures require a fine mesh, which can make the time step prohibitively small. An unconditionally stable scheme using Laguerre polynomials has been recommended for chip-package cosimulation. Prior limitations in this method have been overcome in this research work. The enhanced transient simulation scheme using Laguerre polynomials has been named SLeEC, which stands for simulation using Laguerre equivalent circuit. A full-wave EM simulator has been developed using the SLeEC methodology.

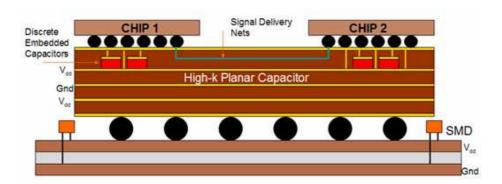

A scheme for efficient use of full-wave solver for chip-package cosimulation has been proposed. Simulation of the entire chip-package structure using a full-wave solver could be a memory and time-intensive operation. A more efficient way is to separate the chip-package structure into the chip, the package signal-delivery network, and the package power-delivery network; use a full-wave solver to simulate each of these smaller subblocks and integrate them together in the following step, before a final simulation is done on the integrated network. Examples have been presented that illustrate the technique.

#### 1 Introduction

The consumer demand for electronics products with more functionality, better performance, smaller size, less weight, and lower cost has given rise to numerous issues in signal integrity and power integrity. As more functionality is integrated in a package, there is more communication between the chips, resulting in larger number of input/output (IO) pins and more interconnects to be routed. With smaller spacing between the interconnects, there can be significant crosstalk, causing the product to fail. The endless requirement for faster speed has created smaller rise times and fall times on the order of picoseconds. This has pushed the frequency spectrum into the GHz range. Faster signaling creates voltage fluctuations on the power-distribution network that can cause false switching of logic circuits. The current in interconnects and on its return path creates regions of small and large electromagnetic (EM) fields. Chips placed at the locations of high EM field experience loss in signal quality due to EM coupling. With every next generation integrated circuit (IC), the voltage levels are scaled down to reduce power dissipation and transistor failure. As a result, the noise tolerance is becoming smaller.

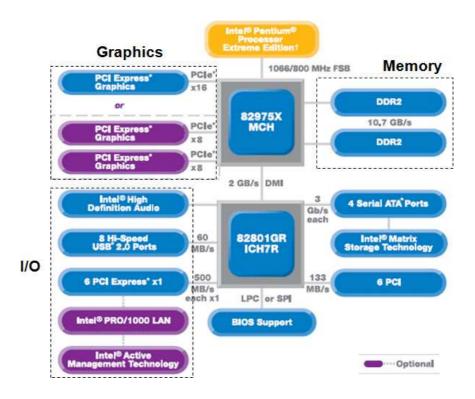

ICs making up a system, together with passive components and the power-distribution network, are interconnected together in a package. A layout of a generic Intel PC system is shown in Figure 1 [1]. The chip marked 82975X MCH, which is known as the Northbridge, is connected to the graphics, the processor and the memory chips. The chip marked 82801GR ICH7R, which is known as the Southbridge, is connected to the slower IO chips. The various ICs making up the Intel system can be efficiently organized as a multichip module, similar to the configuration shown in Figure 2. The IC and the package do not exist independently, and therefore, in order to be able to evaluate the performance of the system, cosimulation of the chip and the package is needed. For example, the noise generated on the package affect the ICs and vice versa.

According to the International Technology Roadmap for Semiconductors (ITRS) 2005 [2], one of the challenges in future packages is to develop a chip-package cosimulation tool to analyze signal integrity and power integrity. It is becoming difficult to predict failures due to the lack of tools capable of chip-package cosimulation for accurate evaluation of

Figure 1: A generic Intel PC system.

system performance. Signal and power-integrity problems have resulted in a longer design cycle time. Failures that can be detected at the simulation level rather than at the product prototype level can save cost and time. Accurate modeling methods and tools play a key role in noise prediction. With tools that perform a system-level simulation, the number of design iterations that are needed to successfully create a working prototype, can be drastically reduced. Smaller design cycle time reduces cost, as well as decreasing the time

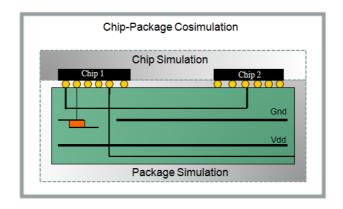

Figure 2: A multichip module.

required to deliver a product to the consumer. The objective of this research is to develop an accurate, time-efficient, and memory-efficient technique for chip-package cosimulation.

#### 1.1 Development of CAD Tools

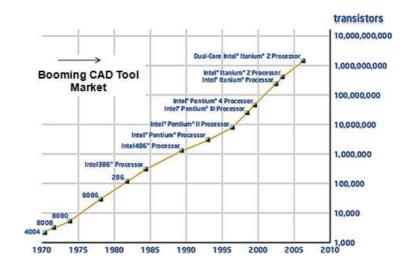

CAD tools are indispensable in the development of any electronic system for today's market. The Intel microprocessor family from the years 1970 to 2005 is shown in Figure 3 [1]. What is often neglected is the importance played by CAD tools in the progress. Initial processors contained limited number of transistors and were hand crafted. With increasing number of transistors and more integration of digital and analog, modern electronic design without the aid of CAD tools is unthinkable.

Figure 3: The Intel processor family and CAD tools.

CAD tools play different roles such as optimization of logic, automatic placement and routing of transistors, time/frequency-domain simulation for noise prediction. They reduce the product development time and help create better designs that work more efficiently. Most of the CAD tools have a certain domain where they can be applied. Some tools operate purely at the chip level, while others only at the package level. A drawback of this approach is that there is no feedback between the two. The noise generated by the parasitics of the package structures can cause the chip to fail. The objective of this thesis is to develop simulation methodologies in the time and frequency domain to enable cosimulation at the chip and the package levels.

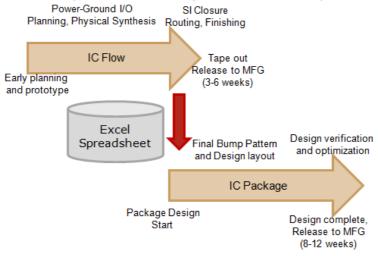

A traditional sequential design flow of an IC and a package is shown in Figure 4 [3]. In the sequential design flow, the chip is first designed followed by the package design based on the IO pad assignments of the IC. A disadvantage of this approach is that the problems that occur due to the integrated chip and the package go undetected until the final stage. The reason for using this type of design flow is because of the lack of CAD tools that are available in order to be able to design both the chip and the package in parallel.

The recommended package-aware design flow is shown in Figure 5 [3]. In this paradigm, both the package and the chip are planned concurrently to ensure signal and power-integrity closure. The advantage of this approach is that potential signal and power-integrity issues that can occur within the chip, the package, or as a result of the integrated chip and the package, are detected early in the design stage. Making changes to the design in the early stages is much easier, faster, and more cost effective. Package-aware integrated-circuit design results in a faster product turnaround time. The simulation methodologies developed in this thesis can be applied to perform chip-package cosimulation at the design stage, thereby making the package-aware design-flow possible.

The multiscale feature of the chip-package structure makes it difficult to use conventional tools for simulation. The on-chip structures require a very fine mesh, while a coarse mesh can be used for the package structures. The large variation in the mesh dimensions, as well as the fine mesh, make the simulation time and the memory requirement prohibitively large. In this thesis, an efficient simulation methodology that uses Laguerre polynomials for simulation has been developed. Several test cases have been simulated that show the advantage of using the Laguerre polynomials based scheme for multiscale simulation over the conventional methods.

# 1.2 Common Signal and Power-Integrity Problems Present in a Chip and a Package

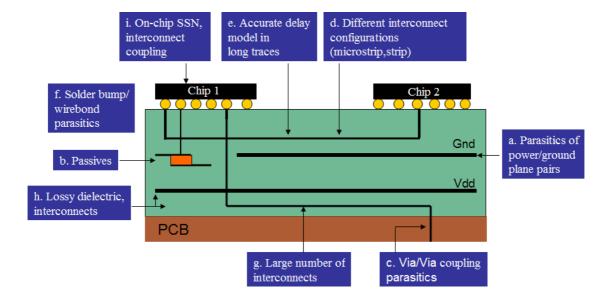

A list of some of the parasitics at the chip and the package levels is shown in Figure 6.

1. Non-ideal power-ground structures:

The transient current that is drawn by switching logic circuits from a power-ground

# Design Convergence (Traditional Sequential Timeline)

Figure 4: Traditional sequential design flow [3].

#### Design Convergence (Concurrent Design Approach) Power-Ground I/O SI Closure Early planning and prototype Planning, Physical Synthesis Routing, Finishing Tape out IC Flow Release to MFG (3-6 weeks) Net list I/O drivers constraints Design verification Techfiles Final Bump Pattern and 1st pass acceptance and Design layout SPG Ratios IC Package Package Exploration Design complete, and Optimization Release to MFG (8-12 weeks)

Figure 5: Package-aware design flow. [3].

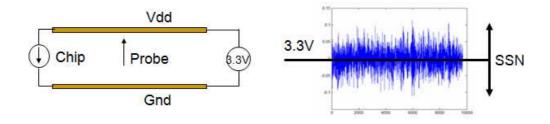

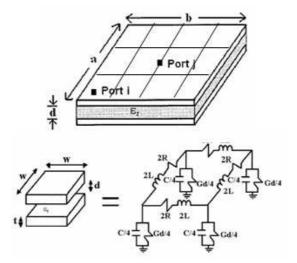

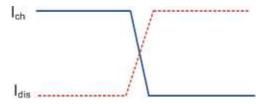

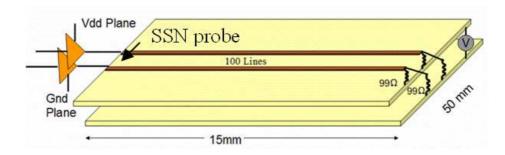

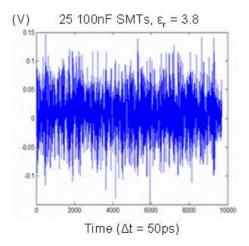

plane produces simultaneous switching noise (SSN) due to the non-ideal planes in the power-distribution network. A cross section of a power-ground plane is shown in Figure 7. The transient current drawn from a chip is modeled by a current source. An ideal voltage supply is also connected to the power-ground plane. A typical waveform at some point on the power-ground plane marked *probe* is shown in the figure. Rather than an ideal constant voltage, noise voltage on the order of hundreds of millivolts, known as simultaneous switching noise (SSN), is typically present for chips operating in the GHz range. Power-supply noise can cause problems such as false switching in logic circuits [4]. Power grids on the chip are also non ideal and increase the noise voltage [5]. On-chip and package decoupling capacitors are placed to minimize SSN [6]. Simulators should also be capable of including passive components such as capacitors, inductors and resistors, which are almost always present.

#### 2. Reflections due to imperfect terminations:

Terminations in interconnects that are not matched to their charactersitic impedances will result in problems such as ringing and reflections [4]. These reflections degrade the performance of the driver and the receiver ICs that are attached to the net.

Figure 6: Common signal and power-integrity problems present in a package.

Figure 7: Simultaneous switching noise (SSN).

#### 3. Parasitics of via, solder-bump, package leads, wirebonds:

Solder bumps, leads, and wirebonds are interfaces between the chip and the package. In addition to carrying signals between the chip and the package domains, their parasitics generate significant noise degrading the performance [7] [8]. Via parasitics are also critical to accurately estimate the noise voltage levels. The parasitics may cause reflections, which can introduce ringing in the waveform.

#### 4. Interconnect parasitics:

Interconnects are modeled using cascaded lumped elements composed of inductors (L), capacitors (C), resistors (R, G) and mutual inductance. Cascaded lumped element model for transmission lines based on R,L,G,C per unit length matrices for multiconductor transmission lines is given in [9]. The loss in the interconnects and substrate attenuate the signal as it propagates in the channel.

## 1.3 Proposed Research

The objective of the proposed research is to develop a transient simulation methodology for chip-package cosimulation. The solver should be capable of solving large practical problems; it must be fast and accurate; the techniques should be robust to model structures of different types of configurations. Based on the proposed research the following research work has been completed:

#### 1. Transient simulation using Laguerre polynomials

Transient simulation using Laguerre polynomials is unconditionally stable and therefore, has the advantage of not being limited by any time step. Laguerre FDTD has shown to be  $70-80\times$  faster than the conventional FDTD scheme. For chip-package cosimulation, the on-chip structures require a very small mesh making the time step prohibitively small for simulation using the conventional finite-difference time-domain scheme. Since Laguerre FDTD is unconditionally stable, it is ideally suited for chip-package cosimulation. Since its introduction, several modifications have been made to the algorithm. The new methodology has been named SLeEC and stands for simulation using Laguerre equivalent circuit.

#### 2. Simulation for any length of time

The limited time duration for which Laguerre FDTD could be simulated has been resolved, so that Laguerre FDTD can now be done for any length of time.

#### 3. Companion model of the FDTD grid

An equivalent circuit model of the FDTD grid has been developed, reducing the number of unknowns to be solved without the use of long cumbersome equations.

#### 4. Transient circuit simulation using Laguerre polynomials

Laguerre FDTD has been applied to circuit problems consisting of passive circuit components such as inductors with mutual inductance, resistors, and capacitors.

#### 5. Choosing the correct number of basis coefficients

Transient simulation using Laguerre polynomials requires finding the correct number of basis coefficients to accurately represent the time-domain waveform. A numerical way by which the correct number of basis functions are chosen has been proposed.

#### 6. Full-wave EM simulator using the SLeEC methodology

A 3D time-domain EM simulator that uses Laguerre polynomials for transient simulation has been developed. A variety of test cases have been simulated to demonstrate the advantage of using this tool for chip-package cosimulation.

#### 7. Obtaining frequency-domain parameters through time-domain simulation

A way by which frequency-domain parameters can be obtained from time-domain simulation has been proposed. Results show that time-domain windowing is necessary before conversion to frequency-domain parameters to obtain the right results.

#### 8. Efficient use of full-wave solvers for chip-package cosimulation

For chip-package cosimulation, rather than using a full-wave solver to simulate the entire structure, the structure can be partitioned into different blocks and a full-wave solver can be applied to each of these blocks separately. Results from each of these blocks can be integrated together to model the complete structure. The on-chip structures have been simplified to a great extent. The proposed technique has been demonstrated for package power-ground planes and package interconnects. The following tasks have been completed:

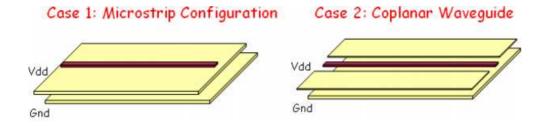

#### (a) Modeling of microstrip lines referenced to a power-ground plane

A microstrip-line configuration is shown in Figure 8. Given two-port frequency-domain parameters of a microstrip line, which has ports located at the near end and the far end of the microstrip, as well as two-port frequency parameters of the power plane, which has ports located at the near-end reference and the far-end reference of the microstrip, an admittance matrix model to integrate the interconnect and the power plane has been developed. The two-port admittance matrix model has been generalized to an N-port model that can be used to model N coupled microstrip lines referenced to a power-ground plane. To demonstrate scalability, a 64-bit bus referenced to a power-ground plane has been simulated.

#### (b) Modeling of a conductor-backed coplanar-waveguide structure

It is common for interconnects to be routed on the same layer as the power or a ground plane, by creating a slot on the plane and routing the interconnect in the slot, as shown in Figure 8. The interconnect and the power-ground plane-pair form a conductor-backed coplanar-waveguide structure. Given such a configuration, the frequency parameters of the interconnect are obtained separate from those of the power plane. The two sets of frequency parameters are integrated together using multiconductor transmission line theory. A good correlation between Sonnet<sup>®</sup> and the proposed model has been obtained over a wide bandwidth of 8GHz.

- (c) DC Analysis with frequency-domain parameters

A method has been developed to include DC sources along with frequency-domain parameters in transient cosimulation of package interconnects and package power-ground planes. Augmenting the transient simulation method to include DC operating point has been completed. A transmission line example, showing a good match with ADS® has been accomplished.

- (d) Memory optimization for linear transient simulation with current sources Memory can be reduced significantly for linear transient simulation with transient current sources. The memory complexity can be reduced from  $O(N^2)$  to O(N), where N is the number of ports in the frequency-domain parameter block.

#### 1.4 Dissertation Outline

Conventional time-domain solvers are limited by an upper bound on the time step that can be used to obtain stable and accurate simulation results. This limit in the time step, known as Courant time step, is a major bottleneck for chip-package cosimulation. With small mesh dimensions required for on-chip structures, the time step can become prohibitively small. Transient simulation using Laguerre polynomials is unconditionally stable and is not limited by the Courant time step. Prior limitations have been overcome and the enhanced methodology is called SLeEC and stands for simulation using Laguerre equivalent circuit. SLeEC can be applied to both 3D EM simulation and linear transient circuit simulation. Circuits composed of resistors, inductors (with mutual inductance), capacitors, and linear voltage/current sources can be simulated using SLeEC. Transient simulation results show excellent correlation between the proposed technique and the traditional EM/circuit

Figure 8: A microstrip and a conductor-backed coplanar-waveguide configuration.

simulators.

For chip-package cosimulation, rather than using a full-wave solver to simulate the entire structure, the structure can be partitioned into different blocks and full-wave solver can be applied to each of these blocks separately. Results from each of these blocks can be integrated together to model the complete structure. The on-chip structures have been simplified to a great extent. The proposed technique has been demonstrated for package power-ground planes and package interconnects. The methodology is memory efficient and scalable to large problems. The technique can be used for frequency-domain and time-domain simulation of package structures. Examples showing the scalability of this technique to realistic test cases are given. The technique permits the use of complex non-linear driver models in the simulation. A memory optimization technique for linear systems, which also results in faster simulation, has been proposed.

The remainder of this thesis is organized as follows: The SLeEC methodology is given in Chapters 2-6; 3D EM test cases showing good correlation between the conventional FDTD scheme and the SLeEC methodology is presented in Chapter 7; transformation from time-domain to frequency-domain parameters is given in Chapter 8, followed by efficient use of full-wave solvers for chip-package cosimulation in Chapter 9.

## 2 Transient Simulation Using Laguerre Polynomials

#### 2.1 Introduction

The finite-difference time-domain (FDTD) scheme has been a ubiquitous method for transient electromagnetic (EM) analysis [10] and circuit simulation [11]. The main drawback of FDTD is the Courant-Friedrich-Levy (CFL) condition, which will be referred to as the Courant condition, that limits the time step that can be used to obtain stable and accurate simulation results. In EM analysis, the smaller the mesh dimension, the smaller is the Courant time step [10]. In mathematical form, the Courant condition for EM simulation is

$$\Delta t < \frac{1}{v_{max}} \left( \left( \frac{1}{\Delta x} \right)^2 + \left( \frac{1}{\Delta y} \right)^2 + \left( \frac{1}{\Delta z} \right)^2 \right)^{-\frac{1}{2}},$$

(1)

where  $v_{max}$  is the maximum phase velocity of the wave propagation,  $\Delta x$ ,  $\Delta y$ , and  $\Delta z$  are the smallest mesh dimensions in the x, y, and z directions [10]. The time-step limit for numerical stability can be derived using dispersion analysis [10]. A summary of the derivation in [10] is given in the appendix in Chapter 12.

In transient circuit simulation of passives such as resistors, inductors, and capacitors, the maximum allowable time step is a function of the smallest inductor and capacitor values [12].

$$\Delta t < \sqrt{L_{min}C_{min}} \tag{2}$$

Courant-like condition for stability in the circuit domain is given in Equation 2, where  $L_{min}$  and  $C_{min}$  are the smallest inductor and capacitor values in the circuit.

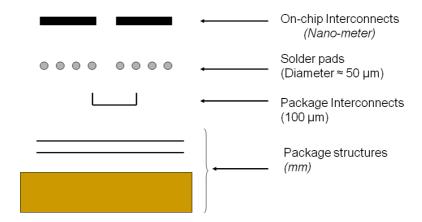

The Courant condition is a major bottleneck in using FDTD for chip-package cosimulation. Multiscale dimensions in a chip-package structure is shown in Figure 9. The on-chip structures are in the *nanometer* scale, the solder pads typically have a diameter of  $50\mu m$ , the package interconnects are in the  $100\mu m$  range, and the package structures, such as the power-ground planes, are in the mm scale. The on-chip structures that are in the nm range would require a fine mesh for simulation, making the time step prohibitively small.

An unconditionally stable implicit-FDTD scheme using Laguerre polynomials has been proposed in [13]. The method presented in [13] will be referred to as the Laguerre-FDTD scheme in the rest of this document. Laguerre FDTD is unconditionally stable and therefore,

Figure 9: Multiscale features in a chip-package structure.

the time step is not limited by the Courant condition. It has been shown in [13] that Laguerre FDTD can be  $80 - 100 \times$  faster than the conventional FDTD scheme. Since transient simulation using Laguerre polynomials is unconditionally stable, it is ideally suited for chip-package cosimulation.

The following modifications and additions to the original Laguerre-FDTD scheme in [13] have been made in this research work:

- 1. The limited time duration for which Laguerre FDTD could be simulated has been resolved, so that Laguerre FDTD can now be done for all time duration.

- 2. An equivalent circuit model, which is also known as a *companion model*, of the FDTD grid has been developed, reducing the number of unknowns to be solved without the use of long cumbersome equations.

- 3. Laguerre FDTD has also been applied in transient simulation of circuits consisting of passive circuit components, such as inductors with mutual inductance, resistors, and capacitors. The companion models for these components, which allow easier implementation, have also been developed.

- 4. In Laguerre FDTD, the time-domain source waveforms are represented in the Laguerre domain by a set of Laguerre coefficients. The source coefficients are used to solve for the unknown values in the Laguerre domain. The output of interest is converted back to the time domain from the Laguerre domain to obtain the transient waveform. To

obtain maximum accuracy, the right number of coefficients has to be used to generate the time-domain waveform. A numerical way by which the correct number of basis coefficients are chosen has been proposed.

Each of these modifications are explained in detail after the algorithm has been presented. The new and improved algorithm has been named SLeEC, which stands for simulation using Laguerre equivalent circuit.

#### 2.2 The SLeEC Alogrithm

SLeEC can be applied to linear transient circuit simulation, as well as time-domain electromagnetic simulation. In circuit simulation, SLeEC can be used in transient analysis of linear passive components such as resistors, capacitors, inductors, mutual inductance, voltage sources, and current sources. In electromagnetic simulation, SLeEC can be used for transient analysis instead of the traditional leap-frog scheme.

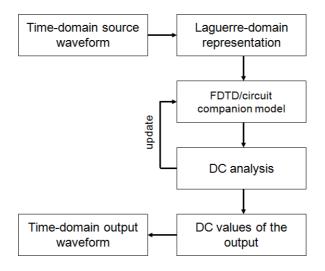

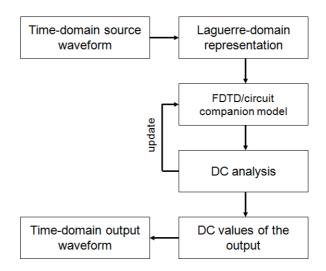

The flowchart of the SLeEC methodology is shown in Figure 10. A summary of the

Figure 10: The flowchart of the SLeEC methodology.

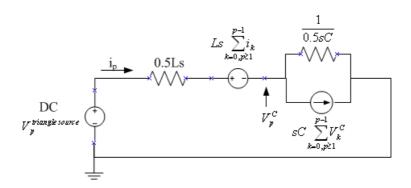

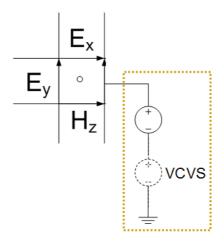

methodology is given in this paragraph, followed by a detailed explanation of each of the steps. The first step is to convert the input source waveforms from time domain to Laguerre domain. A time-domain waveform can be represented in the Laguerre domain by a set of coefficients. The next step is to replace the (1) capacitors, inductors, mutual inductance, in the

case of circuit simulation and (2) the FDTD grid, in the case of electromagnetic simulation, with their respective companion models. The companion models in the time domain for an inductor and a capacitor is given in [14]. The companion models in the Laguerre domain for the FDTD grid, resistors, capacitors, and mutual inductance are derived in this thesis. The companion models in the Laguerre domain are made up of resistors, current sources, voltage sources, and controlled sources. A DC analysis is done once for each of the basis coefficients that represents the input waveforms. Although multiple input waveforms maybe present, they can all be taken into account in a single DC analysis. At the end of each of the DC analyses the companion models are updated before the next DC analysis. The DC solution represent the Laguerre basis coefficients of its corresponding time-domain waveform. In the companion model of the FDTD grid for EM simulation, the nodal voltages are mapped to electric-field coefficients and the branch currents to magnetic-field coefficients. The final step is to convert the DC values for the output of interest to the time domain. Detailed explanation of each of these steps is given in the following subsections.

It is worth mentioning earlier that the DC values do not have to be saved at each iteration. Once the companion models are updated at the end of each iteration, there is no need to save the DC solution. Only the DC values for the output of interest needs to be saved at the end of each iteration, making the algorithm memory efficient.

#### 2.2.1 Transformation from time domain to Laguerre domain

Laguerre polynomials are defined recursively as follows [13]:

$$L_0(t) = 1, (3)$$

$$L_1(t) = 1 - t, (4)$$

$$pL_p(t) = (2p - 1 - t)L_{p-1}(t) - (p - 1)L_{p-2}(t); \text{ for } p \ge 2.$$

(5)

Laguerre polynomials satisfy the relationships

$$\int_0^\infty \varphi_u(\bar{t})\varphi_v(\bar{t})d\bar{t} = \delta_{uv},\tag{6}$$

$$\varphi_u(\bar{t}) = e^{-\bar{t}/2} L_u(\bar{t}), \tag{7}$$

$$\bar{t} = s \cdot t. \tag{8}$$

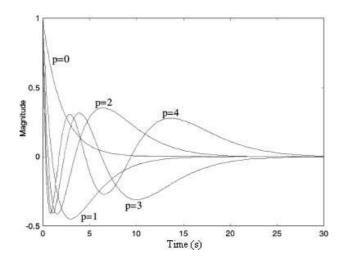

In Equations 6 - 7,  $\bar{t}$  is the real time multiplied by a scaling factor s, as shown in Equation 8. The actual time scale for which the simulation is run is very small. To make the basis function work, the real time is multiplied by s to scale the magnitude to the order of seconds.  $\varphi(\bar{t})$  is Laguerre polynomial L weighted by the exponential function  $e^{-\bar{t}/2}$ , as given in Equation 7. A Laguerre polynomial weighted by the exponential function satisfies the orthonormal property of basis functions given in Equation 6.  $\delta_{uv}$  in Equation 6 is the Kronecker delta function. The weighted Laguerre polynomials for orders p = 0 to p = 4 are shown in Figure 11 [13].

Figure 11: Weighted Laguerre polynomials for orders p = 0 to p = 4.

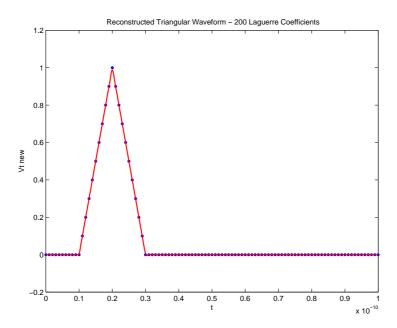

A triangular waveform with a rise/fall time of 10 ps, and a delay of 10 ps is shown in Figure 12. The triangular waveform, W(t), can be represented as a sum of weighted Laguerre polynomials as

$$W(t) = \sum_{p=1}^{p=N} W_p \varphi_p(\bar{t}). \tag{9}$$

In Equation 9,  $W_p$  represents the  $p^{th}$  coefficient of the  $p^{th}$  basis function  $\varphi_p$ .  $W_p$  can be obtained using the orthonormal property of basis functions and is given in Equation 10.

$$W_p = \int_0^\infty W(t)\varphi_p(\bar{t})d\bar{t} \tag{10}$$

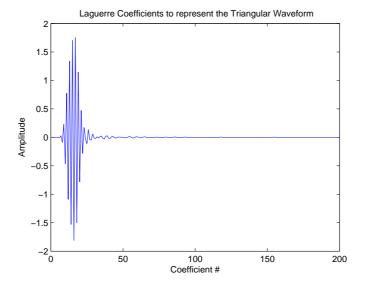

The dotted curve in Figure 12 is the original triangular waveform and the solid curve is the waveform reconstructed using 200 coefficients of the Laguerre basis functions. The two waveforms in Figure 12 are indistinguishable. The first 200 coefficients of the basis functions are shown in Figure 13. The scaling factor used to construct the waveform is  $s = 3.0 \times 10^{12}$ .

#### 2.2.2 Companion Models

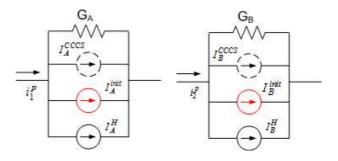

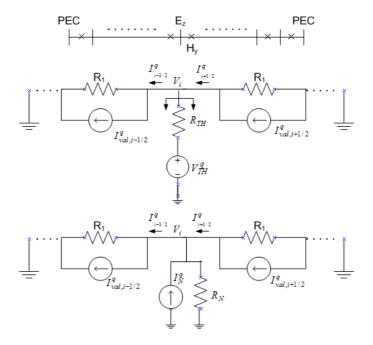

The second step is to replace the FDTD grid, or the passive components in the case of circuit simulation, with their respective Laguerre companion models. SLeEC requires solving a system of linear equations of the form Ax = b to obtain the unknown  $p^{th}$  Laguerre basis coefficients. These equivalent circuit models enable the use of stamp rule in modified nodal analysis to set up and solve the matrix, thereby making the implementation easier [14]. The popular Spice simulator uses modified nodal analysis for simulation. Therefore SLeEC can be seamlessly integrated with Spice to do transient circuit/EM simulation using Laguerre polynomials. In addition, as explained in Chapter 5, the companion models help reduce the dimension of the matrix to be solved without the use of long and cumbersome equations.

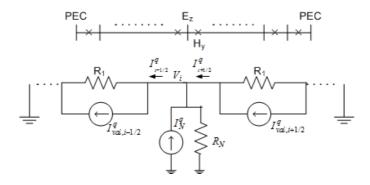

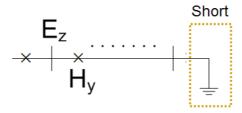

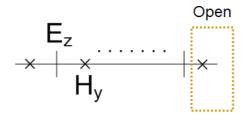

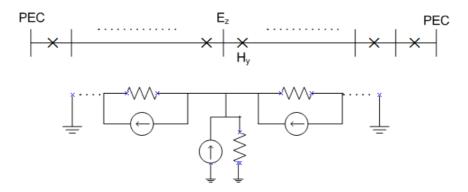

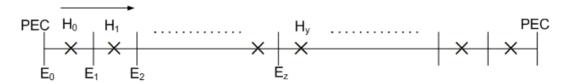

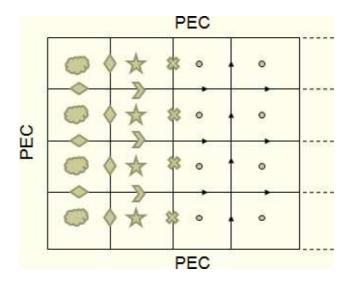

Companion models are composed of resistors, independent and dependent voltage/current sources. Detailed derivation of the models for circuit/EM simulation are given in Chapter 4 and Chapter 5. As a preview, the companion model for a 1D FDTD grid is shown in Figure 14. Vertical bars in the grid represent  $E_z$  fields and  $\times$  represent  $H_y$  fields. The grid is terminated using the perfect electric conductor (PEC) boundary condition. Nodal voltages represent the  $E_z$  fields and branch currents represent the  $H_y$  fields. The PEC boundary condition can be represented in the companion model by a short circuit, as shown in the figure.

#### 2.2.3 DC Analysis

To obtain the  $p^{th}$  Laguerre basis coefficients of the unknown values, a DC analysis is done once on the companion circuit model. The DC solution represent the Laguerre basis coefficients of their corresponding time-domain waveform. At the end of the DC analysis, the solution is used to update the companion model before solving for the  $(p+1)^{th}$  basis coefficients. The two-step process of updating the companion model and solving the matrix is repeated until enough coefficients have been obtained to accurately represent the time-domain waveform for the output of interest.

Figure 12: The original (dots) and reconstructed (solid) triangular waveform using Laguerre basis functions.

Figure 13: The coefficients of basis functions for the triangular waveform in Figure 12.

Figure 14: The companion model for a unit cell in a 1D FDTD grid.

Two important points to be noted are (1) There is no need to save the entire DC solution at every iteration. Once the companion model is updated, there is no need to store the DC solution for the next iteration. Only the coefficients for the output of interest need to be saved. (2) The A matrix when solving Ax = b stays constant throughout the iterations. Only the b matrix is updated at every iteration. Therefore, LU decomposition for solving Ax = b needs to be done only once.

#### 2.2.4 Transformation from Laguerre domain to time domain

The final step is to convert the Laguerre-domain coefficients to time domain for the output of interest. This is done using Equation 9. In order to maximize the accuracy, the right number of basis coefficients must be used to generate the time-domain waveform. The methodology for choosing the correct number of basis coefficients is given in Chapter 6.

#### 2.3 Advantages of Laguerre Polynomials

There are several reasons why Laguerre polynomials is attractive over other orthogonal polynomials:

- 1. Transient simulation using Laguerre polynomials is unconditionally stable.

- 2. Laguerre polynomials allows a simple method for choosing the correct number of basis coefficients to obtain maximum accuracy when generating its corresponding time-domain waveform.

- 3. When solving for N Laguerre basis coefficients  $\{W_0, W_1, \dots, W_{N-1}\}$ , the dimension of the matrix to be solved is independent of N.

- 4. Although a matrix of the form Ax = b is solved to obtain the  $p^{th}$  Laguerre basis coefficients, the A matrix is independent of p and LU-decomposition has to be done only once when solving for the N coefficients  $\{W_0, W_1, \ldots, W_p, \ldots, W_{N-1}\}$ .

- 5. There is no need to save the DC solution at every iteration. Once the companion model is updated, there is no need to store the DC solution for the next iteration. Only the coefficients for the output of interest need to be saved. In this respect, Laguerre polynomials makes the algorithm memory efficient.

- 6. And most important of all, it works well. A good correlation has been obtained with FDTD for all of the test cases that have been simulated.

## 2.4 Summary

Transient simulation using Laguerre polynomials is unconditionally stable. The Laguerre-FDTD scheme was proposed in [13]. Several modifications to the Laguerre-FDTD scheme have been made in this research work. The improved simulation methodology has been named SLeEC, which stands for simulation using Laguerre equivalent circuit.

# 3 Simulation For Any Length of Time

### 3.1 Introduction

A major drawback of the Laguerre-FDTD methodology in [13] is that the transient simulation can be performed only for a limited time duration and cannot be done for all time. There are two reasons for this limitation: the first reason is the nature of the Laguerre basis functions and the second reason is the finite precision of the computer making it impossible to represent very large numbers or very small numbers. Elaborate explanations of the reasons for the limitation will be followed by a solution that allows simulation for all time duration.

The first reason for the limitation is due to the nature of the basis functions. The Laguerre basis functions for order p = 0-4 are plotted in Figure 11. As shown in the figure, the basis functions approach 0 as t tends to  $\infty$ . Therefore, any time-domain waveform that is spanned by these set of basis functions also goes to 0 as t tends to  $\infty$ . Structures that are lossless or have a low loss cannot be simulated accurately because the fields can be nonzero for a long period of time.

The second reason for the limitation is the finite precision of the computer. A Laguerre basis function of order p is an exponentially decaying function multiplied by the  $p^{th}$  Laguerre polynomial. The exponential function quickly decays to 0 and beyond a certain time the exponential function is treated exactly as 0. Laguerre polynomials become very large with increasing time. Beyond a certain time, the numbers become very large to be represented with the limitation of finite precision and is represented as Inf in the IEEE 754 floating-point standard. Consequently, beyond a certain time point, the basis function is represented as  $0 \times Inf$  or NaN, not a number.

## 3.2 An Example to Demonstrate the Limitation

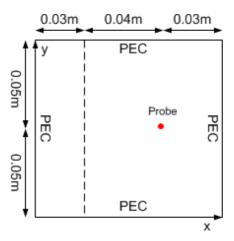

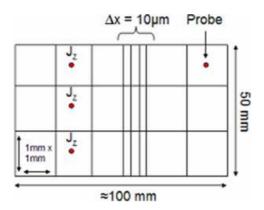

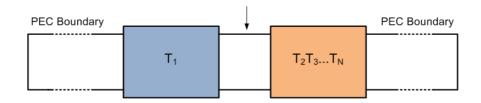

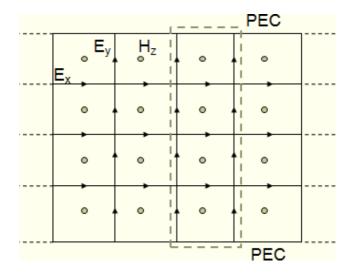

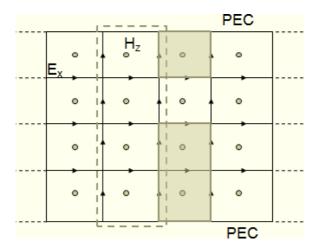

An example where Laguerre FDTD is unable to capture the transient response beyond some time is presented in this paragraph. A lossless resonant cavity containing the fields  $E_x$ ,  $E_y$ , and  $H_z$  that is terminated with PEC boundary is shown in Figure 15. A modulated

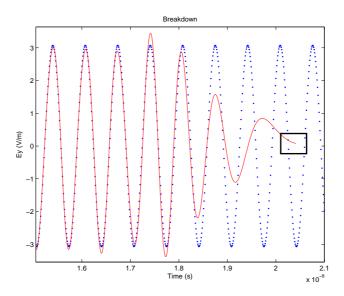

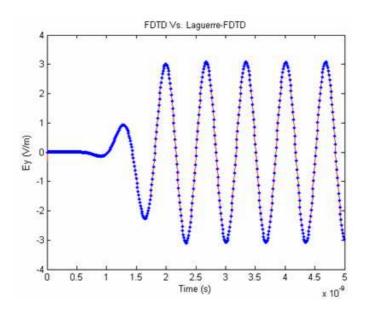

Gaussian source waveform with the same parameters as [13] is used as the  $J_y$  current source and is placed along the vertical dashed line in Figure 15. The number of cells used to mesh the structure is  $10 \times 10$ . The  $E_y$  field at the location marked probe between 15ns and 21ns is plotted in Figure 16. Theoretically, since the cavity is lossless, the fields must never decay to 0. The solid waveform has been obtained using the Laguerre-FDTD scheme and the dots by the conventional FDTD scheme. Since the basis functions go to 0 as t tends to  $\infty$ , the solid waveform starts to decay to 0, as shown in the figure. The abrupt termination of the solid waveform, which is indicated by the box, occurs due to the limitation of finite precision, as explained in the previous paragraph.

Figure 15: A 2D box with PEC boundary.

### 3.3 A Solution to Overcome the Limitation

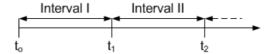

The solution to overcome this limitation is to divide the total simulation time into different intervals. Let Interval I span from time  $t = t_0$  to  $t = t_1$ , Interval II span from time  $t = t_1$  to  $t = t_2$ , and so on, as shown in Figure 17. The length of each interval is chosen such that simulation can be accurately performed in that time duration. The final values at the end of Interval i are used as initial conditions to simulate in Interval (i + 1). This process is repeated until the time duration for which the simulation needs to be done is completed. The companion models for circuit simulation and EM FDTD simulation, which will be presented in Chapters 4 and 5, include initial conditions to enable restarting a

Figure 16: The transient simulation response from 15ns to 20ns. Solid: the Laguerre-FDTD scheme and Dots: FDTD

Figure 17: The total simulation time is divided into different intervals.

simulation. The differential equations that describe the transient behavior of a system have been modified to explicitly include initial conditions that will permit simulation for all time duration. The SLeEC algorithm that is presented in Chapter 2.2 is applied in each of the time intervals.

It must be noted that Laguerre-MNA does not require storing all nodal voltages and all branch currents from the series of DC analysis that has been performed. At the end of each DC analysis, once the companion models have been updated, there is no need for saving the solution. The only solution that needs to be stored at the end of each DC analysis is the solution of the output for which the transient waveform is to be observed, which is a constant amount of memory.

## 3.4 Computing the Final Values at the End of an Interval

The final values at the end of an interval, e.g. Interval i, must be computed in order to use these values as the initial conditions in the next time interval, Interval (i+1). For example, the initial condition for a capacitor is the initial voltage across the capacitor and the initial condition for an inductor is the initial current through the inductor. Not all the coefficients, i.e. the DC solution for the voltage across a capacitor and the current through an inductor need to be saved to compute the final value at the end of a time interval. At the end of each DC analysis, the contribution of  $p^{th}$  Laguerre basis coefficient  $(W_p)$  to the final value of the transient waveform at the end of a time-interval  $(t_f)$  can be computed by using Equation 11.

$$value(t_f) = value(t_f) + W_p \varphi_p(st_f)$$

(11)

$value(t_f)$  is first initialized to 0, before using Equation 11. By using Equation 11, the coefficients of the DC solution need not be saved in order to compute the final value of a quantity at the end of a time-interval.

## 3.5 Examples of Simulation Using Initial Conditions

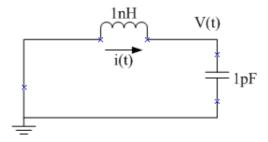

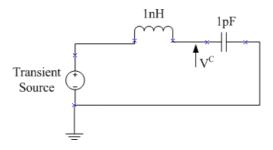

An LC circuit is shown in Figure 18. The values for L and C are 1nH and 1pF, respectively.

Figure 18: The circuit for transient simulation with initial conditions.

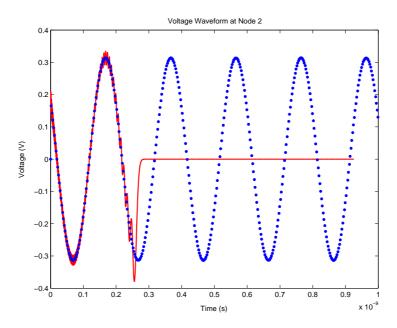

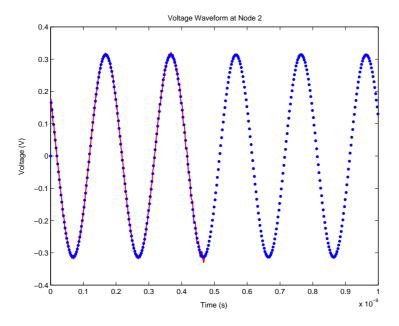

The initial conditions are the voltage across a capacitor and the current through an inductor at time t = 0. The initial current through the inductor, i(0), is -8.12 mA and the initial voltage across the capacitor, V(0), is 0.18 V. The transient simulation waveforms of V(t) generated using 200 Laguerre basis coefficients and 400 coefficients are shown in Figure 19

and Figure 20, respectively. Note the abrupt termination of the waveform around 0.5ns in Figure 20. Simulation beyond this time requires restarting the simulation again with the new initial conditions.

As a second example, for the structure shown in Figure 15, the simulation time of 7.5ns is divided into two intervals, 5ns and 1.5ns.  $E_y(t)$  at the location marked probe in Figure 15 for Interval I is shown in Figure 21. The solid line has been obtained using SLeEC and the dots is from the conventional FDTD scheme. The time-scale factor used in Interval I is  $s = 7.0 \times 10^{10}$ . The final values of the fields at the end of Interval I are used as initial conditions for simulation in Interval II. The transient waveform for Interval II is plotted in Figure 22. The value of the time-scale factor used for the smaller Interval II is  $s = 7.56 \times 10^{11}$ . The number of basis coefficients used is 400 for Intervals I and II.

## 3.6 Summary

The Laguerre-FDTD scheme proposed in [13] has the bottleneck of being able to simulate only for a limited time duration. This limitation has been overcome in SLeEC. The total simulation time is divided into different intervals. At the end of an interval, the simulation is restarted using the final values in the previous interval as initial conditions.

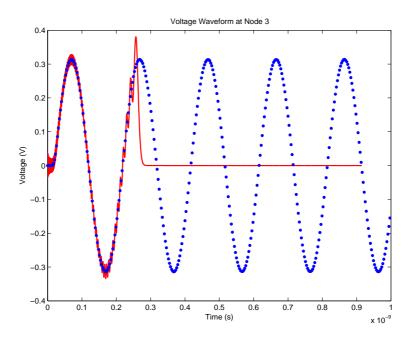

Figure 19: The voltage across the capacitor V(t) with initial conditions (200 basis coefficients). Dots: WinSpice and Solid: SLeEC

Figure 20: The voltage across the capacitor V(t) with initial conditions (400 basis coefficients). Dots: WinSpice and Solid: SLeEC

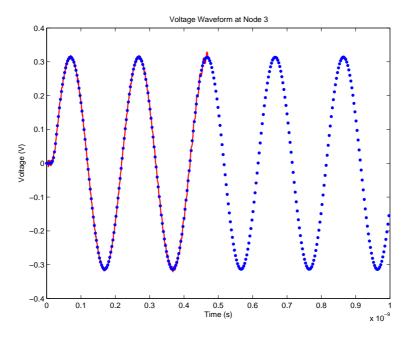

Figure 21: The simulation results from 0ns to 5ns. Solid: SLeEC and Dots: FDTD

Figure 22: The simulation results from 5ns to 6.5ns using new interval length and time-scale factor. Solid: SLeEC and Dots: FDTD

# 4 Companion Models for Circuit Simulation

### 4.1 Introduction

SLeEC can be used for linear transient simulation of circuits made up of inductors with mutual inductance, capacitors, and resistors. The advantage of SLeEC is the unconditional stability by which significant speed up can be obtained over the conventional time-domain schemes that are limited by the Courant condition. In the second step of the SLeEC algorithm, shown in Figure 10, the circuit components are replaced by their respective Laguerre-domain companion models. Companion models for an inductor, capacitor, and mutual inductance are derived in Chapters 4.2, 4.3, and 4.5.

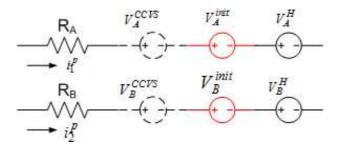

## 4.2 The Companion Model of an Inductor

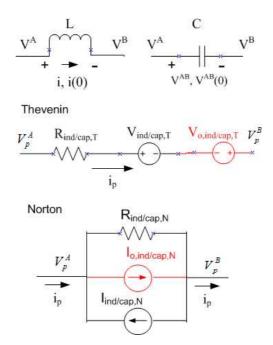

The Thevenin and Norton forms of the companion model for an inductor of value L is shown in Figure 23. The *structure* of the companion models are the same for both an inductor as well as a capacitor. The current through the inductor at time t is i(t). The initial current

Figure 23: The Thevenin and Norton forms of the companion model for an inductor or a capacitor.

through the inductor is i(0) and the direction of the current flow is marked by the arrows shown in the figure. The voltages at Node A and Node B are  $V^A(t)$  and  $V^B(t)$ , respectively.  $V_p^A$  and  $V_p^B$  represent the  $p^{th}$  basis coefficients of the voltages  $V^A(t)$  and  $V^B(t)$ , respectively. The  $p^{th}$  basis coefficient of the branch current i is marked as  $i_p$ .

In the Thevenin form, an inductor is replaced by a resistor in series with two voltage sources. The voltage source marked  $V_{o,ind/cap,T}$  is a function of the initial current through the inductor and represents the initial condition. The value of the series resistor is

$$R_{ind,T} = 0.5Ls, (12)$$

where s is the time-scale factor and the subscript T stands for Thevenin. The value of the first voltage source is a function of the previous DC results of the branch currents. The value of the first voltage source is

$$V_{ind,T} = Ls \sum_{k=0, p \ge 1}^{p-1} i_k.$$

(13)

In the first DC analysis that is done for p = 0,  $V_{ind,T}$  is set to 0. The value of the second voltage source is

$$V_{o,ind,T} = Lsi(0). (14)$$

The rest of the chapter presents the mathematical derivation of the companion model.

The voltage across the inductor is given by

$$V^A - V^B = L\frac{di}{dt} - Li(0)\delta(t). \tag{15}$$

The time varying current and voltages, i,  $V^A$ , and  $V^B$ , can be written as a sum of Laguerre basis functions as

$$i = \sum_{q=0}^{\infty} i_q \varphi_q(\bar{t}) \tag{16}$$

$$V^A = \sum_{q=0}^{\infty} V_q^A \varphi_q(\bar{t}) \tag{17}$$

$$V^{B} = \sum_{q=0}^{\infty} V_{q}^{B} \varphi_{q}(\bar{t}) \tag{18}$$

The variables  $i_q$ ,  $V_q^A$ , and  $V_q^B$  are the  $q^{th}$  basis coefficients of the current and voltages.  $\varphi_q$  is the  $q^{th}$  basis function defined in Equation 7 and  $\bar{t}$  is the scaled time defined in Equation 8. The time derivative of U can be written in the Laguerre domain as [13]

$$\frac{dU}{dt} = \frac{d}{dt} \left( \sum_{q=0}^{\infty} U_q \varphi_q(\bar{t}) \right)$$

$$= s \sum_{q=0}^{\infty} \left( 0.5U_q + \sum_{k=0,q>1}^{q-1} U_k \right) \varphi_q(\bar{t}). \tag{19}$$

Substituting Equations 16-18 in Equation 15 and using the time-derivative relationship in Equation 19, Equation 20 can be obtained.

$$\sum_{q=0}^{\infty} V_q^A \varphi_q(\bar{t}) - \sum_{q=0}^{\infty} V_q^B \varphi_q(\bar{t}) = Ls \sum_{q=0}^{\infty} \left( 0.5i_q + \sum_{k=0,q>1}^{q-1} i_k \right) \varphi_q(\bar{t}) - Li(0)\delta(t)$$

(20)

Multiplying Equation 20 by  $\varphi_p(\bar{t})$ , integrating over time  $[0, \infty]$ , and using the orthonormal property of basis functions given in Equation 6, Equation 21 can be obtained.

$$V_p^A - V_p^B = Ls \left( 0.5i_p + \sum_{k=0, p \ge 1}^{p-1} i_k \right) - Lsi(0)$$

(21)

In deriving Equation 21, Equation 22 is used when integrating the delta function term.

$$\int_{0}^{\infty} \delta(t)\varphi_{p}(\bar{t})d\bar{t} = s\varphi_{p}(0) = s \tag{22}$$

Equation 21 can be represented in the Thevenin form by a resistor in series with two voltage sources with the values given in Equations 12-14.

Equation 21 can be rearranged to obtain a Norton representation. Solving for  $i_p$  in Equation 21, Equation 23 can be obtained.

$$i_p = 2i(0) + \frac{1}{0.5Ls}(V_p^A - V_p^B) - 2\sum_{k=0, p \ge 1}^{p-1} i_k$$

(23)